VHDL实验:2选1多路选择器与数字逻辑组件实现

"该文档包含了四个VHDL实验的结果,分别是2选1多路选择器、D触发器、半加器和全加器的设计。实验代码基于IEEE库中的STD_LOGIC_1164标准,用于描述数字逻辑系统的行为。"

在VHDL中,这些实验展示了基本的数字逻辑组件的建模方法。以下是每个实验的详细概述:

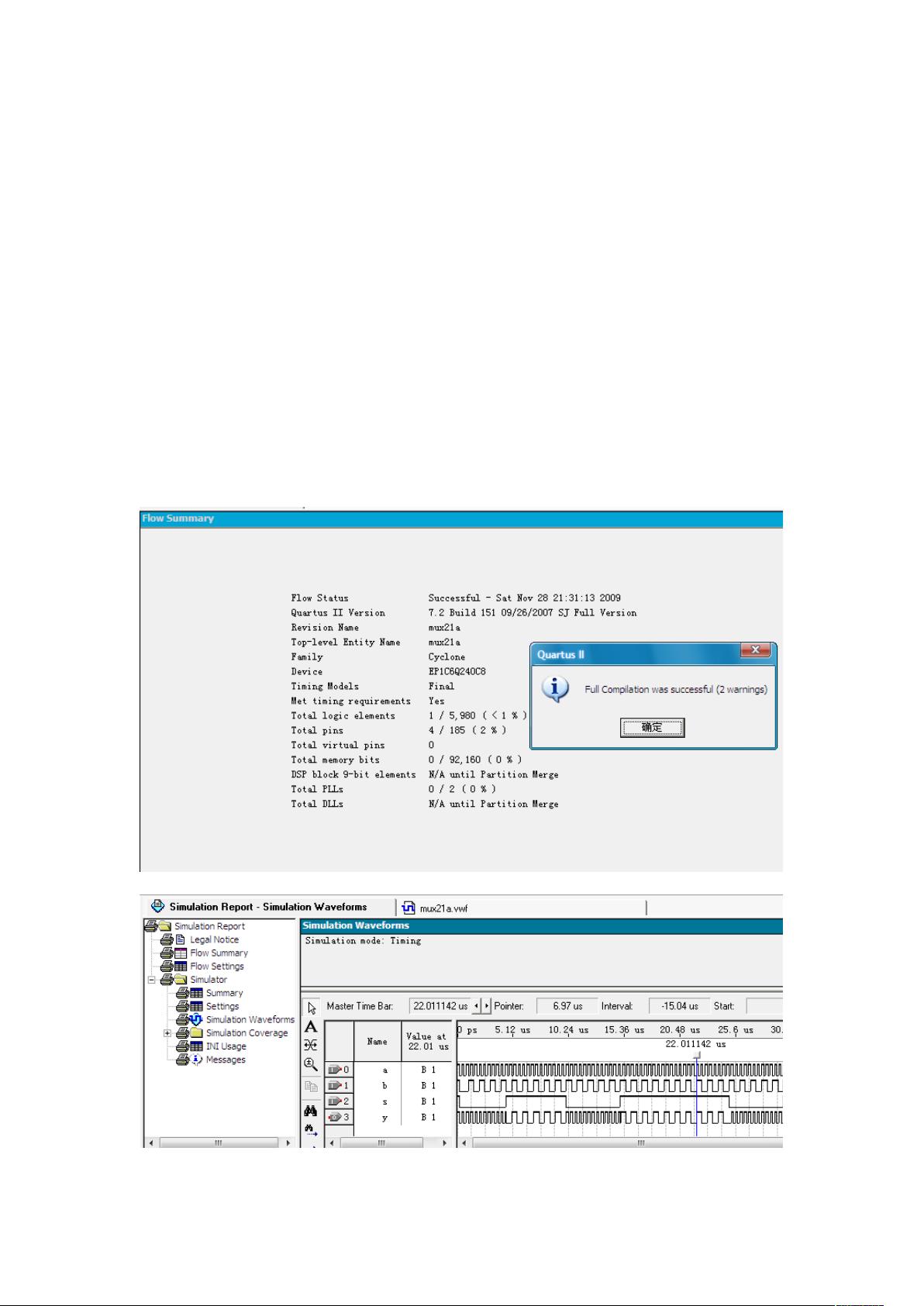

1. **2选1多路选择器 (MUX21a)**:

这个实验设计了一个简单的2选1多路选择器,其功能是根据输入信号`s`来选择`a`或`b`作为输出`y`。在VHDL中,这个设备被定义为一个实体`mux21a`,它有四个端口:两个输入`a`和`b`,一个选择输入`s`,以及一个输出`y`。实体的架构中包含一个进程,该进程根据`s`的值决定`y`的赋值。

2. **D触发器**:

D触发器是一种边沿触发的存储元件,它的输出在时钟边沿时更新为数据输入(D)的当前值。实验中的代码没有给出,但通常会包括一个进程,其中时钟信号`clk`是敏感项,而`d`是数据输入,`q`是输出,可能还有一个清除或预置输入。

3. **半加器 (Half Adder)**:

半加器实现了两个位的加法,不考虑进位。在VHDL中,半加器`h_adder`有两个输入`a`和`b`,以及两个输出:进位`co`和和`s`(`so`)。和`s`是`a`和`b`的异或,进位`co`是`a`和`b`的与。这个设计中,异或和与操作是通过布尔表达式完成的。

4. **全加器 (Full Adder)**:

全加器在半加器的基础上增加了对前一位进位的处理。虽然实验代码中似乎重复了半加器的代码,但全加器通常会有一个额外的输入`ci`(进位输入),并且其`co`(进位输出)不仅取决于`a`和`b`,还取决于`ci`。全加器可以将三个位加在一起,并考虑进位。

以上实验是VHDL学习的基础,它们帮助理解如何用硬件描述语言来表示和模拟数字逻辑电路。通过这些实验,学生可以学习到VHDL的基本语法,如实体、架构、过程、条件语句和逻辑运算符,并掌握数字逻辑设计的基本原理。

点击了解资源详情

262 浏览量

点击了解资源详情

113 浏览量

2021-10-10 上传

454 浏览量

258 浏览量

2021-09-19 上传

134 浏览量

TonyXQQ

- 粉丝: 11

- 资源: 27