"阵列乘法器设计与实现-计算机组成原理课程设计"

版权申诉

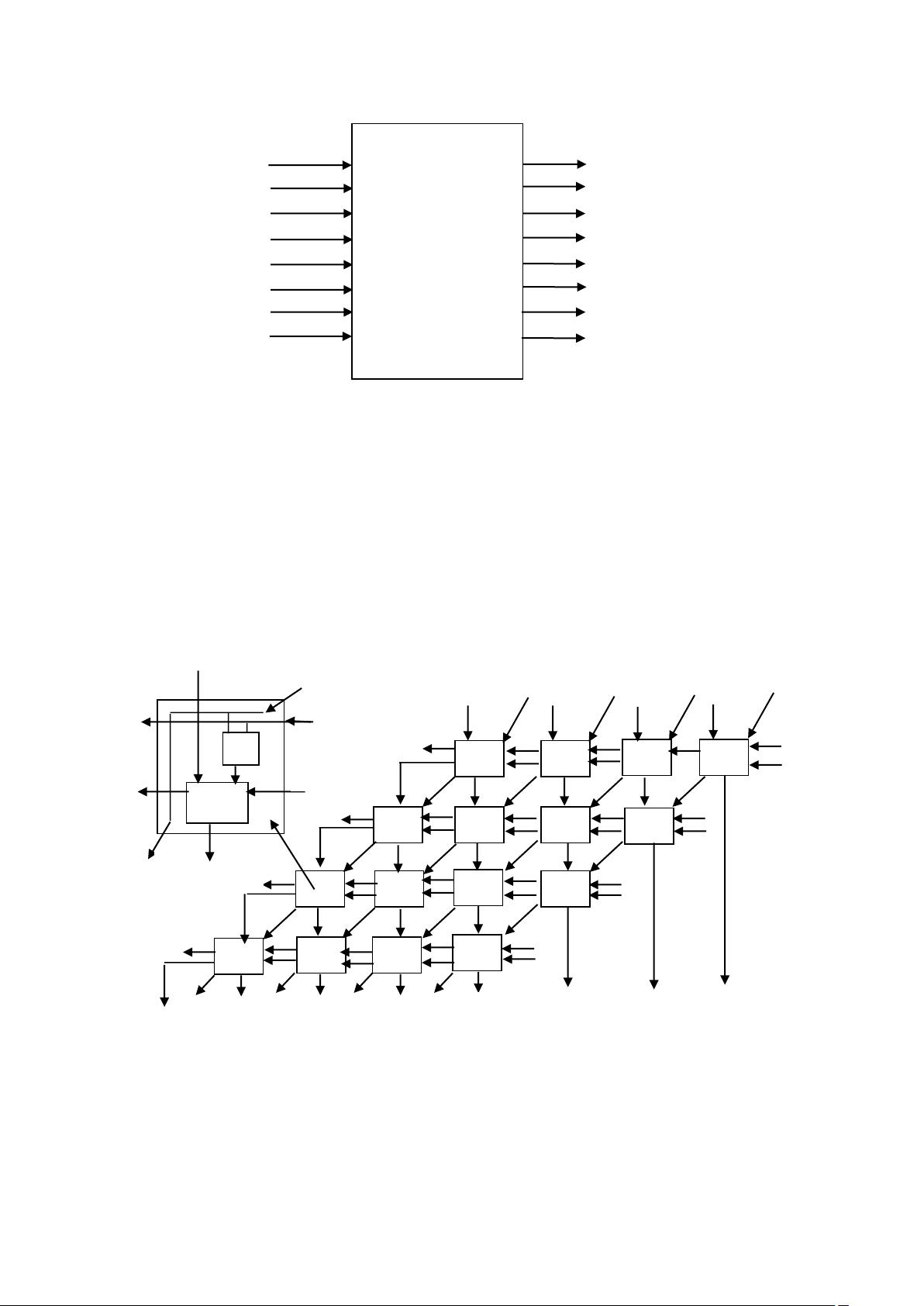

。X1依次表示乘数A的各位二进制数,Y1依次表示被乘数B的各位二进制数,而Z1到Z8分别表示加法器的部分积结果。通过对阵列乘法器的设计与实现,可以实现快速高效的乘法运算,提高了计算机系统的整体性能。

1.2 设计思路

阵列乘法器的设计思路是基于人工计算方法和二进制乘法的原理,通过逐位相乘并相加的方式得到最终的乘积。在设计阵列乘法器时,需要考虑到乘数和被乘数的位数、部分积的存储、进位的处理等关键问题。通过分析乘法运算的逻辑过程,可以确定阵列乘法器的整体设计思路,并将其转化为硬件电路的设计与实现。

1.3 设计环境

在设计阵列乘法器时,需要选择合适的设计环境,包括硬件描述语言、综合工具、逻辑综合工具等。在本课程设计中,我们选择了Verilog硬件描述语言进行阵列乘法器的设计,并使用综合工具进行电路的综合和适配,以及进行硬件测试。

第2章 详细设计方案

2.1 总体方案的设计与实现

在本章节中,我们将针对阵列乘法器的总体设计进行详细的讲解。首先介绍了总体方案的设计思路和逻辑图,然后对器件的选择与引脚锁定做了详细的说明,最后介绍了编译、综合、适配等过程。

2.1.1 总体方案的逻辑图

本课程设计中,我们设计的阵列乘法器总体方案的逻辑图如图2.1所示。逻辑图清晰地展现了乘数和被乘数的逐位相乘并相加的过程,以及部分积和最终乘积的计算流程。通过该逻辑图,可以直观地了解阵列乘法器的工作原理和电路结构。

2.1.2 器件的选择与引脚锁定

在阵列乘法器的详细设计中,我们选择了适合的逻辑门、触发器、加法器等器件,并进行了引脚的锁定。通过合理的器件选择和引脚锁定,可以保证阵列乘法器的电路设计符合实际的硬件电路实现要求。

2.1.3 编译、综合、适配

在阵列乘法器的设计过程中,我们使用了综合工具对电路进行了综合,并进行了适配以适应特定的硬件平台和实际的运行环境。通过编译、综合、适配等过程,可以验证和优化电路设计,提高阵列乘法器的性能和可靠性。

2.2 功能模块的设计与实现

在第2章中,我们详细讨论了阵列乘法器的功能模块设计与实现,包括一位全加器的设计与实现、4位输入端加法器的设计与实现以及阵列乘法器的设计与实现等内容。这些功能模块是阵列乘法器电路设计的核心,通过精心设计和实现,可以实现高效快速的乘法运算。

2.2.1 一位全加器的设计与实现

一位全加器是阵列乘法器电路设计中的基础模块,它用于实现二进制的加法运算。在本课程设计中,我们详细介绍了一位全加器的设计思路和逻辑电路实现,包括输入信号的处理、逻辑门的选择和连接、以及进位信号的处理等内容。

2.2.2 4位输入端加法器的设计与实现

4位输入端加法器是阵列乘法器电路设计的重要功能模块,它用于实现四位二进制数的加法运算。在本课程设计中,我们给出了4位输入端加法器的详细设计方案和逻辑电路实现,包括数据输入的处理、逻辑门的连接、进位信号的处理等内容。

2.2.3 阵列乘法器的设计与实现

阵列乘法器是本课程设计的核心内容,它采用了类似人工计算的方法进行乘法运算,并通过大规模的阵列结构来实现高效快速的乘法运算。在本章节中,我们详细介绍了阵列乘法器的设计思路和逻辑电路实现,包括乘数和被乘数的逐位相乘、部分积的存储和累加、以及最终乘积的输出等内容。

第3章 硬件测试

在第3章中,我们介绍了阵列乘法器的编程下载、硬件测试及结果分析等内容。通过对阵列乘法器进行硬件测试,并分析测试结果,可以验证阵列乘法器设计的正确性和可靠性,为进一步的优化和改进提供参考。

3.1 编程下载

在硬件测试的准备阶段,我们对阵列乘法器的设计进行编程下载,将其加载到特定的硬件平台上进行测试。通过编程下载,可以将阵列乘法器的逻辑电路转化为实际的硬件电路,并进行功能测试和性能评估。

3.2 硬件测试及结果分析

在硬件测试阶段,我们对阵列乘法器进行了功能测试和性能评估,获取了实际的运行结果并进行了结果分析。通过硬件测试及结果分析,可以验证阵列乘法器的设计是否符合预期的功能和性能要求,发现和解决可能存在的问题,为最终的设计优化提供参考依据。

通过本课程设计,我们深入学习了计算机组成原理的相关知识,并实际设计了阵列乘法器的硬件电路。通过阵列乘法器的设计与实现,我们加深了对计算机系统组成原理的理解,提高了解决实际问题的能力和实践能力。同时,通过硬件测试及结果分析,我们验证了阵列乘法器设计的正确性和可靠性,为今后的研究和开发工作奠定了基础。

2023-05-25 上传

2021-10-11 上传

2021-10-03 上传

2021-12-20 上传

小虾仁芜湖

- 粉丝: 113

- 资源: 9354

最新资源

- 单片机考试复习课,老师考前资料

- SQL语言实用操作全集

- latex符号表 The Comprehensive LATEX Symbol List

- Bjarne.Stroustrup.The.C++.Programming.Language.Third.Edition

- JAVA面试题解惑系列1-11

- How to Solve It:A New Aspect of Mathematical Method(Polya.G.).pdf

- masm的ml.exe错误信息中文对照

- ubb正则表达式学习资料

- board.c详细分析

- new—U-boot解析

- 五轴头回转中心的几何误差检测与补偿.PDF

- Keil uVision2软件中文入门教程

- 保护电脑完全攻略保护电脑完全攻略

- BootLoader 与Linux 内核的参数传递

- C++写好代码的十个秘诀

- ArcIMS+轻松入门