高速数据传输:LVDS接口设计与实现

180 浏览量

更新于2024-06-23

收藏 1.43MB DOC 举报

"远程数据传输中并行转串行LVDS接口设计说明书"

本文档详细介绍了在远程数据传输中采用并行转串行LVDS接口的设计方案,旨在解决高速数据传输的需求。LVDS(低压差分信号)作为一种高效能的接口技术,因其低电压、低功耗和高速传输特性,已经成为现代通信系统中的重要组成部分。

1.1 课题研究背景和意义

随着数字信号处理技术的进步,高速数据处理和传输的需求日益增长。传统的并行I/O接口在面对高速微处理器、多媒体、光传输连接等应用时,其带宽和传输效率已无法满足需求。因此,开发新的接口技术,如LVDS,对于解决高速数据传输的瓶颈至关重要。

1.3 LVDS简介

LVDS是一种低电压差分信号技术,通过发送和接收端之间的小幅电压差来传输数据,具有高速、低噪声、低功耗的特性。这种技术在减少电磁干扰的同时,提高了信号传输的可靠性,特别适用于高数据速率的应用。

1.5 本课题研究内容和安排

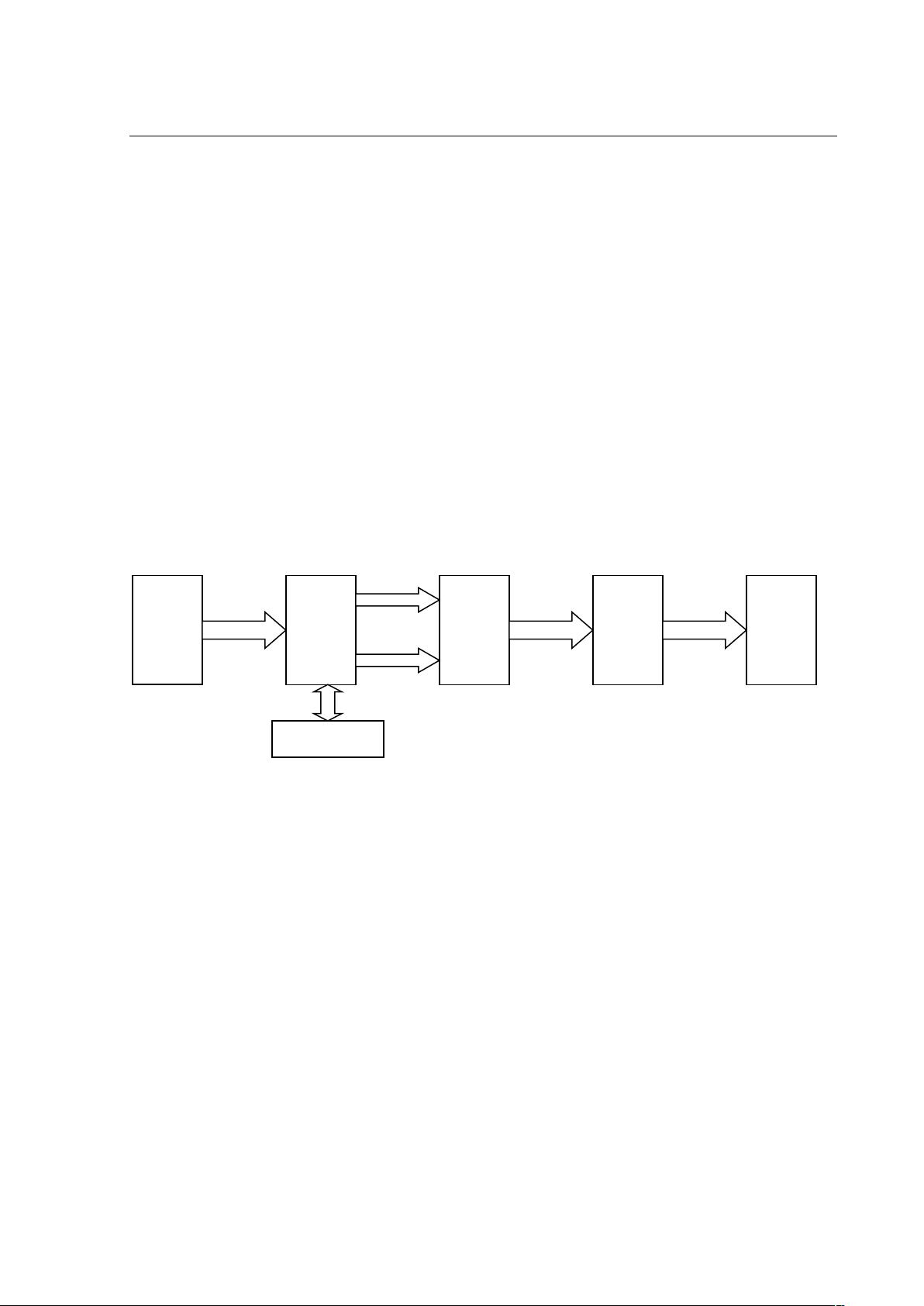

本课题主要研究LVDS接口在FPGA(现场可编程门阵列)中的实现,包括系统整体结构、LVDS原理、FPGA的结构和特点,以及并行和串行接口的设计。同时,还涵盖了硬件电路设计,如光耦合器、存储器、电源电路等,并涉及系统软件设计,如程序设计、仿真和调试。

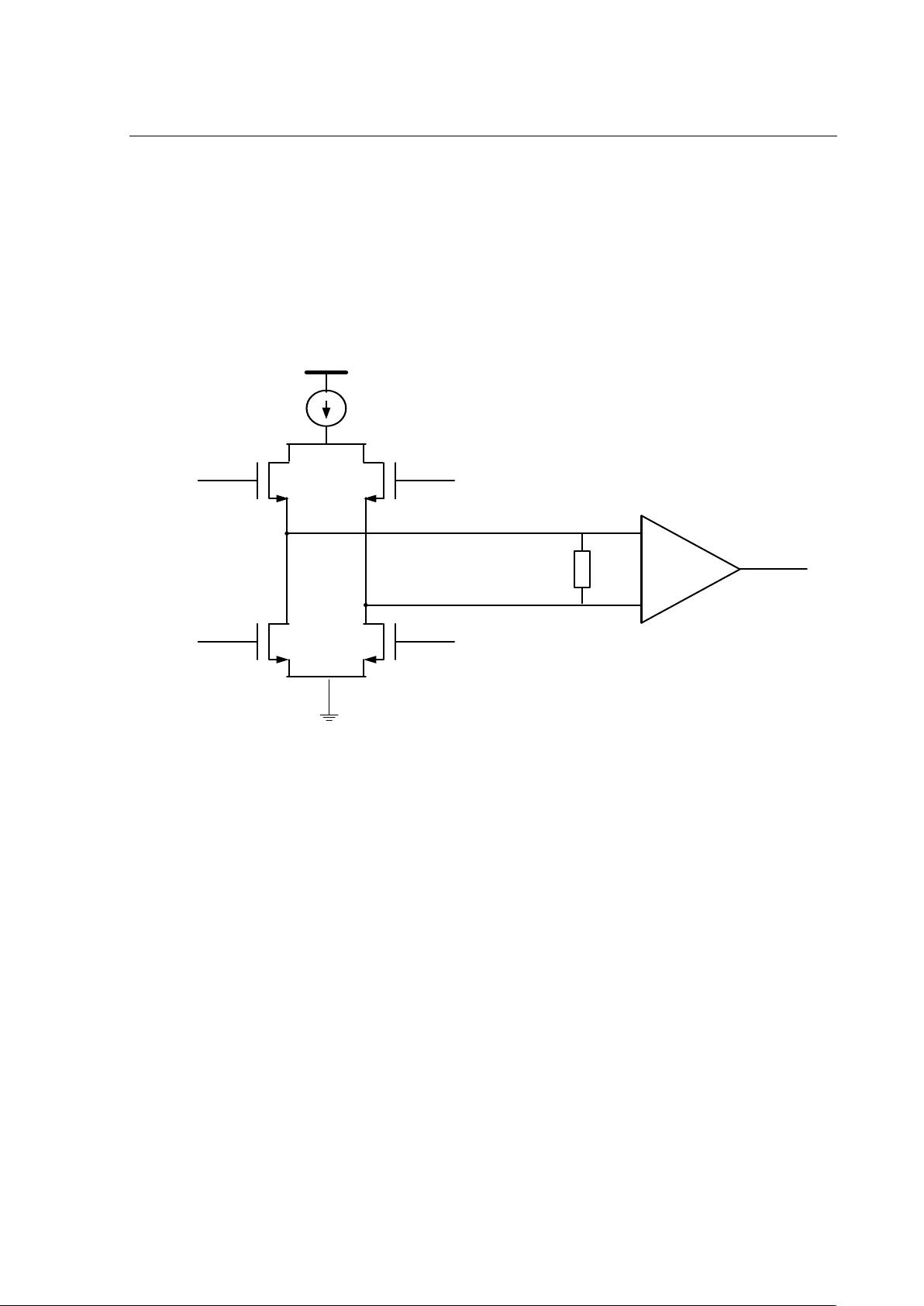

2.2 LVDS原理

LVDS通过一对差分信号线进行数据传输,利用低电压差分信号传输数据,降低了信号的电磁辐射,提高了传输效率。

2.3 FPGA结构和特点

FPGA是可编程逻辑器件,由可配置的逻辑块、输入/输出单元、互连资源等组成,具备灵活性高、速度快、可重配置等优点,适用于实现复杂的逻辑功能,如LVDS接口的并行转串行转换。

2.4 并行接口和串行接口

并行接口同时传输多个数据位,而串行接口则逐位传输。在高速传输中,串行接口可以减少布线复杂性,提高信号完整性。

3.3~3.12 整体硬件电路设计

这部分详细阐述了FPGA内部电路、配置电路、串化器配置、驱动电路、存储器、电源、下载、时钟、LED显示、开关控制和并行数据输入电路的设计,以及整体电路的性能分析。

4.1~4.3 系统软件设计

系统程序设计包括系统程序框图、晶振倍频、并行转串行程序和分频程序的实现,以及程序的仿真和调试过程。

5.1 总结与展望

总结了项目的研究成果,指出LVDS接口在3G技术及其他高速数据传输系统中的重要性,并对未来可能的发展方向进行了展望。

此文档提供了一个完整的远程数据传输中并行转串行LVDS接口设计方案,涵盖了从理论基础到实际硬件和软件设计的全过程,对理解LVDS接口设计及其在高速数据传输中的应用具有重要参考价值。

2023-07-09 上传

2023-07-10 上传

2023-06-29 上传

2023-06-29 上传

点击了解资源详情

1537 浏览量

Mmnnnbb123

- 粉丝: 764

- 资源: 8万+

最新资源

- lsh_scripts

- music.notation:可插拔音乐符号

- jq-mods

- 保险行业培训资料:方案说明与促成

- 手机工具-华为一键解锁工具

- EE461L-Group2-FinalProject:EE 416L的学期项目(软件工程实验室)

- xornada_revolusion_agasol:https的镜像

- C#与EXCEL.rar

- webrtc-stress-test:在无头模式下使用Chrome Web浏览器运行并发WebRTC会话的工具

- utils-cjson-parse:尝试将输入字符串解析为注释JSON

- Mac可视化反编译java软件 JD_JUI

- konachan100.github.io:查看来自Konachan.net的最新100条帖子:https:konachan100.github.io

- deteccao_de_fraude

- PostgreSQL10.1-CN.zip

- bsxops:强制 MATLAB 运算符的行为类似于 BSXFUN-matlab开发

- 电子功用-旋转电机的整流子表面切削方法及其装置