基于FPGA的M4K移位寄存器逻辑分析仪设计

196 浏览量

更新于2024-08-31

收藏 264KB PDF 举报

"M4K块移位寄存器数据读进方式的逻辑分析仪设计"

本文介绍了一种基于FPGA(Field-Programmable Gate Array)的逻辑分析仪设计,该设计采用了Altera公司的Cyclone系列EPlC3T144C8作为核心控制芯片,并利用QuartusⅡ作为开发软件平台。该逻辑分析仪具有16个采样通道和可变频采样时钟,其独特之处在于利用FPGA内部的M4K块作为移位寄存器,持续读取数据,从而提升了工作效率、系统稳定性和分析能力。

传统的逻辑分析仪通常将采样数据暂存在锁存器中,待触发条件满足后,再将数据输出至外部存储器。这种方法速度较慢且占用空间大,不适合大规模数据的存储。本文提出的设计方案则通过FPGA内部的M4K块不断读取数据,实现了在程序运行过程中无中断的数据读取,提高了数据处理速度,节省了存储空间,同时提供了三种不同的采样模式,增强了分析的灵活性和深度。

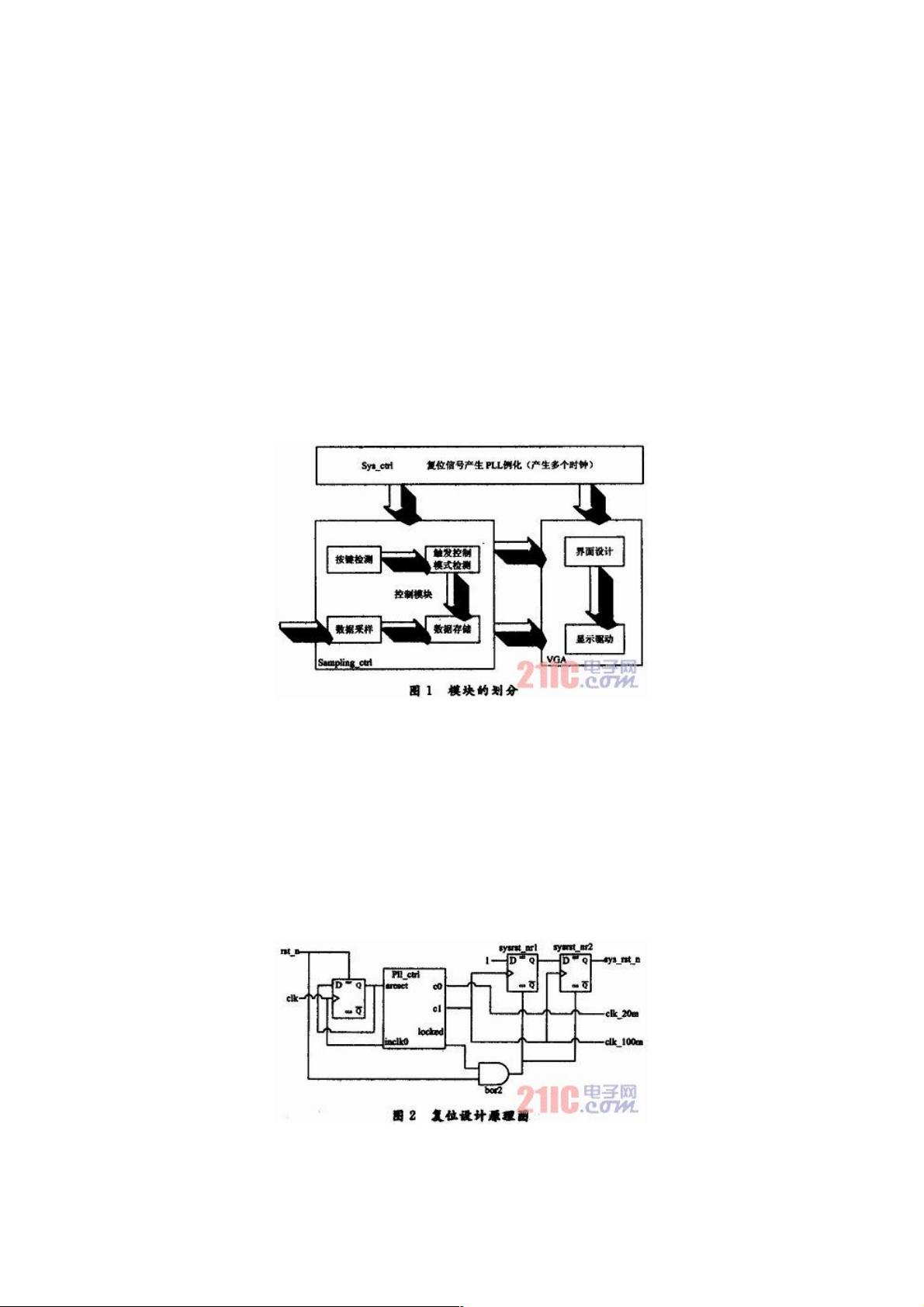

逻辑分析仪的整体架构包括数据采样、数据存储和显示控制三个部分。设计的最高信号捕获精度为100MHz,支持最多16路信号输入,1路触发信号,采样时钟可调,并且可以连接到计算机显示器以VGA模式显示波形。系统的核心——Sampling_ctrl模块,集成了按键检测、触发控制、数据采样和存储等多种功能。

此外,文章还讨论了复位信号的产生和PLL(Phase-Locked Loop)的例化,确保了系统的稳定时钟源。复位模块首先对FPGA的输入复位信号进行异步复位和同步释放,然后通过PLL产生多个稳定的时钟信号供系统使用。

总结而言,这个M4K块移位寄存器数据读进方式的逻辑分析仪设计,凭借其高效、稳定和低成本的特性,展示了在逻辑分析领域的创新应用,对于需要进行高速数据捕获和分析的场合具有很高的实用价值。关键词涉及逻辑分析仪、FPGA、采样技术和移位寄存器,这些是理解本文设计关键点的关键术语。

2022-07-14 上传

2023-05-19 上传

2024-07-24 上传

2023-06-10 上传

2023-04-27 上传

2023-05-22 上传

2023-06-24 上传

2023-07-04 上传

2023-06-08 上传

weixin_38686399

- 粉丝: 9

- 资源: 934

最新资源

- OptiX传输试题与SDH基础知识

- C++Builder函数详解与应用

- Linux shell (bash) 文件与字符串比较运算符详解

- Adam Gawne-Cain解读英文版WKT格式与常见投影标准

- dos命令详解:基础操作与网络测试必备

- Windows 蓝屏代码解析与处理指南

- PSoC CY8C24533在电动自行车控制器设计中的应用

- PHP整合FCKeditor网页编辑器教程

- Java Swing计算器源码示例:初学者入门教程

- Eclipse平台上的可视化开发:使用VEP与SWT

- 软件工程CASE工具实践指南

- AIX LVM详解:网络存储架构与管理

- 递归算法解析:文件系统、XML与树图

- 使用Struts2与MySQL构建Web登录验证教程

- PHP5 CLI模式:用PHP编写Shell脚本教程

- MyBatis与Spring完美整合:1.0.0-RC3详解