FPGA实现的RISC微处理器:VHDL设计与挑战

40 浏览量

更新于2024-09-02

收藏 154KB PDF 举报

在20世纪80年代初崛起的RISC(Reduced Instruction Set Computing,精简指令集计算机)技术引领了计算机发展潮流,其基本理论构成了计算机领域不可或缺的基础。然而,实际设计RISC微处理器并非易事,尤其是结合EDA(Electronic Design Automation,电子设计自动化)技术。EDA是现代电子设计的核心工具,其目标是通过ASIC(Application-Specific Integrated Circuit,专用集成电路)设计实现高性能电子系统。

在这个背景下,FPGA(Field-Programmable Gate Array,现场可编程门阵列)和CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)作为EDA的重要应用载体,提供了灵活且高效的平台。FPGA特别值得一提,它的内部拥有丰富的可编程资源,允许用户定制自己的逻辑结构,其外部连线少、电路简洁,易于控制,而且性能不断提升,如目前的千万门级(10 million-gatemark),工作频率可达200至400MHz。

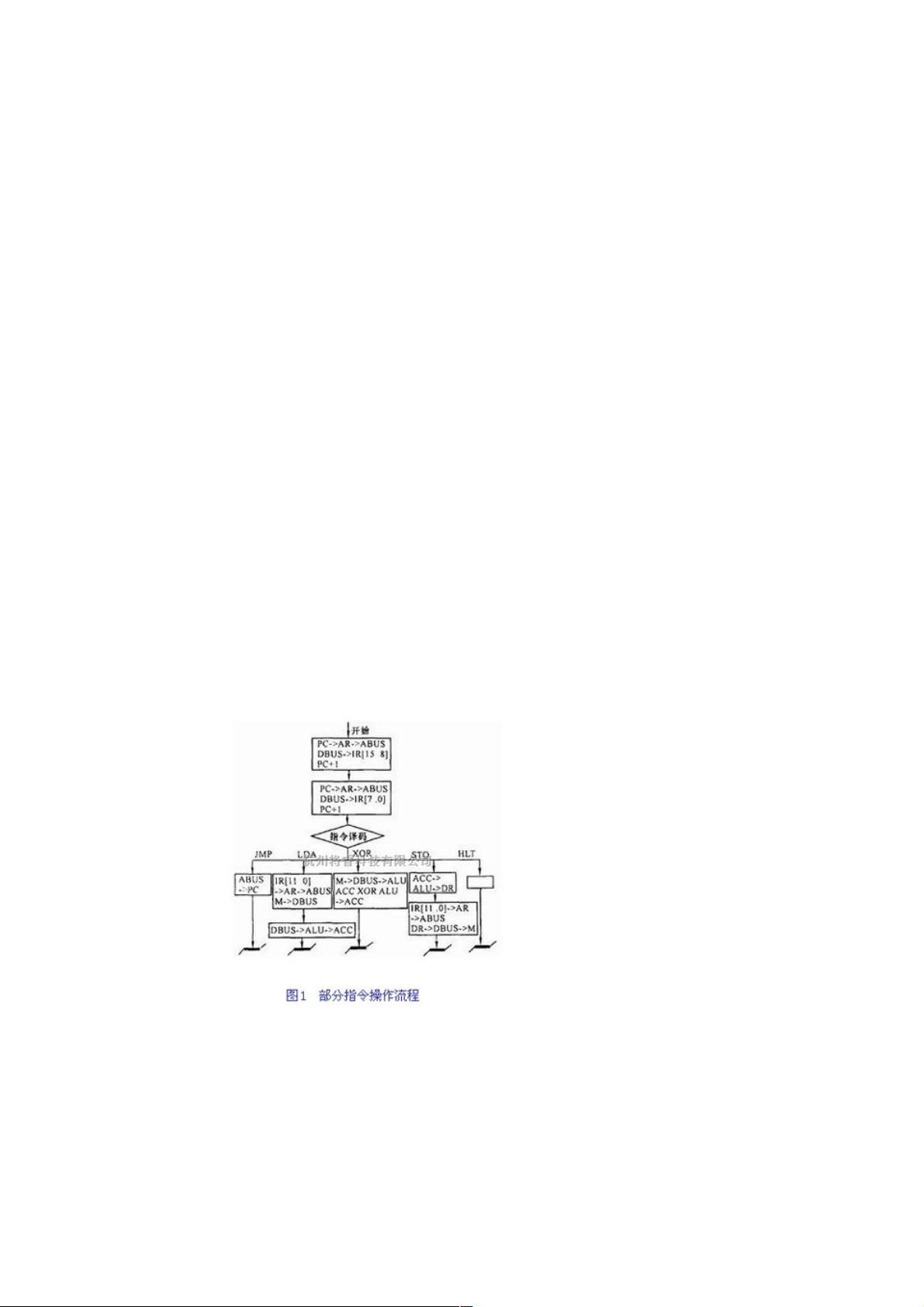

本文重点介绍了如何利用FPGA技术,通过VHDL(VHSIC Hardware Description Language,超大规模集成电路硬件描述语言)设计并实现一种8位RISC微处理器。该微处理器的设计遵循RISC架构原则,例如简化指令集、固定指令长度、单一或少数的寻址方式、大量寄存器使用以及硬连线控制等特性,以提升指令执行效率。

微处理器的基本功能包括指令控制、操作控制、时间控制和数据处理,而设计中具体包括控制器、运算器和寄存器单元,还有程序计数器、译码器等辅助组件。控制器作为核心决策机构,负责协调和管理系统的运行流程。

本文不仅探讨了理论概念,还提供了实际设计过程中的仿真和综合结果,展示了基于FPGA的RISC微处理器设计与实现的技术细节和实用性。这样的设计方法对于理解RISC微处理器的构建原理和优化策略,以及在现代嵌入式系统和应用中灵活运用EDA技术具有重要意义。

2020-12-10 上传

2020-11-29 上传

2020-12-08 上传

2024-06-30 上传

2024-10-28 上传

2024-11-11 上传

2023-08-18 上传

2023-08-25 上传

2024-11-11 上传

weixin_38637805

- 粉丝: 4

- 资源: 952

最新资源

- Thinking in java 2rd Edition

- 互联网产品开发流程文档

- 七种数据库连接 mysql、oracle……

- 模式识别前四章答案-清华大学-边肇祺

- struts2权威指南

- Struts in Action 中文版

- JBoss+jBPM+jPDL用户开发手册

- PHOTOSHOP技巧

- 李涛JAVA学习资料

- 人力资源系统很详细的描述

- JasperReport-iReport报表开发指南.pdf

- Ant全攻略 教会你如何玩转Ant

- 手把手教你用C#打包应用程序(安装程序)

- 实战Acegi:使用Acegi作为基于Spring框架的WEB应用的安全框架

- 数字电视原理与实现pdf

- 我的VS2008学习资料