探索同步时序逻辑与流水线设计:解决竞争冒险实验

需积分: 0 45 浏览量

更新于2024-08-05

收藏 270KB PDF 举报

实验09_竞争冒险及流水线技术1 是一项针对IT专业人士的实践课程,旨在帮助学习者深入了解电路设计中的时序逻辑和同步电路原理,特别是通过流水线技术来提升电路性能。课程的核心内容包括以下几个方面:

1. **电路描述与实现**:利用Verilog语言进行电路描述,这是硬件描述语言的一种,常用于描述数字电路的行为。通过Vivado工具,学生将在FPGA实验平台上实现这些电路,Vivado是一个广泛使用的FPGA开发工具,提供综合、适配、编程和配置等功能。

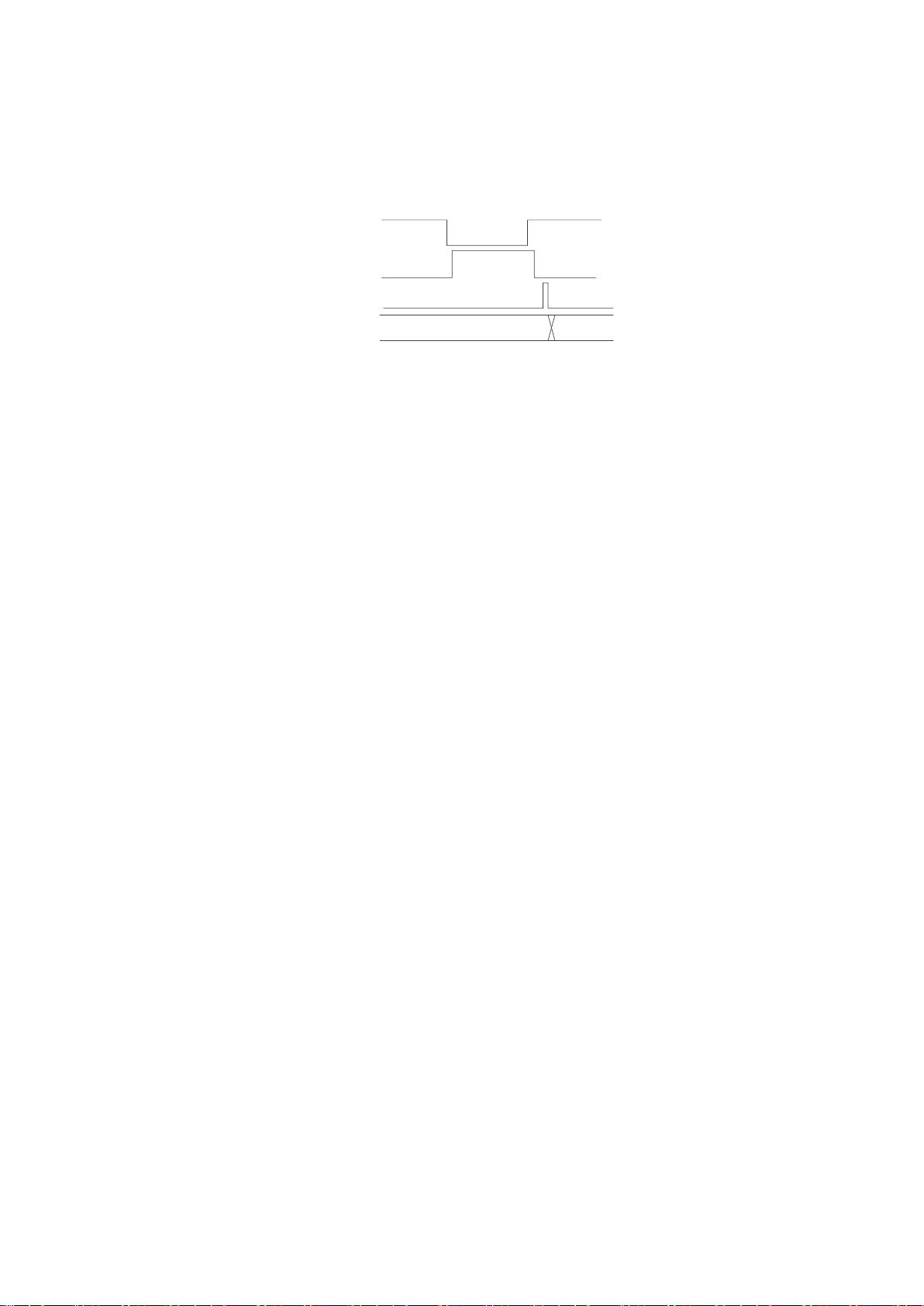

2. **电路运行与仿真**:通过Vivado的集成环境,学生将学习如何设计并模拟电路,以识别可能存在的问题。在电路运行过程中,可能会遇到竞争冒险(race condition)的现象,即多个信号同时影响同一个结果,导致不可预测的结果。

3. **竞争冒险的理解与解决**:课程讲解了为何在实际电路中组合逻辑电路较少见,因为它们容易引发竞争冒险。通过Logisim软件,学生将亲身体验这种现象,并学习如何通过设计优化避免它。

4. **流水线技术**:实验重点在于流水线设计,一种提高时序逻辑电路性能的方法,通过将连续的任务分解为多个阶段,每个阶段独立执行,从而减少等待时间。学生将掌握流水线设计原则和异常处理策略。

5. **实验目标与环境**:实验目标包括掌握时序逻辑基础、理解同步时序逻辑优势、学习流水线设计技巧,以及处理流水线运行中的异常。实验环境要求具备一台PC,运行Windows或Linux操作系统,以及如Vivado、Logisim和FPGA实验平台(Nexys4DDR)等工具。

6. **实验步骤**:实验分为多个步骤,首先让学生分析组合逻辑电路中的竞争冒险问题,然后通过设计流水线来改进。整个过程涉及理论知识的应用和实践经验的积累,目的是提升学生的电路设计和分析能力。

通过本实验,读者将不仅巩固先前实验中学到的组合逻辑电路设计,还将深入理解时序逻辑电路的内在机制,掌握流水线设计这一关键技术,这对于提升电路设计效率和系统性能具有重要意义。

2022-05-05 上传

2022-08-08 上传

2021-10-02 上传

2012-11-08 上传

2022-09-22 上传

2021-09-11 上传

2021-09-30 上传

2021-10-10 上传

2021-09-11 上传

点墨楼

- 粉丝: 37

- 资源: 279

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜