CPLD FPGA实现的高效数字频率计设计

版权申诉

171 浏览量

更新于2024-06-25

收藏 1.95MB DOC 举报

"基于CPLD FPGA的数字频率计系统的设计"

本文档详细介绍了如何使用CPLD (复杂可编程逻辑器件) 和FPGA (现场可编程门阵列) 设计一个数字频率计系统。设计过程中,作者采用了EDA (电子设计自动化) 工具Quartus II,并使用VHDL (Very High Speed Integrated Circuit Hardware Description Language) 语言进行编程,以实现高效、精确的频率测量。

在第一章中,首先阐述了EDA技术及其发展历程,以及CPLD和FPGA的基本概念。CPLD和FPGA是现代数字系统设计中常用的可编程逻辑器件,它们允许设计者根据需求定制硬件逻辑,提供高灵活性和性能。接着,讨论了数字频率计系统的设计背景和课题任务,强调了简化设计和提高系统可靠性的目标。

第二章中,详细讲解了数字频率计的工作原理,包括测频的基本原理。系统通过计数被测信号在一个固定时间周期内的脉冲数量,然后计算出频率。设计了一个总体设计方案,为后续硬件和软件设计提供了框架。

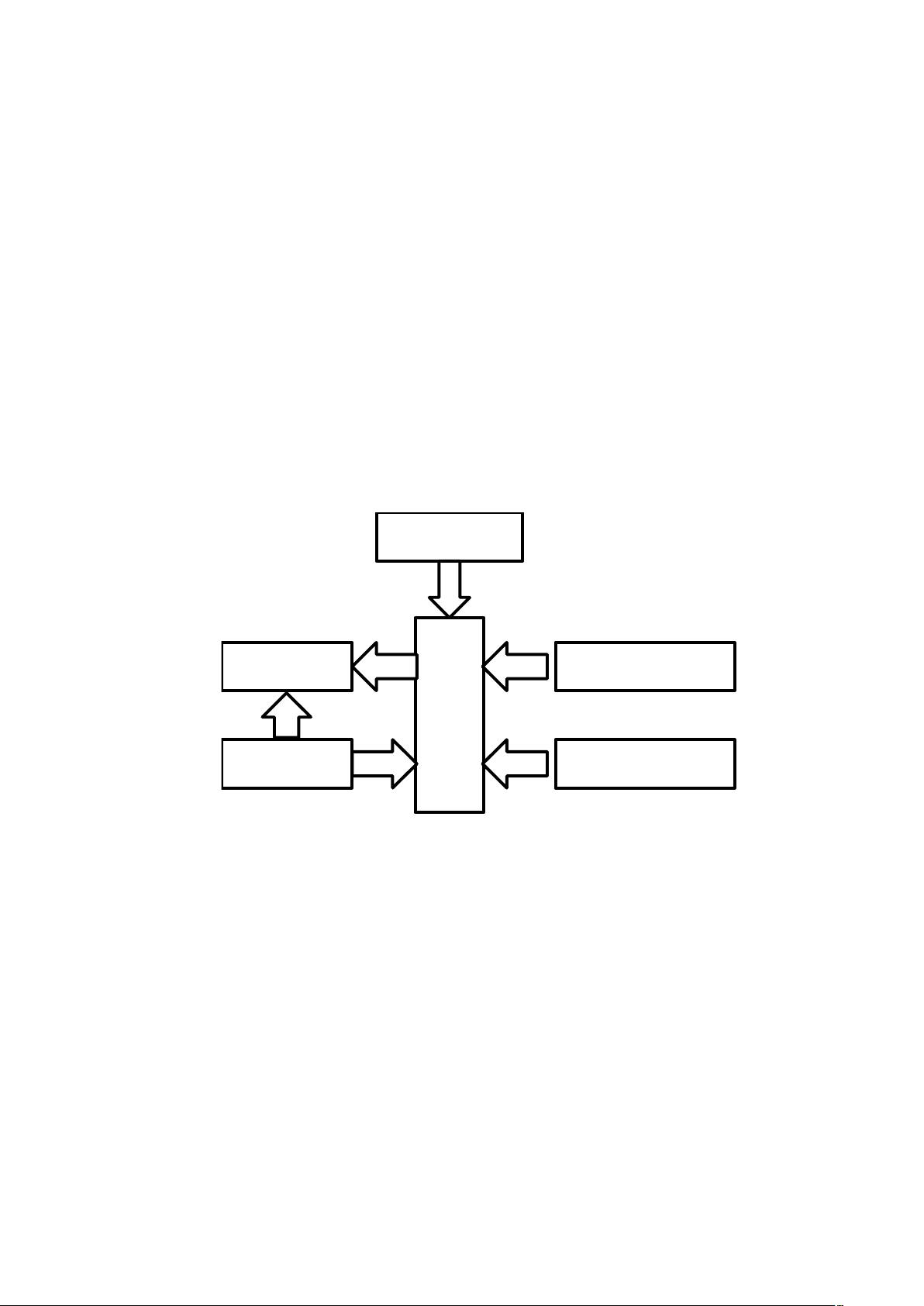

第三章主要探讨了系统的硬件设计,包括系统原理框图、可编程逻辑器件的选择、时钟电路、电源电路、显示电路、下载接口电路以及拓展电路。其中,时钟电路是系统的心脏,提供精确的时间基准;电源电路确保设备稳定运行;显示电路用于直观地展示测量结果;下载接口电路则用于将VHDL程序下载到CPLD/FPGA中;而拓展电路如ADC0804和DAC0832接口,可以实现模拟信号的数字化处理,扩大了系统功能。

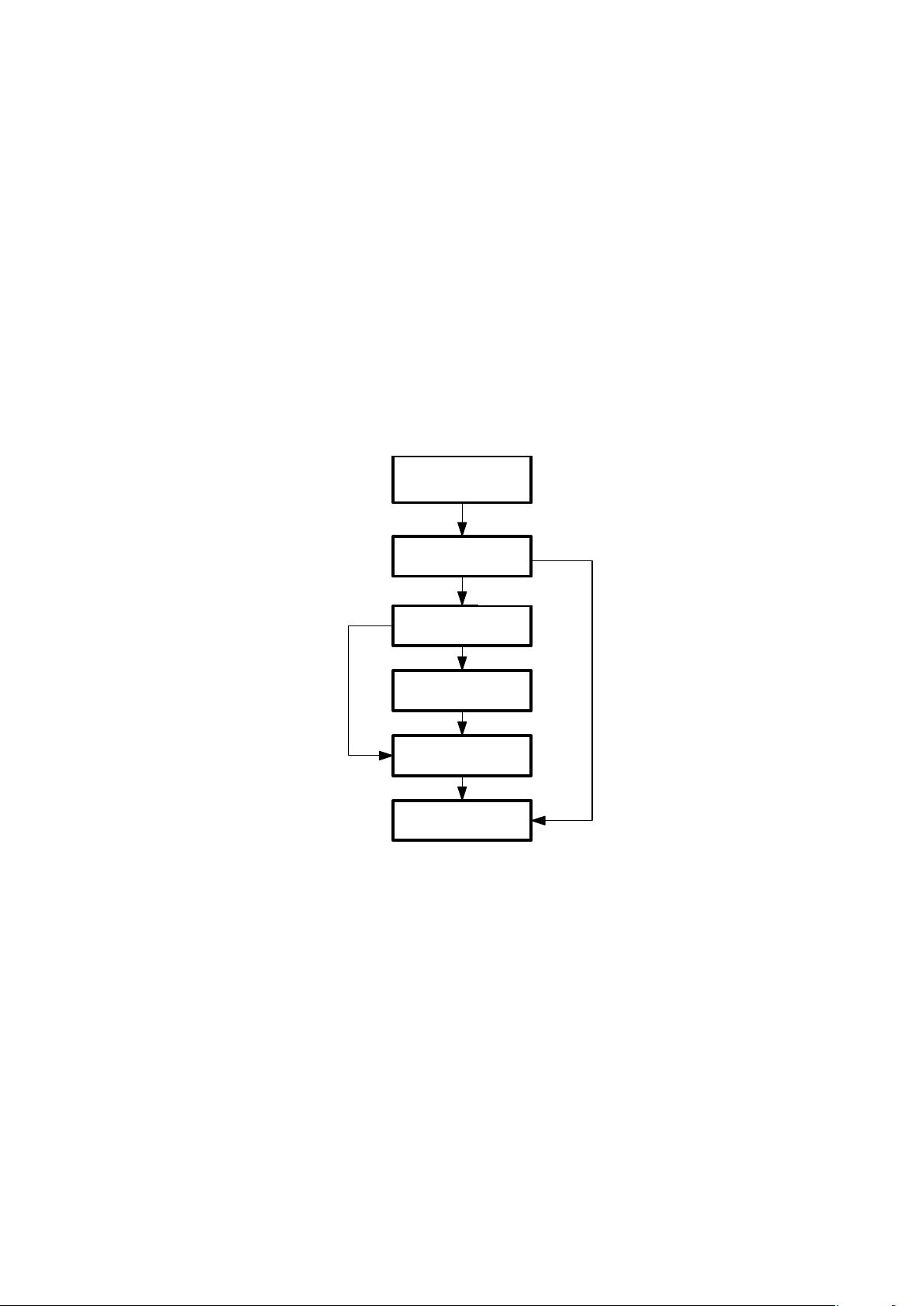

第四章则转向软件设计,介绍了Quartus II工具的使用,包括其设计流程和VHDL编程流程。各个功能模块如分频模块、测频控制模块、计数模块、锁存器模块和显示模块的VHDL程序设计也进行了详细说明,这些模块共同构成了频率计的核心逻辑。

第五章是系统调试与误差分析,讲述了如何验证设计的正确性并分析可能产生的误差,以及测试结果的分析。

最后,文档以结束语和致谢收尾,并附带了原理图、PCB图和程序清单,为读者提供了完整的设计参考资料。

这个设计实例展示了CPLD/FPGA在数字系统设计中的强大能力,以及VHDL在实现复杂逻辑功能上的优势,对于学习数字电路、嵌入式系统和硬件描述语言的读者具有很高的参考价值。

2023-06-20 上传

156 浏览量

2010-03-01 上传

2021-09-18 上传

2023-07-08 上传

2021-09-18 上传

老帽爬新坡

- 粉丝: 98

- 资源: 2万+

最新资源

- Zigbee入门学习

- at&t 部分语法大 其中的一个小块

- ARM嵌入式系统实验教程(二)附加实验教程

- NETBEANS RCP.PDF

- 基于超混沌的FM_DCSK系统的性能分析.pdf

- GPRS模块Q39的介绍

- 《effective software testing》 addison wesley 著

- unix/linux系统管理

- 基于ORACLE数据融合的一卡通系统的实现

- java西安公司考试考试资源

- FPGA设计的经验谈

- RestFul_Rails_Dev_v_0.1

- 软件工程师笔试题目(应聘)

- 宫东风考研英语讲座.宫东风考研英语讲座

- ARM嵌入式WINCE实践教程

- SCCP信令原理介绍