TLV2548-EP

www.ti.com

SLAS668 –OCTOBER 2009

as the channel is selected (after the fifth SCLK). In this case the sampling period is not started until CS has

become inactive. Therefore the non-overlapped CSTART low time must meet the minimum sampling time

requirement. The low–to–high transition of CSTART terminates the sampling period and starts the conversion

period. The conversion clock can also be configured to use either internal OSC or external SCLK. This function is

useful for an application that requires:

• The use of an extended sampling period to accommodate different input source impedance.

• The use of a faster I/O clock on the serial port but not enough sampling time is available due to the fixed

number of SCLKs. This could be due to a high input source impedance or due to higher MUX ON resistance

at lower supply voltage.

Once the conversion is complete, the processor can initiate a read cycle by using either the read FIFO command

to read the conversion result or by simply selecting the next channel number for conversion. Since the device

has a valid conversion result in the output buffer, the conversion result is simply presented at the serial data

output. To completely get out of the extended sampling mode, CS must be toggled twice from a high-to-low

transition while CSTART is high. The read cycle mentioned above followed by another configuration cycle of the

ADC qualifies this condition and successfully puts the ADC back to its normal sampling mode. This can be

viewed in Figure 9.

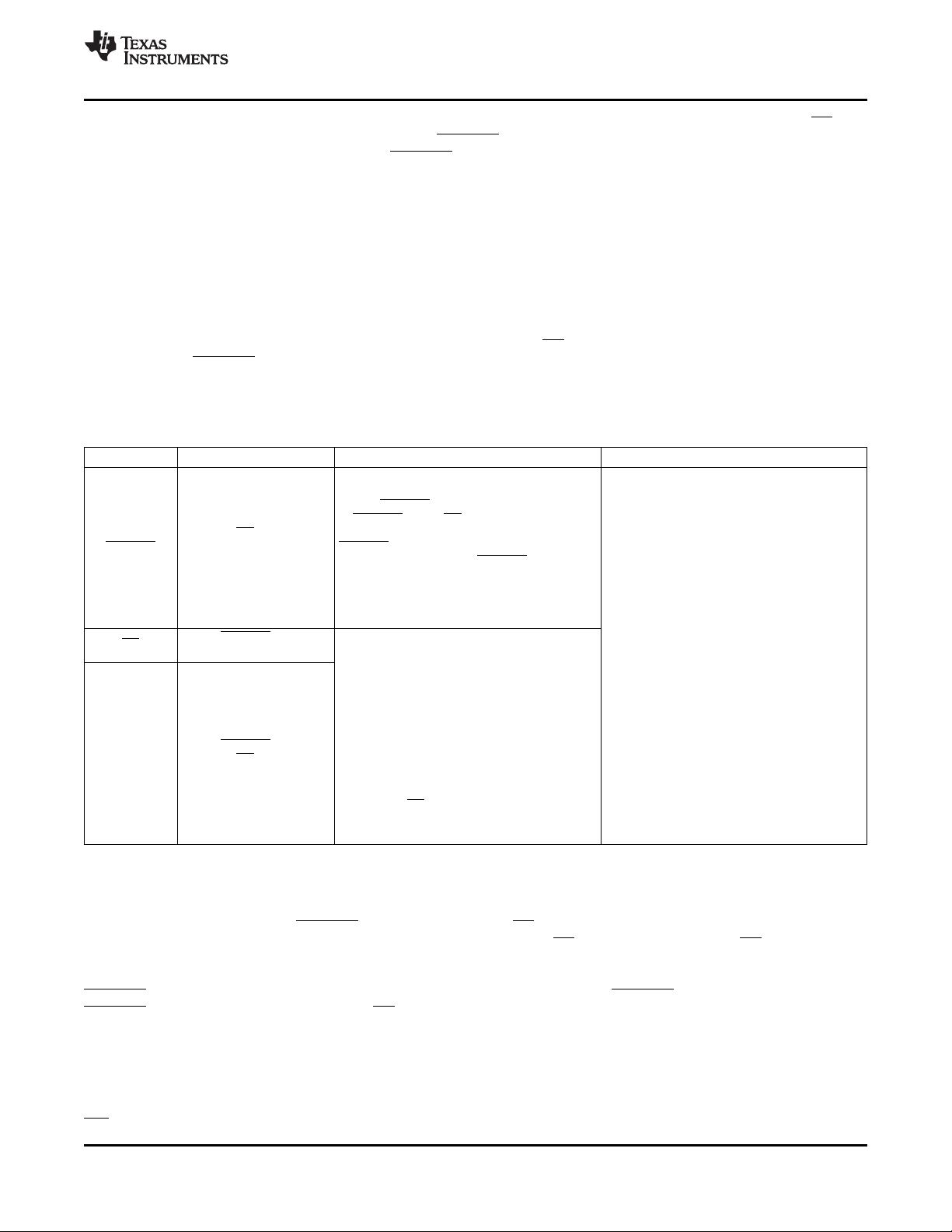

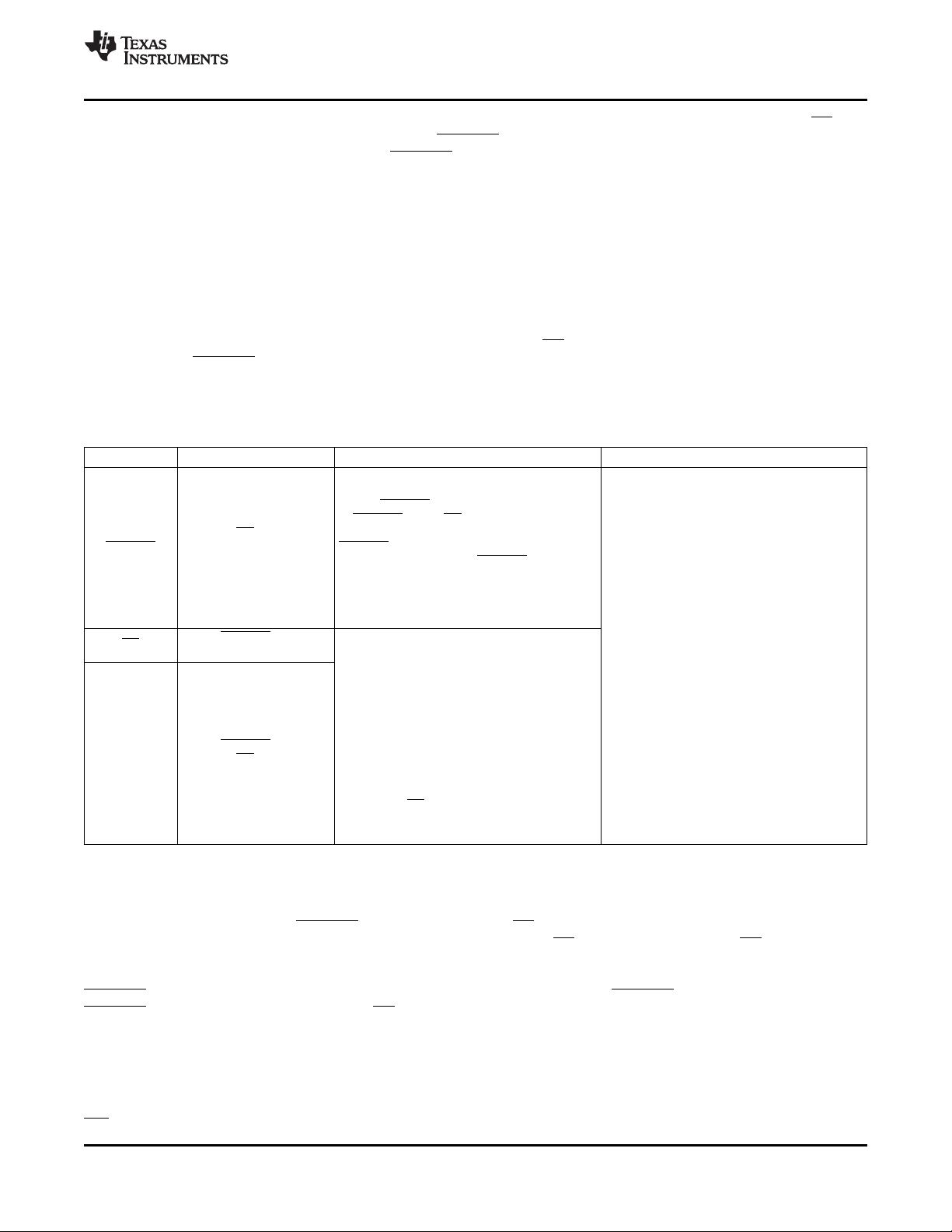

Table 5. Sample and Convert Conditions

CONDITIONS SAMPLE CONVERT

No sampling clock (SCLK) required.

Sampling period is totally controlled by the low

time of CSTART. The high–to–low transition

of CSTART (when CS = 1) starts the sampling

CS = 1 of the analog input signal. The low time of

CSTART (see Figure 11 and CSTART dictates the sampling period. The

Figure 19) low–to–high transition of CSTART ends

sampling period and begins the conversion

cycle. (Note: this trigger only works when

internal reference is selected for conversion

modes 01, 10, and 11.)

1) If the internal clock OSC is selected, a

maximum conversion time of 3.86 μs can be

CSTART = 1 SCLK is required. Sampling period is

CS

achieved.

FS = 1 programmable under normal sampling. When

2) If external SCLK is selected, conversion

programmed to sample under short sampling,

time is t

conv

= 14 x DIV/f

(SCLK)

, where DIV can

12 SCLKs are generated to complete

be 1, 2, or 4.

sampling period. 24 SCLKs are generated

when programmed for long sampling. A

command set to configure the device requires

4 SCLKs thereby extending to 16 or 28

CSTART = 1

SCLKs respectively before conversion takes

FS

CS = 0

place. (Note: Because the ADC only bypasses

a valid channel select command, the user can

use select channel 0, 0000b, as the SDI input

when either CS or FS is used as trigger for

conversion. The ADC responds to commands

such as SW powerdown, 1000b.)

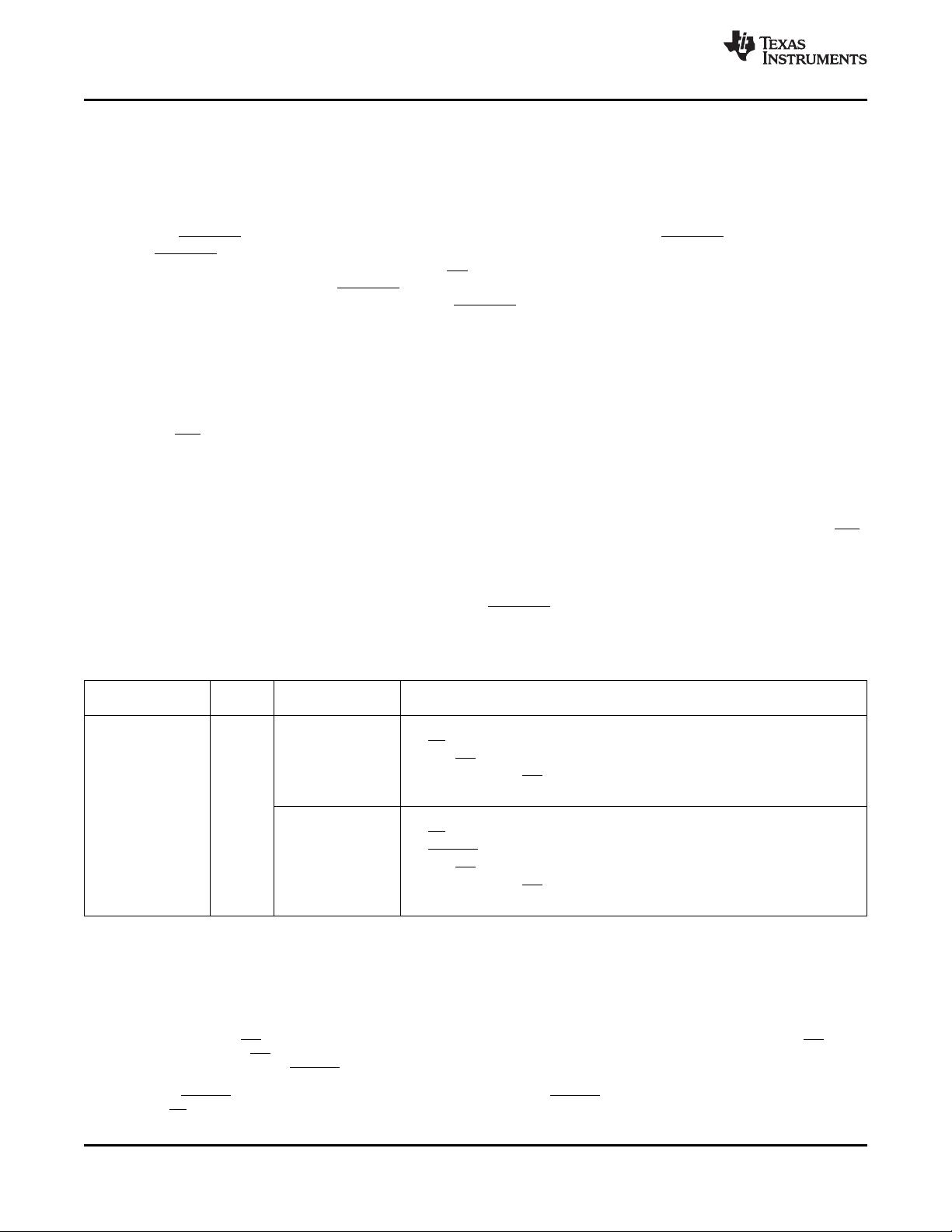

TLV2548 Conversion Modes

The TLV2548 has four different conversion modes (mode 00, 01, 10, 11). The operation of each mode is slightly

different, depending on how the converter performs the sampling and which host interface is used. The trigger for

a conversion can be an active CSTART (extended sampling), CS (normal sampling, SPI interface), or FS (normal

sampling, TMS320 DSP interface). When FS is used as the trigger, CS can be held active, i.e. CS does not need

to be toggled through the trigger sequence. SDI can be one of the channel select commands, such as SELECT

CHANNEL 0. Different types of triggers should not be mixed throughout the repeat and sweep operations. When

CSTART is used as the trigger, the conversion starts on the rising edge of CSTART. The minimum low time for

CSTART is equal to t

(SAMPLE)

. If an active CS or FS is used as the trigger, the conversion is started after the 16th

or 28th SCLK edge. Enough time (for conversion) should be allowed between consecutive triggers so that no

conversion is terminated prematurely.

One Shot Mode (Mode 00)

One shot mode (mode 00) does not use the FIFO, and the EOC is generated as the conversion is in progress (or

INT is generated after the conversion is done).

Copyright © 2009, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): TLV2548-EP