FPGA/CPLD状态机的稳定性提升策略与设计挑战

16 浏览量

更新于2024-08-31

收藏 276KB PDF 举报

FPGA/CPLD状态机的稳定性设计是现代电子系统设计中的关键环节,特别是在大规模集成电路的发展背景下,硬件描述语言(HDL)如VHDL的运用使得状态机设计变得更为重要。状态机作为FPGA/CPLD中最常见和广泛应用的时序电路模块,其设计稳定性和可靠性直接影响系统的性能和可靠性。

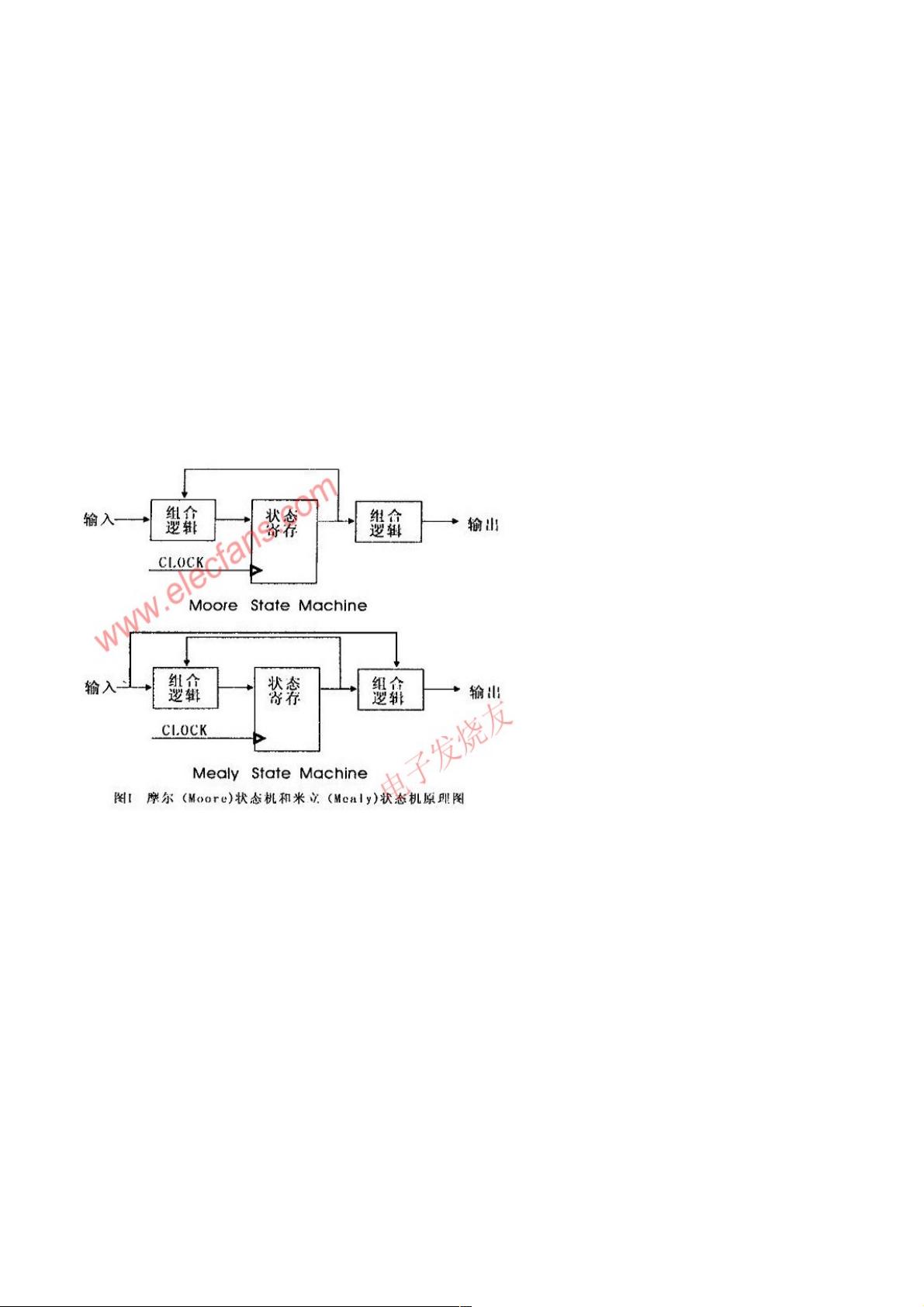

状态机主要有两种类型:Moore状态机和Mealy状态机。Moore状态机的输出仅取决于当前的状态值,输出变化仅在时钟边沿触发,而Mealy状态机的输出同时考虑当前状态值和输入值,这使得它的控制和输出更为灵活,但也带来了设计复杂度的提升。理解状态机的工作原理有助于我们更好地利用它们,例如,状态机的结构清晰,用VHDL描述易于理解和调试,其稳定的运行模式类似于CPU,特别适合进行顺序控制的设计。

然而,状态机设计并非没有挑战。常见的问题包括:在状态转换过程中可能出现过渡状态,即在从一个状态转换到另一个状态时,中间可能会经过非预期的状态;在运行过程中,可能会进入非法状态,这可能导致系统崩溃或错误;此外,设计在某种特定器件上表现良好,但在移植到其他器件时可能无法保持一致,这是因为不同器件的硬件特性可能存在差异。另外,尽管状态机能够实现稳定的逻辑功能,但过度复杂的结构会占用大量逻辑资源,这在FPGA中尤为明显,因为FPGA资源有限,过度使用可能导致性能下降。

在FPGA设计中,确保状态机的稳定性是一项细致的任务,需要对设计策略进行深思熟虑,包括选择适当的逻辑结构、优化状态机的结构以减少冗余,以及充分考虑到器件间的兼容性问题。设计师需要遵循最佳实践,比如采用适当的错误处理机制,进行充分的仿真验证,并进行必要的硬件映射优化,以确保最终实现的稳定性。

总结来说,FPGA/CPLD状态机的稳定性设计是一个涉及理论、工具和实践经验的综合过程,通过深入理解状态机的工作原理,合理利用VHDL等高级语言工具,以及应对实际设计中的问题,才能设计出既稳定又高效的FPGA状态机。

2020-07-19 上传

2020-07-27 上传

2024-11-13 上传

2024-11-13 上传

2024-11-13 上传

2024-11-13 上传

2024-11-13 上传

2024-11-13 上传

weixin_38626032

- 粉丝: 7

- 资源: 918

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载