基于FPGA和PCI的高精度码盘测速系统设计

153 浏览量

更新于2024-09-01

收藏 354KB PDF 举报

"EDA/PLD中的基于FPGA 和PCI 的高精度测速板卡的设计与实现"

本文主要探讨了一种基于FPGA(Field-Programmable Gate Array)和PCI(Peripheral Component Interconnect)总线技术的高精度测速板卡的设计与实现。这种新型测速方法旨在克服传统码盘测速方法如M法、T法和M/T法的局限性,以提供更广泛速度范围内的高精度和快速响应。

在传统的测速方法中,M法依赖于计数器在特定采样周期内记录的脉冲数,适用于高频率脉冲,但在低速时由于脉冲数量较少可能导致精度下降。T法则是通过测量两个连续脉冲间的间隔时间来计算速度,但在高速时,由于时间间隔短,测量误差可能增大。M/T法结合了这两种方法,同时计数脉冲和高频时标信号,以提高精度,但仍然存在低速时采样不稳定的问题。

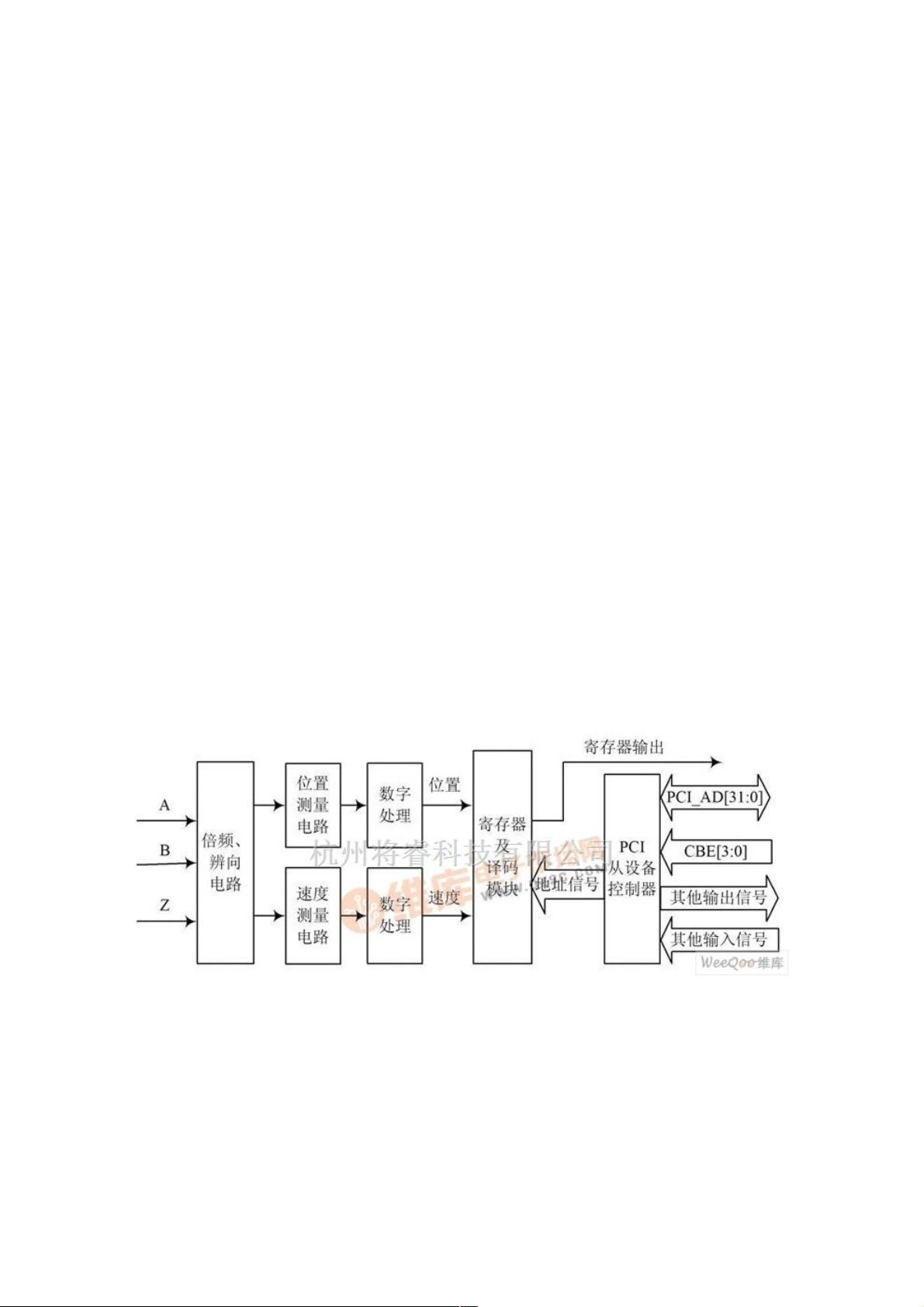

为了解决这些问题,文章提出了一种新的设计方案,该方案利用FPGA作为核心处理器。FPGA是一种可编程逻辑器件,能够根据需求灵活配置,具有高速处理和实时计算的能力。在该系统中,FPGA负责解析码盘输出的脉冲信号,进行高速数据处理,以获取精确的转速信息。

数据通信方面,设计采用了PCI总线,这是一种高性能的局部总线标准,允许设备控制器与主机计算机之间快速交换数据。通过简化PCI从设备控制器,实现了对PCI总线的普通读和猝发读操作,优化了数据传输效率,确保了在不同速率下都能及时地将测速数据传送给控制计算机。

增量式码盘作为关键的传感器元件,它提供了高分辨率的位置和速度信息,其抗干扰性强,适合长距离传输。码盘产生的脉冲信号被FPGA实时采集和分析,根据脉冲频率计算出被测轴的转速。通过这种方法,即使在极端速度条件下,也能保证测量的准确性和实时性。

此外,该设计还可能包含了一些优化措施,例如使用高级的同步和滤波算法来减少噪声影响,以及利用FPGA的并行处理能力实现快速数据处理。这样的设计为高速、高精度的伺服控制系统提供了有力的支持,尤其对于那些需要精确速度和位置信息的复杂应用,如自动化生产线、精密机床和机器人等。

总结来说,"EDA/PLD中的基于FPGA 和PCI 的高精度测速板卡的设计与实现"这一研究工作,通过创新的硬件设计和优化的数据通信机制,成功地提升了码盘测速系统的性能,为现代工业控制系统的速度测量提供了一种更为可靠和高效的解决方案。

2020-07-31 上传

2020-11-05 上传

2020-12-13 上传

2020-11-11 上传

2020-11-09 上传

2020-12-05 上传

2020-12-13 上传

2020-11-11 上传

点击了解资源详情

weixin_38590355

- 粉丝: 7

- 资源: 935

最新资源

- 平尾装配工作平台运输支撑系统设计与应用

- MAX-MIN Ant System:用MATLAB解决旅行商问题

- Flutter状态管理新秀:sealed_flutter_bloc包整合seal_unions

- Pong²开源游戏:双人对战图形化的经典竞技体验

- jQuery spriteAnimator插件:创建精灵动画的利器

- 广播媒体对象传输方法与设备的技术分析

- MATLAB HDF5数据提取工具:深层结构化数据处理

- 适用于arm64的Valgrind交叉编译包发布

- 基于canvas和Java后端的小程序“飞翔的小鸟”完整示例

- 全面升级STM32F7 Discovery LCD BSP驱动程序

- React Router v4 入门教程与示例代码解析

- 下载OpenCV各版本安装包,全面覆盖2.4至4.5

- 手写笔画分割技术的新突破:智能分割方法与装置

- 基于Koplowitz & Bruckstein算法的MATLAB周长估计方法

- Modbus4j-3.0.3版本免费下载指南

- PoqetPresenter:Sharp Zaurus上的开源OpenOffice演示查看器