FPGA驱动的60键多态按键状态识别系统设计与实现

63 浏览量

更新于2024-08-28

收藏 424KB PDF 举报

本文档主要探讨了基于FPGA(Field-Programmable Gate Array)的多按键状态识别系统设计,针对现有按键输入电路的局限性,提出了一个解决方案。传统的方法存在非扫描方式对大量按键处理能力有限且I/O端口需求大的问题,以及扫描阵列方式无法实现多键同时按下。为解决这些问题,设计者利用FPGA的可编程性和丰富的I/O端口,选择VHDL(Vocabulary of Hardware Description Language)作为设计语言。

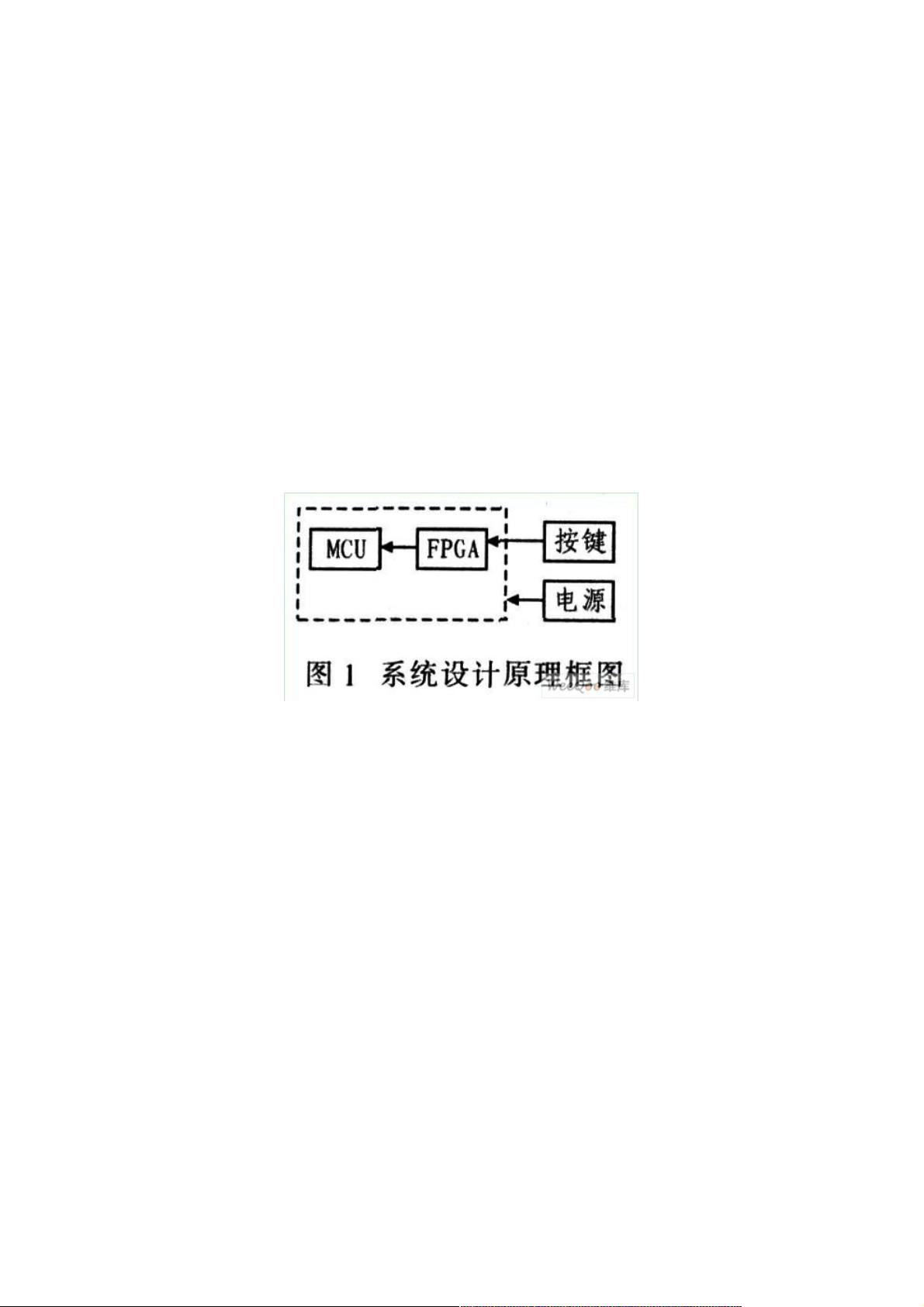

系统的核心设计目标是创建一个能够同时处理大量按键并节省单片机(MCU)I/O资源的系统。FPGA作为硬件平台,其内部的逻辑单元、存储器以及高速运算能力使其成为理想的选择。系统架构包括MCU、FPGA以及按键模块,按键信号通过FPGA进行采集和编码,然后将数据暂存于内部FIFO(First In First Out)中,供MCU读取。电源管理部分确保各组件的正常运行。

具体到硬件配置,文中提到使用了Altera公司的EPF10K30ATC144 FPGA,其具有3.3V供电、102个I/O端口、高达100MHz的工作频率,以及足够的逻辑单元和存储空间,足以支持60个按键的识别和高效处理。为了初始化FPGA,设计中还涉及到外部存储器用于存储配置数据,因为FPGA是基于RAM工艺,需要预先加载配置信息。

此外,系统设计的关键在于FPGA的配置电路,它确保了FPGA在启动时能够正确地执行预设的程序,从而实现按键状态的准确识别。通过精心设计的系统结构,本文提出的方法旨在提高按键输入系统的灵活性和效率,同时降低了对MCU资源的需求,这对于现代电子设备,特别是那些需要处理大量按键交互的场合来说,具有重要的实用价值。

131 浏览量

958 浏览量

133 浏览量

116 浏览量

148 浏览量

151 浏览量

487 浏览量

1588 浏览量

151 浏览量

weixin_38738422

- 粉丝: 3

- 资源: 922

最新资源

- 电子功用-数字电流模控制Boost变换器的建模及稳定性分析方法

- java-grok:简单的API,可让您轻松解析日志和其他文件

- SpaceShooter:简单的C ++ SFML库游戏

- GOO

- MATLAB 遍历算法

- 建立一流的以创新为导向的业务计划、营销和供应链管理体系

- 一站式工作

- 辽宁工程技术大学计算机类专业课程《数据结构》授课PPT课件+实例代码+上机实验+期末复习题(含答案)

- 供应链计划及排程技术与市场全球透视

- BattleTank:开放世界,面对面的坦克大战。 在虚幻4中

- C++写的贪吃蛇游戏

- portfolio-source:我的投资组合网站的源代码

- 树莓派智能小车 循迹 超声波避障 红外避障 红外追踪 遥控小车代码.zip

- 使用 MATLAB 为风电场制作动画:添加现实主义:演示中添加了现实主义-matlab开发

- Juicy.Voxels:Haskell中的卷文件加载器(PVMGifimage列表)

- 供应链管理原理及应用