硬件加速与IC验证技术:FPGA、模拟器与云解决方案

需积分: 50 109 浏览量

更新于2024-07-09

1

收藏 27.66MB DOCX 举报

"本文档主要介绍了IC验证中的硬件加速手段,包括FPGA和模拟器的使用,以及相关的EDA工具。此外,还涉及了SystemVerilog(SV)的学习,包括逻辑类型的区分、枚举类型的操作、过程与方法的差异、接口与模块的实例化规则,以及错误处理和结构体的使用等知识点。"

在IC验证过程中,硬件加速是一个关键环节,以快速验证设计的正确性。FPGA(Field-Programmable Gate Array)因其可重构性,能实现快速原型验证,而模拟器(emulator)则提供了更快的运行速度,虽不及FPGA,但优于仿真器。EDA公司的模拟器具备检测内部信号、设置断点和保存波形等功能,这些在FPGA中难以实现。模拟器内部通常基于FPGA构建,但通过优化和封装,更便于用户进行调试。然而,模拟器的价格昂贵,大型公司可能需要排队使用。

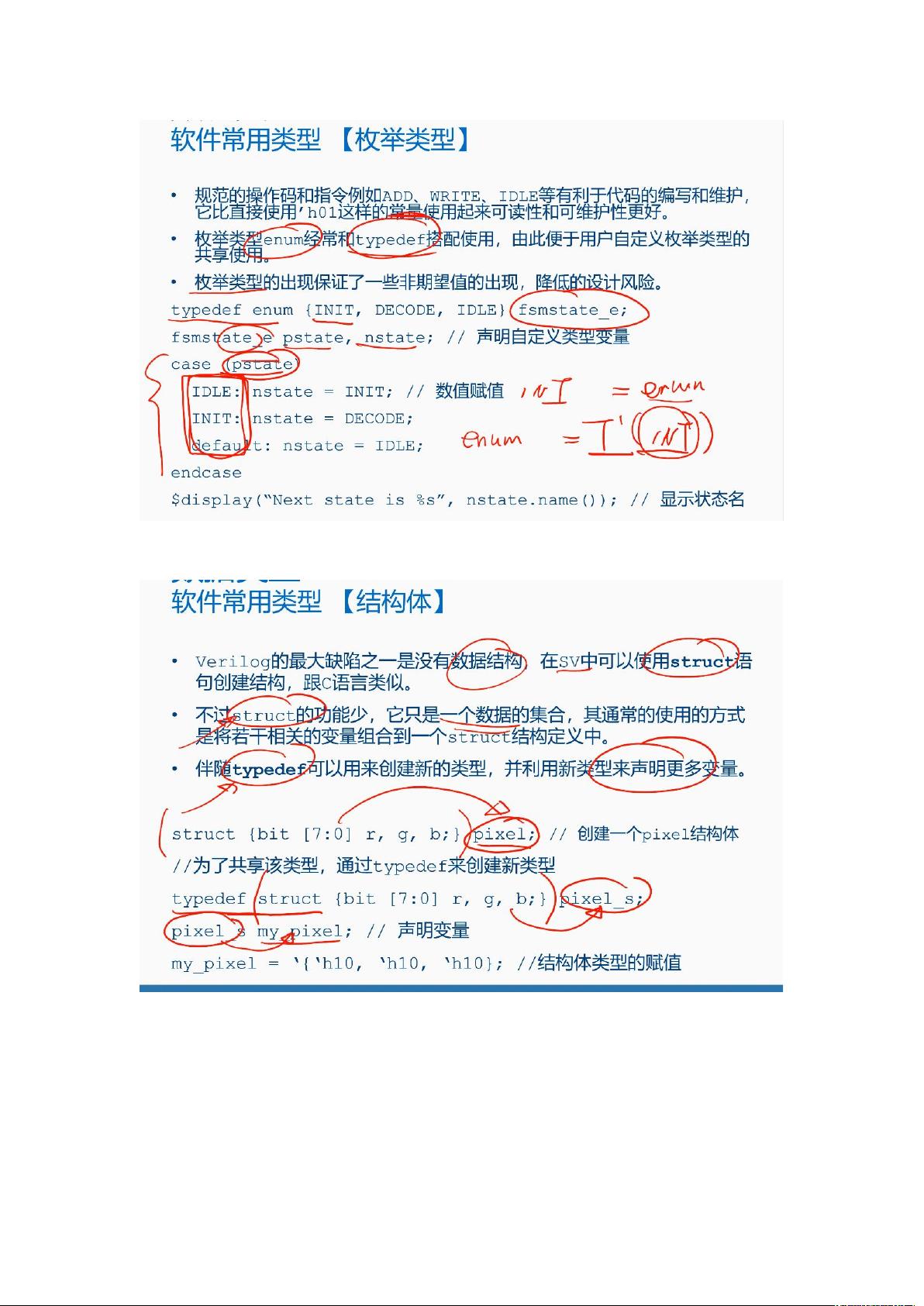

SystemVerilog(SV)是IC验证中常用的高级语言,它允许使用logic代替reg和wire,logic支持四值逻辑(0, 1, X, Z),而wire和reg仅支持二值逻辑(0, 1)。在定义变量时,如Integer和int,虽然它们都是32位,但integer表示四值逻辑,而int表示二值逻辑。在比较不同宽度的变量时,需要了解如何填充0或1。枚举类型可以直接赋值给int,但反向操作需进行类型转换。

在SV中,过程分为automatic和static,未指定时默认为static,即静态变量。Interface可以实例化接口,但不能实例化module,而在Module中则可以实例化两者。可以使用历史命令查看过去的指令。在错误输出方面,$error用于打印错误信息,$display则用于常规显示,打印错误信息时推荐使用$error以确保清晰明了。

枚举打印实验中,$display("%0d")会去除前面的空格和0,整型不能直接赋值给枚举,需要通过类型转换。转换方式有两种,一种是直接赋值如st2=state_t'(1),另一种是使用$cast函数,如$cast(st3,4),推荐使用后者。

在处理结构体时,结构体包含多个数据成员,如addr、data、iswire和id。当结构体包含数组时,使用%p打印默认以十进制形式展示,如t1='{'h10,'h1122_3344,'b1,'h1000}。

这份文档涵盖了IC验证中的硬件加速技术,SystemVerilog的基本语法和高级特性,以及错误处理和数据结构的使用,是学习IC验证的重要参考资料。

2019-05-21 上传

2022-06-20 上传

2019-10-11 上传

2022-11-16 上传

2022-11-02 上传

2022-01-08 上传

2022-12-16 上传

2022-06-20 上传

2021-10-11 上传

Ethan_WC

- 粉丝: 105

- 资源: 10

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析