FPGA设计全流程:Modelsim到Synplify.Pro整合指南

需积分: 10 22 浏览量

更新于2024-12-23

收藏 231KB PDF 举报

"FPGA设计全流程.pdf 是一份详细介绍FPGA设计步骤的文档,内容涵盖了从Modelsim库编译、Xilinx CORE-Generator使用到综合工具Synplify.Pro的运用,以及后续的项目执行和仿真等关键环节。"

FPGA设计全流程涉及到多个软件工具和技术,下面将详细讲解每个阶段:

1. Modelsim编译Xilinx库

Modelsim是一款广泛使用的硬件描述语言(HDL)仿真器,用于验证FPGA设计。在开始设计之前,需要将Xilinx的库文件编译到Modelsim的工作环境中。首先,在Modelsim的安装目录下创建一个名为“XilinxLib”的文件夹,然后在Modelsim中切换到这个目录。接着,找到Xilinx库文件的位置(通常在“$Xilinx/verilog/src”),并将“simprims”、“unisims”和“XilinxCoreLib”这三个库编译到“XilinxLib”中。每个库的编译过程包括在“Compile”菜单中选择库文件,并指定编译目标为新创建的“Xilinx_CoreLib”库。

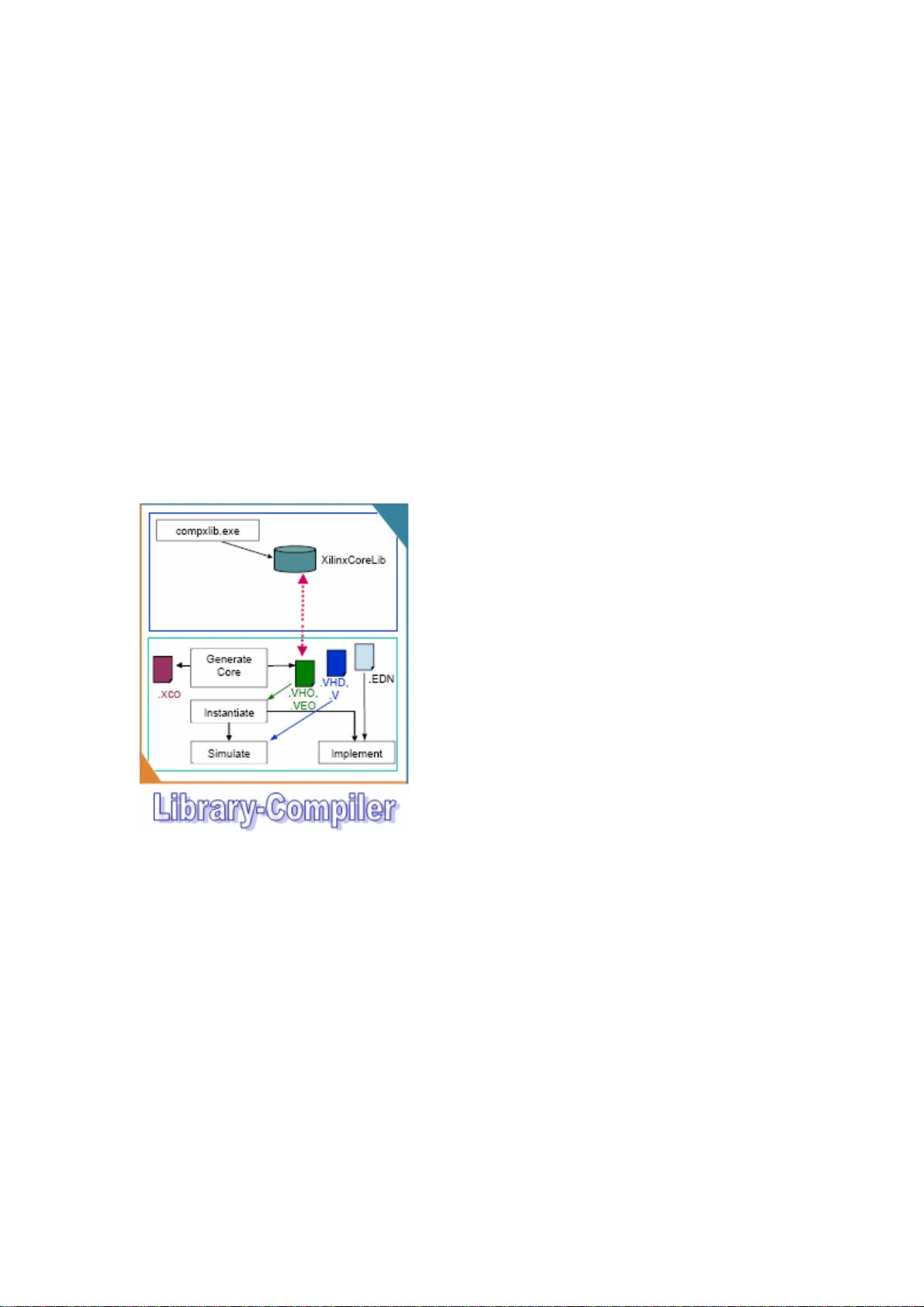

2. 调用Xilinx CORE-Generator

CORE-Generator是Xilinx提供的IP核生成工具,能够帮助设计者快速生成参数化和免费的IP内核。使用CORE-Generator,无论是通过原理图还是HDL,都可以方便地创建和定制IP核。创建IP核的过程包括启动CORE-Generator,选择或配置所需的IP内核参数,然后生成相应的HDL代码或网表。

3. 使用Synplify.Pro综合HDL和内核

Synplify.Pro是一款强大的HDL综合工具,它将设计者的高级HDL代码转换成低级门级网表,适合FPGA的实现。在这个阶段,将从Modelsim编译好的IP核和设计源码导入到Synplify.Pro中进行综合优化。设置综合规则,如面积、速度和功耗的目标,然后运行综合流程,最终得到优化的网表文件。

4. 综合后的项目执行

在Synplify.Pro完成综合后,生成的网表文件需要进一步处理,如约束设置、时序分析等。这通常涉及到使用Xilinx的ISE(Integrated Software Environment)工具。ISE提供了对综合结果的后处理,包括映射、布线和时序分析等功能,以确保设计满足性能和资源的要求。

5. 仿真验证

在将设计下载到FPGA之前,需要进行仿真验证,确保设计的功能正确性。Modelsim可以用来执行功能仿真和时序仿真,检查设计在不同条件下的行为是否符合预期。这包括单元测试、激励生成、覆盖率分析等多个步骤,以确保设计无误。

FPGA设计是一个迭代的过程,可能需要反复进行上述步骤,不断优化设计,直到满足所有性能指标。整个流程中,理解并熟练掌握每个工具的使用方法和设计原则是至关重要的,这将直接影响到FPGA设计的效率和质量。

2011-04-09 上传

420 浏览量

2022-07-11 上传

142 浏览量

2023-02-20 上传

2023-11-05 上传

2023-02-27 上传

2021-07-13 上传

183 浏览量

xiang_jia

- 粉丝: 3

最新资源

- 《ASP.NET 4.5 高级编程第8版》深度解读与教程

- 探究MSCOMM控件在单文档中的兼容性问题

- 数值计算方法在复合材料影响分析中的应用

- Elm插件支持Snowpack项目:热模块重载功能

- C++实现跨平台静态网页服务器

- C#开发的ProgaWeatherHW气象信息处理软件

- Memory Analyzer工具:深入分析内存溢出问题

- C#实现文件批量递归修改后缀名工具

- Matlab模拟退火实现经济调度问题解决方案

- Qetch工具:无比例画布绘制时间序列数据查询

- 数据分析技术与应用:Dataanalys-master深入解析

- HyperV高级管理与优化使用手册

- MTK6513/6575智能机主板下载平台

- GooUploader:基于SpringMVC和Servlet的批量上传解决方案

- 掌握log4j.jar包的使用与授权指南

- 基础电脑维修知识全解析