FPGA数字跑表设计:VHDL实现与电路解析

版权申诉

155 浏览量

更新于2024-07-03

1

收藏 1.83MB PDF 举报

"基于FPGA数字跑表的设计.pdf"

这篇文档是关于基于FPGA(Field-Programmable Gate Array)的数字跑表设计的一份现代电子技术实验报告。设计者利用VHDL(Very-high-speed Integrated Circuit Hardware Description Language)语言进行FPGA的编程,以实现一个功能完备的数字跑表。

在报告中,首先介绍了VHDL语言。VHDL是一种硬件描述语言,用于描述数字系统的结构和行为。它的特点包括强大的表达能力、良好的可读性和可复用性,使得设计者能够清晰地定义硬件电路的行为和结构。VHDL的特点主要体现在它支持数据类型的多样化、结构化编程以及可以描述并行操作,这使得它非常适合于FPGA和ASIC(Application-Specific Integrated Circuit)设计。

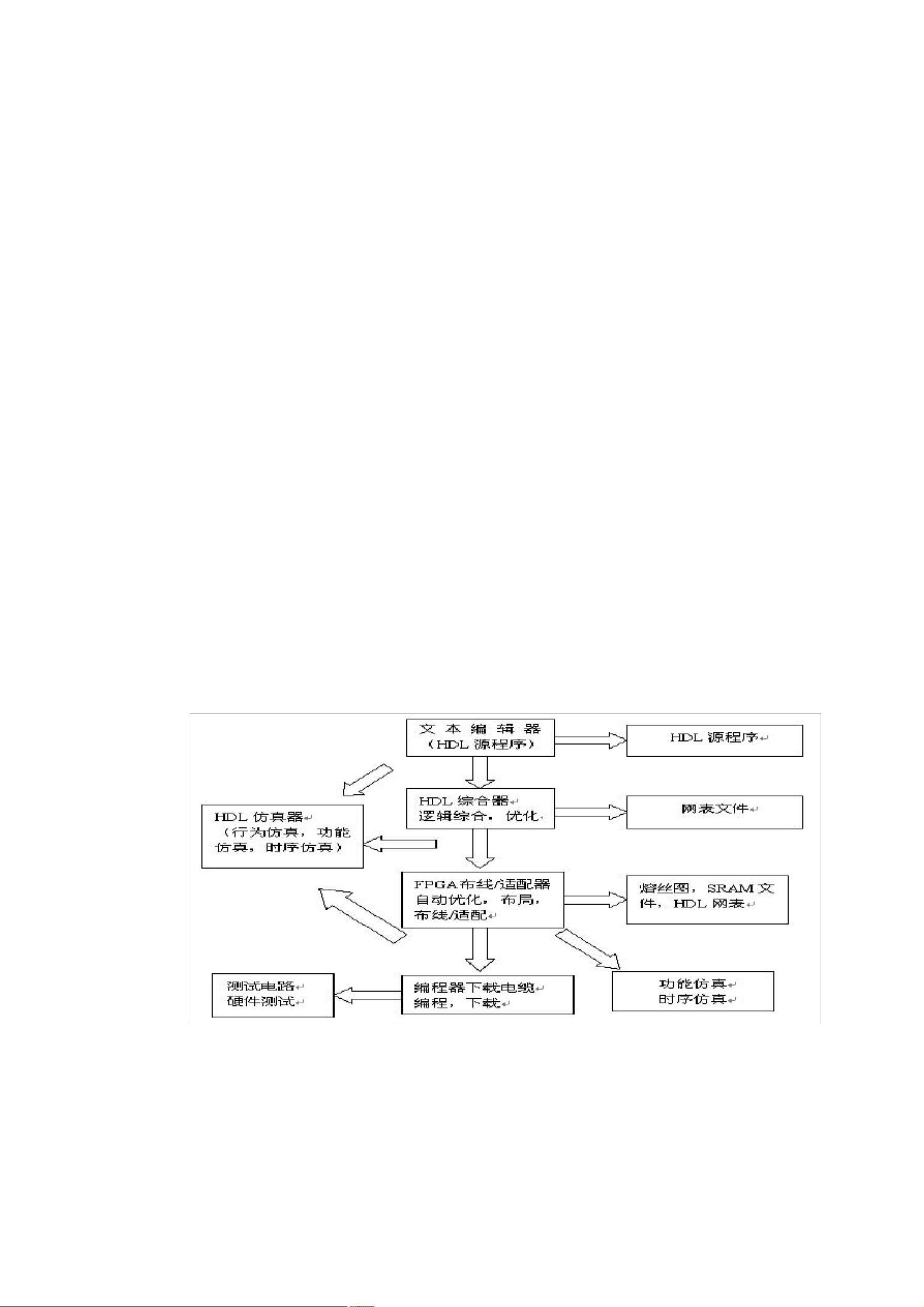

接着,报告详细阐述了FPGA的开发过程。FPGA是一种可编程的逻辑器件,可以通过编程来配置其内部的逻辑单元以实现特定的功能。FPGA设计通常包括以下几个步骤:概念设计、硬件描述语言编程、逻辑综合、布局布线以及功能仿真和硬件验证。实验中使用的开发芯片是XC3S200A,这是一款Xilinx公司的FPGA芯片,具有丰富的逻辑资源和I/O接口,适合用于各种数字系统设计。

然后,报告详细介绍了数字跑表的总体电路设计。设计要求包括实现计时、暂停、复位等功能,系统工作原理基于计数器和控制电路的配合,通过按键进行操作。电路被划分为多个单元,如分频器、按键消抖电路、控制电路、计数器、寄存器、显示模块和使能模块。每个单元都有其特定的作用,例如分频器用于产生稳定的时钟信号,按键消抖电路则解决了因机械按键抖动导致的误触发问题。

在单元电路设计部分,每个模块的功能和实现方法都得到了详细说明。计数器负责时间的累加,寄存器存储当前的时间值,显示模块将这些数值转换为人类可读的格式,并在LED或LCD上显示出来,使能模块则控制不同功能的启动和停止。

顶层设计部分描述了如何将所有单元电路整合到一起,形成完整的数字跑表系统。这一阶段包括顶层VHDL代码编写,分配各模块的输入/输出引脚,并将设计下载到FPGA中进行硬件验证。最后,测试结果和结论部分会对设计的性能进行评估,总结设计过程中的问题和解决方案,以及设计者从这个项目中获得的经验和收获。

这份报告深入浅出地讲解了基于FPGA的数字跑表设计,涵盖了VHDL语言基础、FPGA开发流程、硬件模块设计与集成,对于理解和实践FPGA设计具有很高的参考价值。

542 浏览量

245 浏览量

326 浏览量

121 浏览量

202 浏览量

xxpr_ybgg

- 粉丝: 6803

- 资源: 3万+

最新资源

- api-health-check:Angular项目

- library_system_ruby:图书馆管理系统-Ruby on Rails

- ositestats:网络统计、分析服务器。 PageImpressions、Uniques、流量来源分布、BrowserOs、..

- MyPSD_demo.zip

- P7

- Microsoft Visual Studio Installer Projects

- Abcd PDF - Chrome新标签页-crx插件

- local_library:MDN的“本地库”快速(节点)教程

- PassSlot:使用Mule的PassSlot应用程序

- 员工管理信息系统.rar

- Ameyo | Task + Habit Tracker-crx插件

- T3

- Python训练营

- PUBG引擎源码.7z

- xiaozhao:校园招聘过程中,整理的知识点,包含计算机网络,操作系统,组成原理,Java基础,设计模型等

- Search Keys-crx插件