Verilog流水线CPU设计与冲突解决案例分析

需积分: 0 190 浏览量

更新于2024-08-04

1

收藏 497KB DOCX 举报

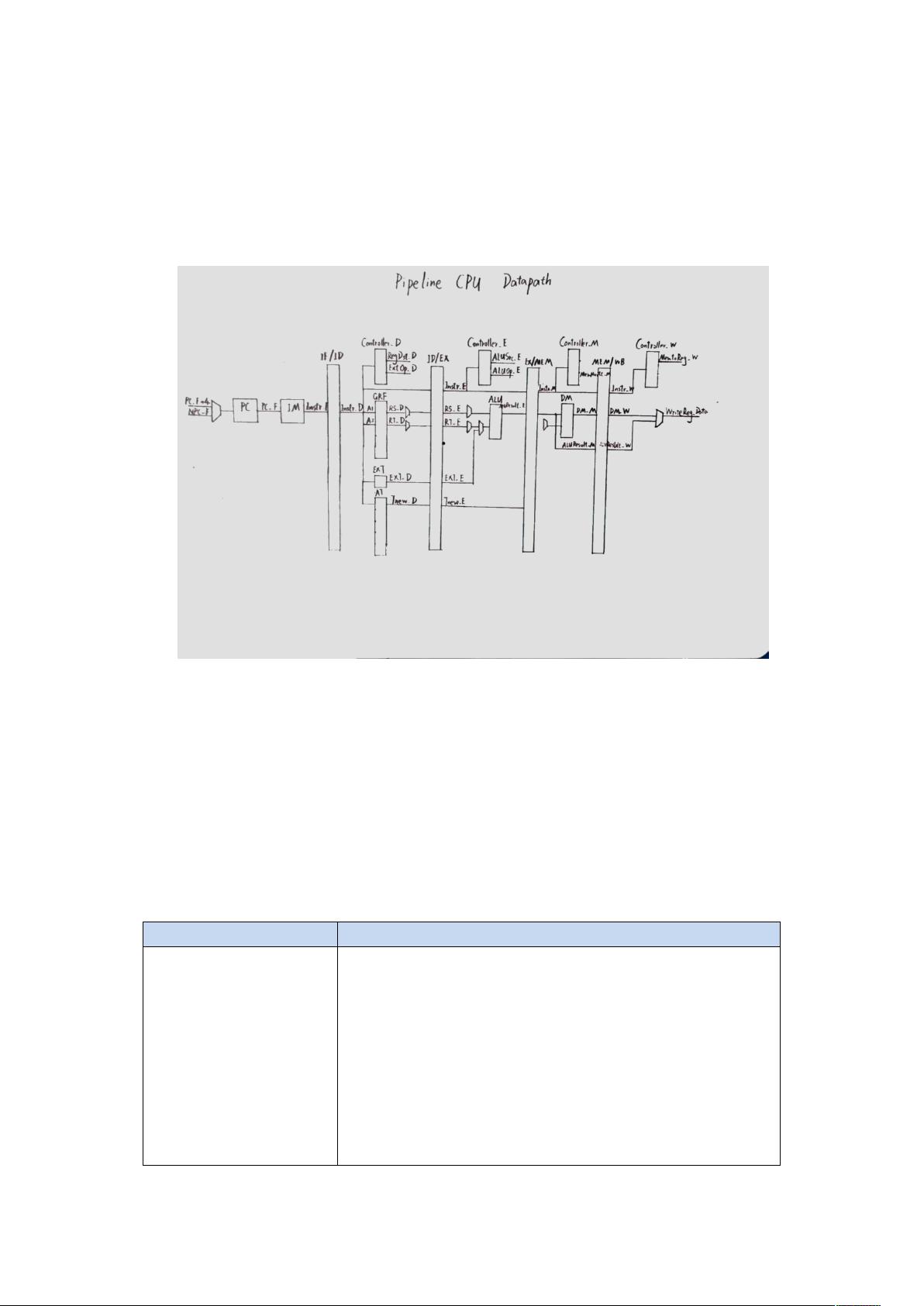

本篇文档是关于计算机组成课程设计的P5部分,主要聚焦于Verilog语言实现的流水线CPU的设计与分析。文档的核心内容围绕着CPU的流水线设计,包括顶层架构、模块划分以及指令处理流程中的关键概念,如解码器、转发信号控制和暂停信号控制。

首先,文档详细解释了流水线的几个关键术语:

- Tuse (Use Time): 指令在D级(数据使用级)时,所需数据必须在多少个时钟周期内准备好。如果Tuse为0,说明数据已计算完成,可通过内部转发机制在不中断流水线的情况下获取结果。

- Tnew (New Time): 指令在某流水级完成计算并能将结果存储回寄存器的时间。Tnew <= Tuse 表明数据可及时提供,可通过转发解决。反之,Tnew > Tuse则可能需要暂停流水线以确保数据的正确性。

接下来,文档提出了思考题,引导学生考虑不同类型的指令组合可能带来的冲突,如R型(读)、I型(立即数)、B型(条件分支,如beq)、load型(加载)、save型(存储,如sw)和jr(跳跃)指令。遇到冲突时,学生被要求描述他们是如何通过手动构造或随机生成测试样本来检测和解决问题的。手动构造时,需要确保覆盖所有可能的指令组合和执行路径,以保证全面测试。而完全随机生成的测试可能存在无法覆盖特定边缘情况的问题。采用连续数据冒险序列等特殊策略结合随机性,能够更有效地进行强度测试。

文档还提供了测试程序示例,使用汇编语言编写了一系列指令,包括ori(无条件或)、addu(加法无符号)、subu(减法无符号)、beq(条件跳转)、sw(存储指令)等,用于演示和测试CPU的流水线功能。这些指令展示了不同类型的指令操作,并在循环结构中模拟了潜在的冲突场景。

总结来说,该文档不仅介绍了计算机组成原理中的流水线CPU设计,还强调了实际操作中的问题解决策略和测试方法,对于理解CPU流水线的工作原理和优化具有重要意义。学生可以根据提供的信息,加深对CPU流水线设计的理解,并在实际项目中灵活应用。

2022-06-27 上传

2021-11-30 上传

2021-02-14 上传

2022-08-03 上传

2022-08-08 上传

2022-07-14 上传

2021-05-08 上传

2022-04-28 上传

zh222333

- 粉丝: 38

- 资源: 296

最新资源

- Python中快速友好的MessagePack序列化库msgspec

- 大学生社团管理系统设计与实现

- 基于Netbeans和JavaFX的宿舍管理系统开发与实践

- NodeJS打造Discord机器人:kazzcord功能全解析

- 小学教学与管理一体化:校务管理系统v***

- AppDeploy neXtGen:无需代理的Windows AD集成软件自动分发

- 基于SSM和JSP技术的网上商城系统开发

- 探索ANOIRA16的GitHub托管测试网站之路

- 语音性别识别:机器学习模型的精确度提升策略

- 利用MATLAB代码让古董486电脑焕发新生

- Erlang VM上的分布式生命游戏实现与Elixir设计

- 一键下载管理 - Go to Downloads-crx插件

- Java SSM框架开发的客户关系管理系统

- 使用SQL数据库和Django开发应用程序指南

- Spring Security实战指南:详细示例与应用

- Quarkus项目测试展示柜:Cucumber与FitNesse实践