Verilog HDL建模秘籍:入门到精通

需积分: 9 47 浏览量

更新于2024-07-09

收藏 17.74MB PDF 举报

Verilog HDL建模篇:探索基础与技巧

Verilog HDL,作为一种广泛应用于FPGA和CPLD设计的高级硬件描述语言,其核心价值在于它的建模能力。"Verilog HDL那些事 - 建模篇 V5.pdf"文档强调了建模在学习过程中的关键地位。建模在Verilog HDL世界中如同乐高积木中的搭建工具,它决定了设计的清晰度、效率和可维护性。

首先,"建模"并非仅仅是模块的简单创建,而是指通过结构化的方式组织和表达设计意图。在学习过程中,新手常遇到的问题是理解不了如何将抽象的概念转化为可编程的代码,这正是缺乏建模技巧的表现。网络上的建议虽然提倡通过阅读他人代码来理解RTL级设计,但这仅是基础,真正的学习应当伴随着对建模的理解和实践。

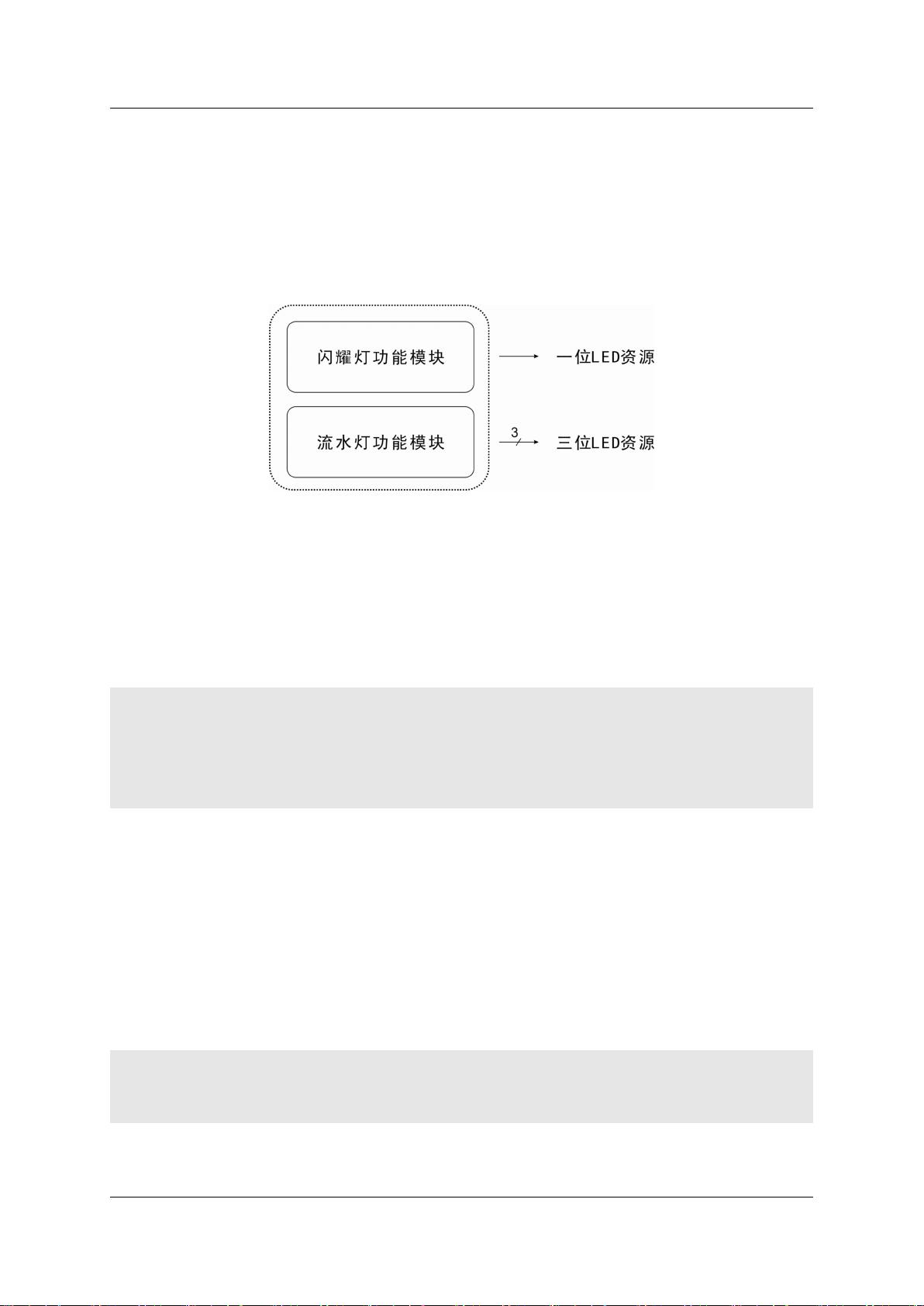

有效的建模技巧包括但不限于模块划分的合理性、接口设计的清晰性、数据流和控制流的可视化以及层次结构的构建。一个好的建模应该使自己的设计易于理解和复用,就像优秀的散文一样,让读者一目了然。忽视建模技巧,就如同只关注语法而不注重文学结构的写作,最终可能导致设计混乱,难以调试和维护。

作者痛惜的是,尽管建模技巧对于理解和设计高质量的Verilog HDL代码至关重要,却往往被初学者轻视,甚至在某些情况下被认为不如时序分析和功能仿真重要。然而,实际上,熟练掌握建模技巧能让设计师在语言表达能力上媲美甚至超越高级编程语言,因为良好的建模能够提高设计的灵活性和可扩展性。

许多初学者在FPGA和Verilog HDL的学习道路上停滞不前,主要障碍就在于他们未能掌握有效的建模方法,也就是所谓的"初级建模"。作者分享的这些技巧,旨在帮助读者跨越这个门槛,实现从理论学习到实际应用的飞跃,从而真正掌握这种强大的设计工具。

理解和运用Verilog HDL的建模技巧是提升FPGA开发能力的关键,它不仅关乎代码的质量,还关系到设计者的职业成长和发展。因此,无论是在学习初期还是进阶阶段,都不能忽视对建模艺术的修炼。

4015 浏览量

303 浏览量

291 浏览量

435 浏览量

238 浏览量

2023-06-13 上传

395 浏览量

168 浏览量

152 浏览量

351 浏览量

qq_24519003

- 粉丝: 0

- 资源: 9

最新资源

- Linux下oracle安装

- 常用软考算法大全内附实例

- 图书馆管理系统 UML 图

- 西门子S7-300编程讲义

- 中国联通(内部质料)

- 高效C++编程技术(Effcient C++ Programming Techniques)

- 利用c++解析XML的书籍

- minigui官方datasheet

- VBA,字符串处理大全

- SAP中创建BAPI笔记.pdf

- Undocumented Windows 2000 Secrets中文版

- TEA5768HL.PDF

- js验证表单大全.doc

- SMD焊接指南.介绍SMD焊接工艺.pdf

- SQL 详细讲解SQL查询优化,希望对大家有帮助

- 指针总结.让你不再害怕指针.doc