VHDL基础教程:语法与特性解析

"这篇资料详细介绍了VHDL的基本语法,非常适合VHDL语言的开发者学习。"

VHDL,全称Very High Speed Integrated Circuit Hardware Description Language,是一种用于电子设计自动化领域的硬件描述语言,广泛应用于数字系统的设计和仿真。VHDL的语言特性使其成为一种强大的工具,能够帮助设计师实现从高层次的系统描述到低层次的门级实现。

VHDL的一个关键特点在于它的多级描述能力。它支持自底向上的设计方法,即从基本逻辑门开始构建电路;同时也支持从顶向下的设计方法,从系统的整体功能出发进行模块化设计。此外,VHDL还允许混合描述,结合结构、行为和数据流三种方式,使得设计过程更加灵活。

设计的基本单位在VHDL中由实体(entity)和结构体(architecture)组成。实体定义了设计单元的输入和输出接口,而结构体则详细描述了单元的功能和实现。为了管理复杂性,VHDL提供了单元(component)、块(block)、过程(procedure)和函数(function)等结构化元素,以及包(package)来封装和复用设计组件。

在数据表示方面,VHDL有常数、信号和变量三种数据对象。每种对象都有特定的数据类型,包括数值类型、逻辑类型、位型和位向量型等。VHDL允许用户定义自己的数据类型,增强了其灵活性和实用性。它是一种强类型语言,确保了数据类型的严谨性。

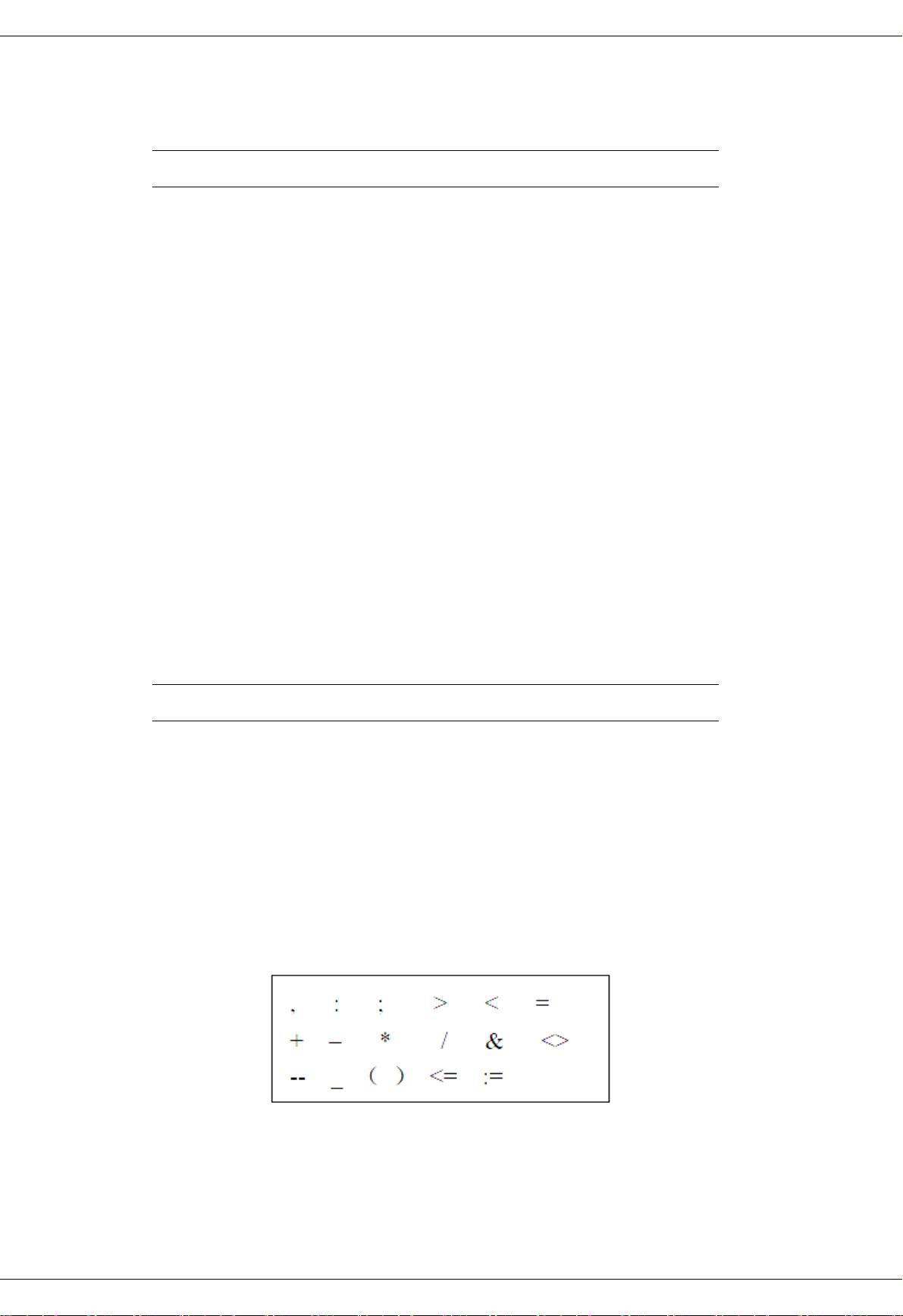

VHDL的语言结构结合了高级编程语言的特性,如IF语句、循环语句等,同时考虑到了数字电路的并行和串行操作。它提供了并行语句(如并行进程)和顺序语句(如赋值语句),能够准确地描述组合电路和时序电路的行为,无论是同步还是异步系统。

学习VHDL语言,不仅需要理解其语法规则,还需要掌握数字逻辑电路的基础知识。通过VHDL,设计师可以更高效地实现和验证数字系统,加速了从设计到实现的过程,并且方便了设计团队之间的交流和合作。

VHDL是一种强大而灵活的硬件描述语言,它的全面性和结构化特性使其在电子设计领域中占据重要地位。对于任何想要进入或深入数字系统设计的人来说,理解和掌握VHDL的基本语法是必不可少的。

2009-07-02 上传

2020-09-20 上传

2024-05-30 上传

2023-07-29 上传

2023-07-31 上传

2023-09-07 上传

2023-09-18 上传

2023-05-13 上传

j1k11

- 粉丝: 3

- 资源: 12

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布