Verilog_HDL实现的交通灯控制器设计

版权申诉

"基于Verilog_HDL的交通灯控制器设计"

本设计旨在利用Verilog HDL语言构建一个交通灯控制器,用于模拟十字路口的交通信号灯操作。该控制器以LED显示交通灯状态,并通过7段数码显示器呈现剩余秒数。设计要求包括主干道和支干道的交替放行,主干道每次放行35秒,支干道放行25秒,黄灯作为过渡,亮5秒,同时支持特殊状态显示,即东西、南北路口同时显示红灯。

设计思路和原理主要围绕十字路口的南北和东西直行交通灯控制。首先,所有方向的红灯亮起作为初始状态,然后按照预设的周期进行状态转换。在主干道绿灯亮时,支干道显示红灯,反之亦然。每个状态转换都伴随着黄灯的5秒过渡。这一过程通过状态机计数法实现,使用Verilog HDL进行描述。

实现方法中,设计者采用文本编辑法编写Verilog代码,利用状态机来控制交通灯的状态变化,并结合计数器来实现时间延迟。系统由实验箱提供的频率信号驱动时钟,两组红黄绿LED模拟实际交通灯,4个7段数码管分别显示两个方向的剩余时间。

在Verilog HDL程序设计部分,整体设计关注于状态之间的转换逻辑。设计了一个三状态的状态机,包括主干道绿灯(状态00)、黄灯过渡(状态01)和支干道绿灯(状态11),以及再次过渡到主干道红灯(状态10)。状态机的真值表和状态转化图清晰地展示了这一逻辑流程,确保了交通灯的正确循环运行。

为了实现控制和显示功能,程序需要设置多个寄存器和计数器,用于存储当前状态和计时。此外,还需要考虑特殊状态的处理,比如在紧急情况下,所有方向的红灯同时亮起。这可能涉及到额外的输入信号和状态判断。

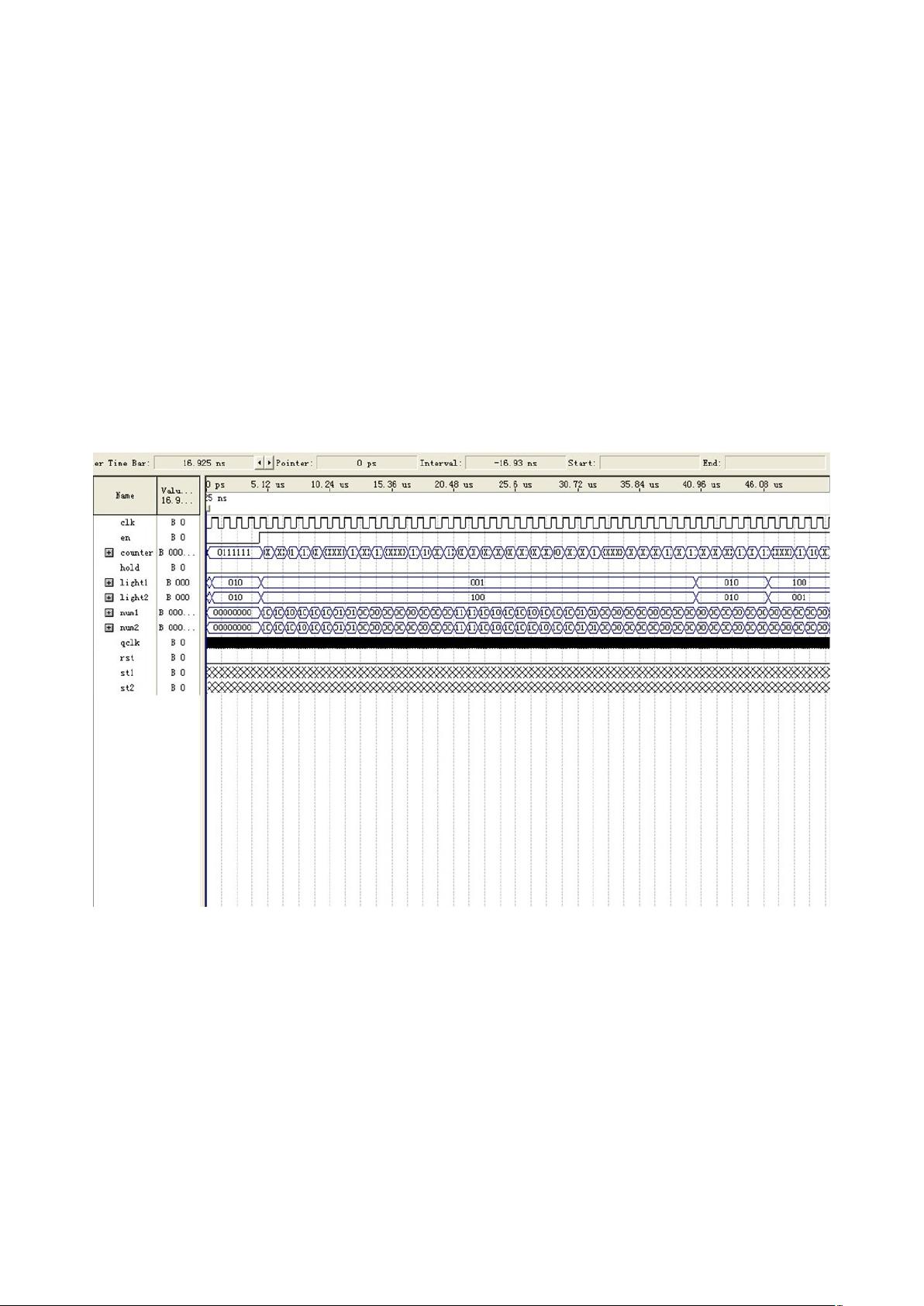

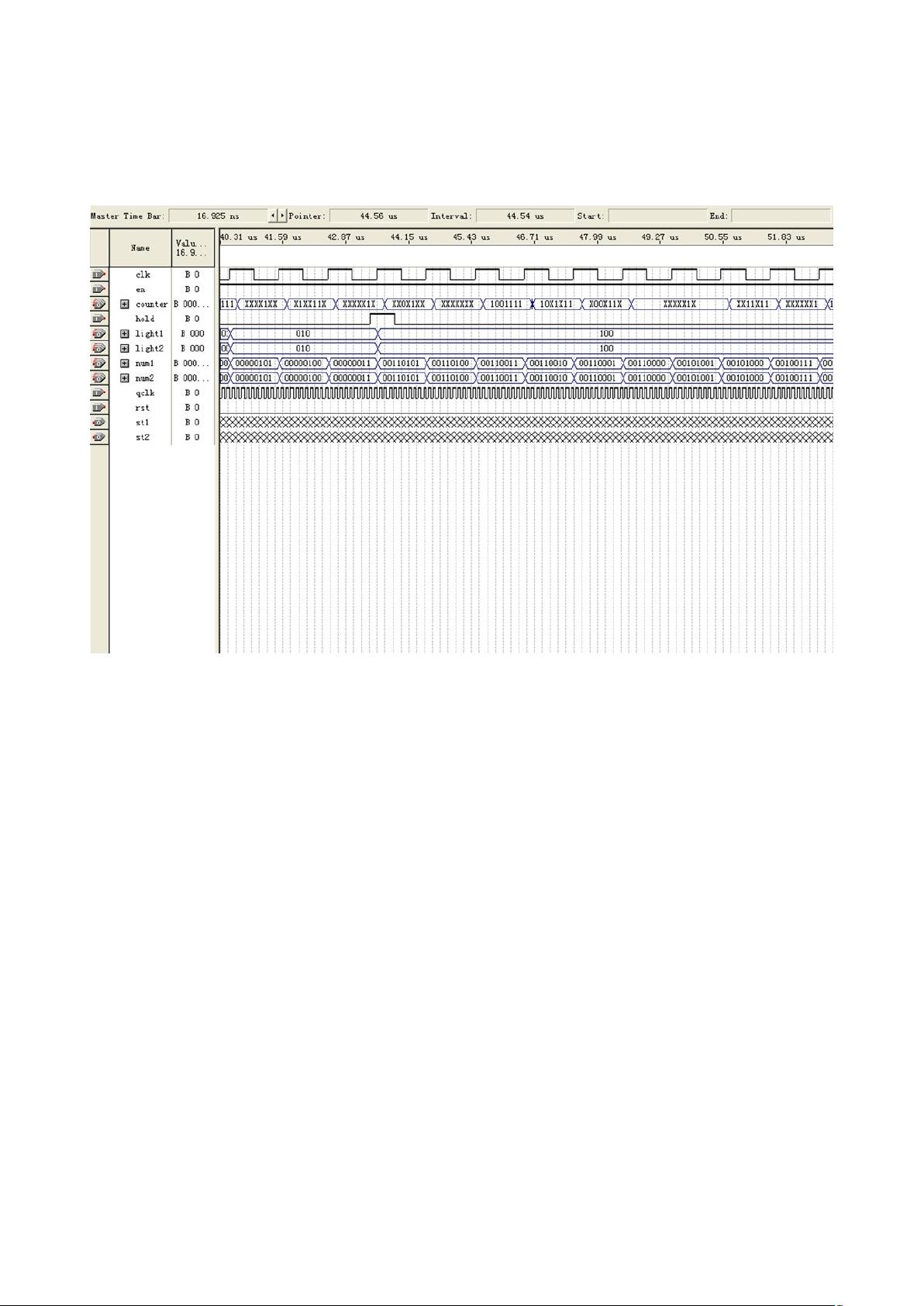

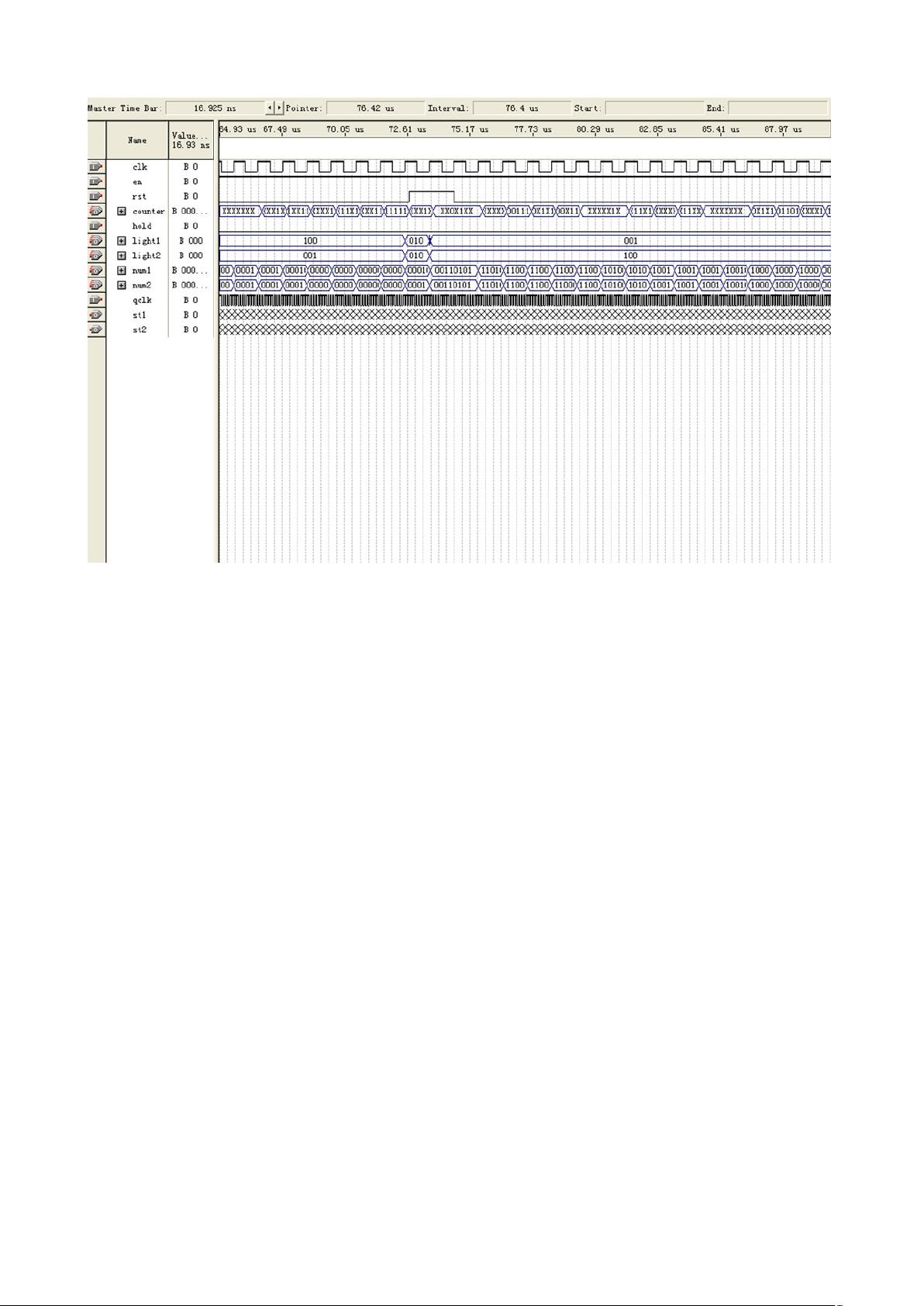

在仿真与硬件调试阶段,设计者会使用波形仿真工具验证代码的正确性,检查状态转换和时间间隔是否符合预期。硬件调试则是在实际电路板上运行程序,确认交通灯控制器在真实环境中的表现。

设计总结部分,设计者会对整个项目进行反思,包括遇到的问题、解决方法以及可能的改进方案。程序清单会列出所有关键的Verilog代码模块,参考资料则提供了相关学习和参考的文献。

基于Verilog HDL的交通灯控制器设计是一个综合性的数字逻辑设计项目,涵盖了状态机设计、时序控制、硬件描述语言编程以及系统级的仿真和验证。它不仅锻炼了设计者的逻辑思维能力,也对实际交通管理系统的运作有了深入的理解。

2022-06-19 上传

2022-06-19 上传

2022-06-21 上传

2022-06-30 上传

2022-07-03 上传

2022-06-21 上传

2021-09-09 上传

2022-07-03 上传

老帽爬新坡

- 粉丝: 98

- 资源: 2万+

最新资源

- NTFS和FAT32的区别.doc

- 双向转发检测BFD技术白皮书

- Vim实用技术-技巧、插件和定制

- 客房管理系统论文—计算机系毕业论文

- ant中文开发指南.pdf

- jsp 转发和重定向的区别(forward sendRedicreat)

- ARM嵌入式WINCE实践教程

- a byte of python-python最佳入门教材

- ARM开发工程师入门秘籍

- LinuxUnix下ODBC的安装、配置与编程.doc

- VC开发MySQL数据库专题

- 香港科大数字图像处理

- UBB语法UBB语法UBB语法

- 数字图像处理基础知识

- DataTable,DataView和DataGrid中一些容易混淆的概念

- 显示系统时钟(汇编)