7系列FPGA与MIG生成DDR2 IP核详解

需积分: 10 39 浏览量

更新于2024-07-21

收藏 14.81MB PDF 举报

"这篇文档是关于Xilinx 7系列FPGA使用Memory Interface Solutions (MIG)生成DDR2 IP核的用户指南,版本1.7,发布于2012年10月16日。该指南详细介绍了如何配置和使用DDR2内存接口,以及相关的IP功能。"

在Xilinx 7系列FPGA中,Memory Interface Solutions (MIG) 是一种强大的工具,用于简化高速存储器接口如DDR2的设计过程。DDR2(Double Data Rate Second Generation Synchronous Dynamic Random-Access Memory)是一种广泛应用的内存技术,它提供比第一代DDR更高的数据传输速率,同时降低了功耗。

MIG IP核是Xilinx提供的预配置硬件模块,能够帮助设计者快速、准确地集成DDR2内存到FPGA设计中。以下是一些关键知识点:

1. **DDR2内存结构**:DDR2内存工作在同步模式下,数据在时钟的上升沿和下降沿同时传输,从而实现双倍数据速率。它具有多个Bank,可以并行处理多个读写请求,提高系统性能。

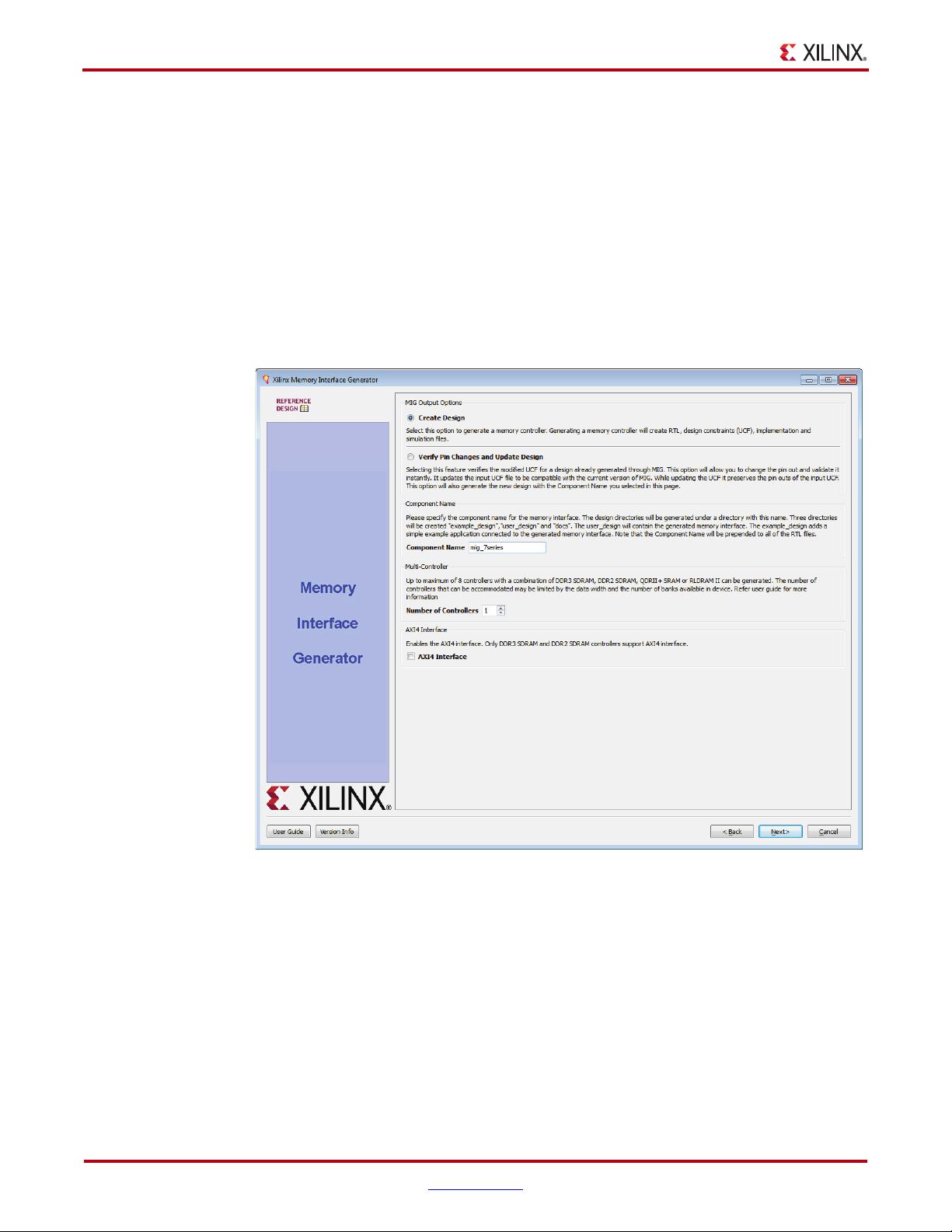

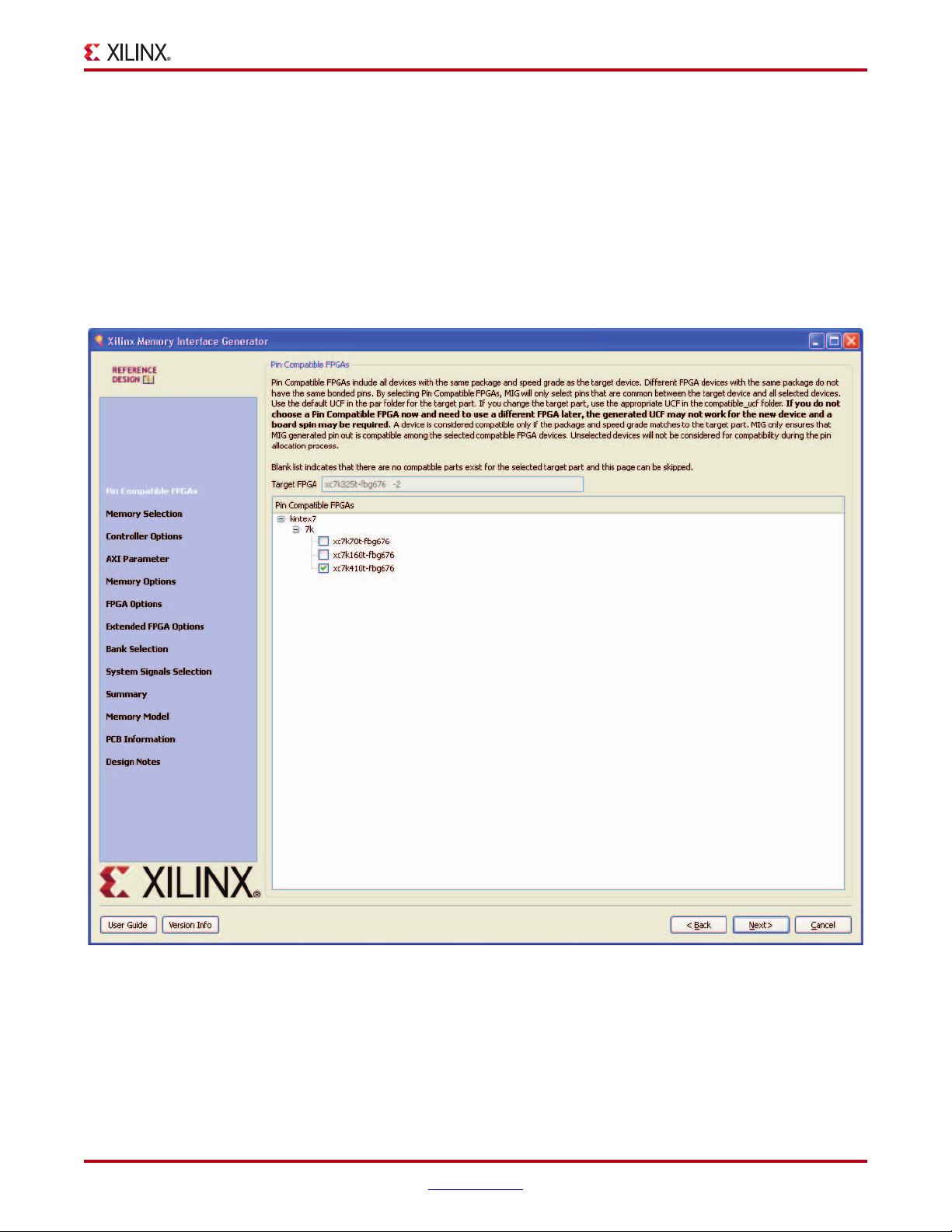

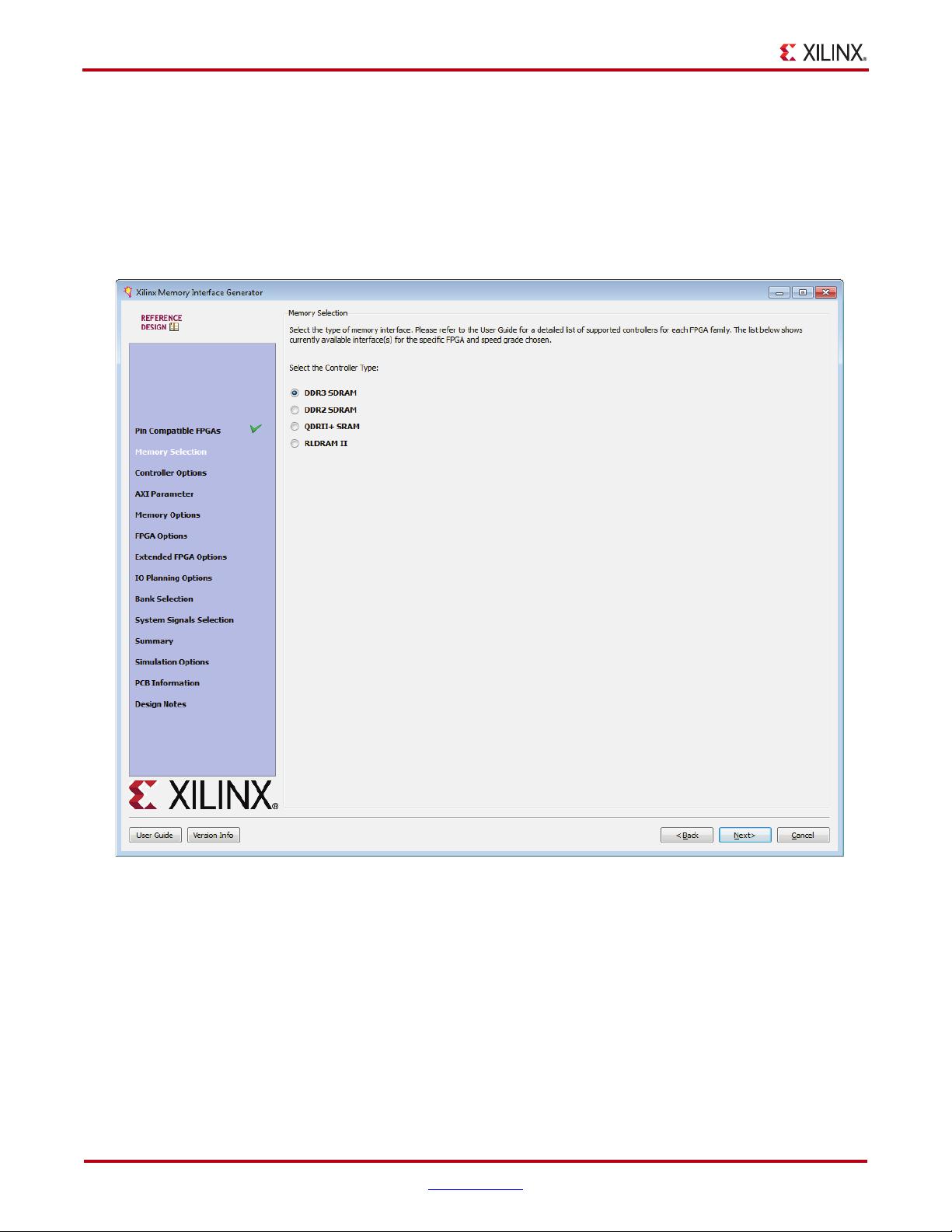

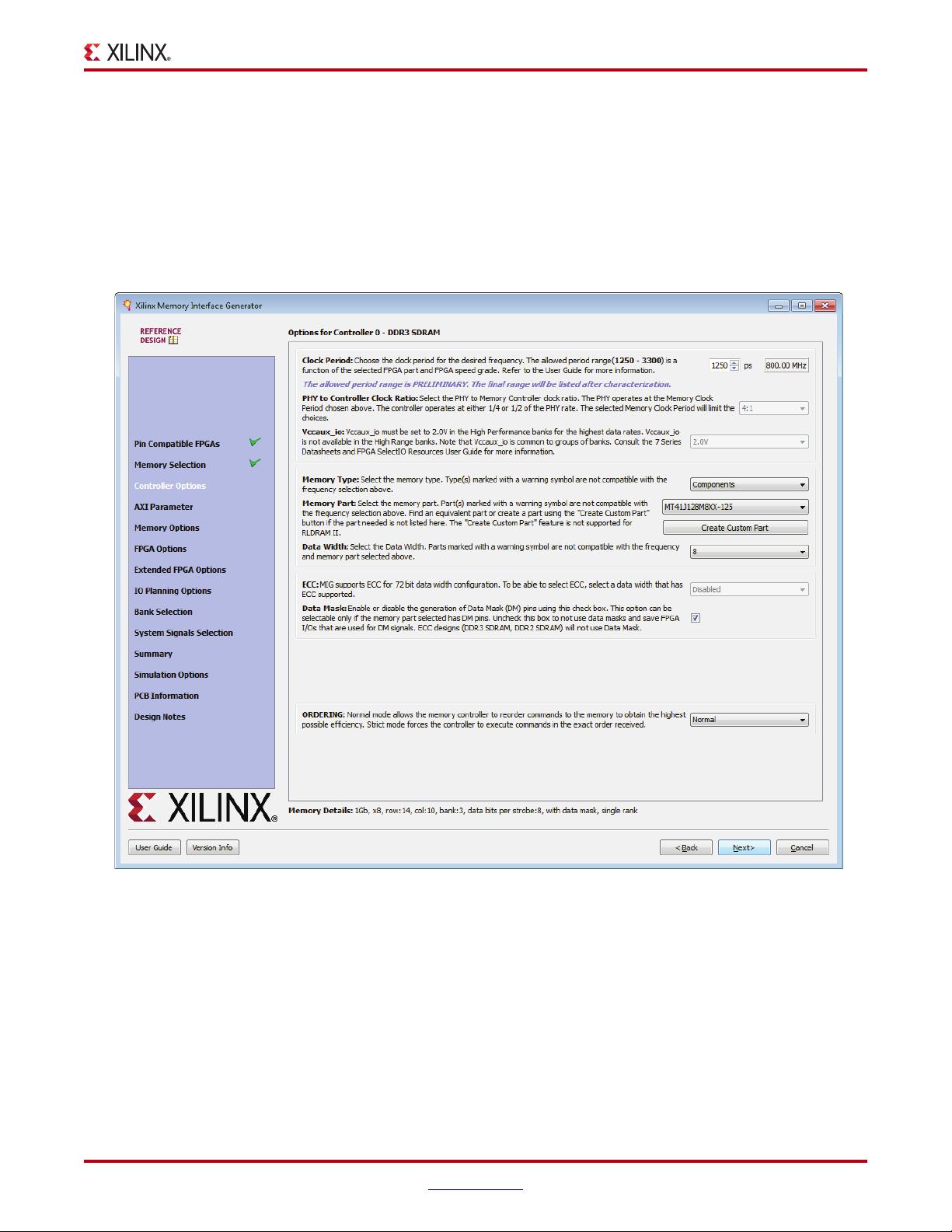

2. **MIG流程**:使用MIG时,设计者首先需要配置IP核,指定内存类型(DDR2)、速度等级、总线宽度等参数。然后,MIG会生成必要的逻辑、时序控制器和PHY层,以确保与DDR2内存芯片的正确通信。

3. **IP配置**:在Xilinx ISE或Vivado设计环境中,设计者通过MIG GUI进行配置,包括选择内存芯片型号、设置时序参数、定义接口宽度等。这些设置会影响到整个系统的性能和兼容性。

4. **接口设计**:MIG生成的IP核提供了与FPGA内部逻辑交互的AXI4-Stream接口,允许高效的数据传输。设计者需要根据应用需求,适配这个接口到他们的系统设计中。

5. **时序约束**:为了确保设计满足内存的时序要求,MIG会自动生成必要的时序约束,这些约束在综合和实现阶段必须被正确应用。

6. **物理层(PHY)**:MIG还包括一个经过优化的PHY层,处理与DDR2内存芯片的物理接口,包括信号调理、时钟恢复和数据对齐等功能。

7. **调试和验证**:MIG提供了一套全面的测试平台和波形视图,便于设计者在硬件上进行功能验证和性能调试。

8. **性能优化**:MIG支持多种优化选项,如预读取、写后读等,以提高内存带宽和降低访问延迟。

9. **合规性和标准**:Xilinx MIG符合JEDEC DDR2标准,确保了设计的兼容性和可靠性。

Xilinx 7Series_MIS提供了详细的步骤和工具,使得开发者能够在7系列FPGA中有效地集成DDR2内存,实现了高性能、低延迟的系统设计。然而,重要的是要注意,虽然MIG大大简化了设计过程,但设计者仍需理解内存接口的基本原理和相关时序要求,以确保设计的成功。同时,Xilinx声明其提供的材料“AS IS”,不承担任何明示或暗示的保修责任。在实际使用中,设计者应遵循文档中的指导,并充分测试以避免潜在的问题。

2020-04-13 上传

2020-08-03 上传

2018-08-17 上传

2017-12-22 上传

2023-07-31 上传

2018-11-23 上传

2023-04-08 上传

2020-03-17 上传

2018-09-21 上传

狂风无语

- 粉丝: 0

- 资源: 1

最新资源

- nostalgebraist-autoresponder:tumblr bot nostalgebraist-autoresponder的代码

- Multi depth pointer based Triangle List:非常快速且可动态扩展的数据结构。-开源

- Android参考源码-调用Android中的软键盘.zip

- ynapshot-CPETT,c语言测试源码是否正确,c语言

- baseballmatching2

- grunt-boilerplate:Grunt、LESS 和 include-replace 满足您所有的 webapp 开发需求

- ibc2k1.github.io

- xryuseix.github.io

- Android应用源码之悬浮窗 监视内容.zip项目安卓应用源码下载

- zbzh,c语言二十一点游戏源码简单,c语言程序

- Vier Hack-crx插件

- BowlingScoreCalculator

- Kinematics-Web-Calculator

- OFDM 频谱:带 GI 的 OFDM 频谱。-matlab开发

- ChatApplication

- No roses-crx插件