华为FPGA设计高级技巧:Xilinx篇

需积分: 10 8 浏览量

更新于2024-07-23

收藏 2.94MB PDF 举报

"FPGA设计高级篇 - 华为FPGA设计中的问题与解决方案,Xilinx篇"

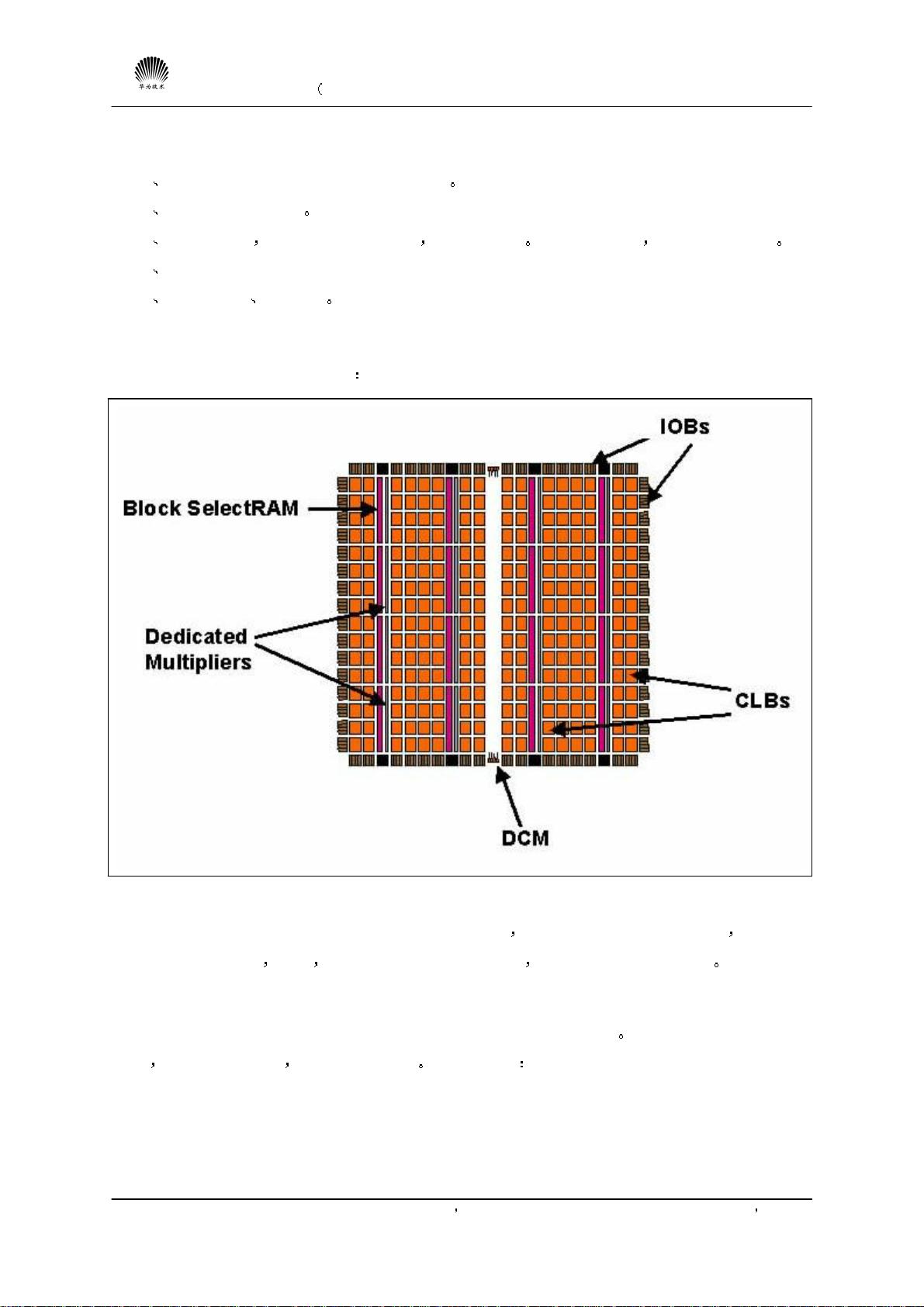

本资料详细介绍了在华为FPGA设计过程中遇到的问题及其解决策略,专注于提高设计效率和性能。文档涵盖了一系列高级技巧,针对Xilinx FPGA器件,如VirtexII系列。以下是一些关键知识点:

1. **设计技巧**:

- **加法电路选择**:讨论了串行进位与超前进位的差异,以及如何通过合理选择加法电路来优化速度和面积。

- **括号处理**:指出使用圆括号可以更有效地处理多个加法器,从而减少逻辑级数,提高速度。

- **IF语句和Case语句**:探讨了这两种控制结构对速度和面积的影响。

2. **内存资源**:

- **分布式RAM (Distributed RAM)** 和 **块RAM (BlockRAM)**:解释了它们的使用和配置,以及如何根据需求选择合适的内存类型。

- **LUT作为组合逻辑**:详细解剖了LUT(查找表)如何被配置以实现高效的组合逻辑电路。

3. **时钟资源**:

- **全局时钟 (GlobalClock)**、**CLKMUX** 和 **DCM (Digital Clock Manager)**:阐述了这些时钟资源的作用,以及如何利用它们来管理时钟信号,优化设计速度和同步性。

4. **IOB (Input/Output Buffer)** 结构:

- **IOB结构**、**SelectI/O** 和 **DCI (Differential Clock Input)**:深入介绍了输入输出缓冲器的不同方面,包括如何配置它们以适应不同的I/O需求。

5. **乘法器资源**:讨论了如何有效利用FPGA内部的乘法器,以提高计算效率。

6. **逻辑单元**:

- **CLB (Configurable Logic Block)**、**Slice**、**LUT**、**SRL (Shift Register LUT)**、**MUXFX** 和 **CarryLogic/ArithmeticLogicGates**:解析了这些基本逻辑单元的结构和功能,以及如何优化它们的使用。

7. **编码风格**:

- 对比了不同编码风格(如ASIC结构与FPGA结构)对设计性能的影响,并给出了最佳实践建议。

8. **BlockSelectRAM** 内部结构的解剖:提供了关于如何高效使用这种存储资源的见解。

整体来看,这份文档旨在帮助开发者深入理解Xilinx FPGA的架构,从而在设计过程中做出更明智的决策,优化速度、面积和功耗。对于想要提升FPGA设计能力的人来说,这份资料提供了宝贵的实战经验和指导。

2024-01-16 上传

2023-08-10 上传

2023-05-14 上传

2023-07-17 上传

2023-07-14 上传

2023-08-09 上传

2023-06-14 上传

放飞的梦

- 粉丝: 0

- 资源: 10

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性