Transition (d): The CPU does an atomic read-

modify-write operation on a data item that was

not present in its cache. It transmits a “read

invalidate”, receiving the data via a “read re-

sponse”. The CPU can complete the transition

once it has also received a full set of “invalidate

acknowledge” responses.

Transition (e): The CPU does an atomic read-

modify-write operation on a data item that was

previously read-only in its cache. It must trans-

mit “invalidate” messages, and must wait for a

full set of “invalidate acknowledge” responses be-

fore completing the transition.

Transition (f): Some other CPU reads the cache

line, and it is supplied from this CPU’s cache,

which retains a read-only copy. This transition

is initiated by the reception of a “read” message,

and this CPU responds with a “read response”

message containing the requested data.

Transition (g): Some other CPU reads a data item

in this cache line, and it is supplied either from

this CPU’s cache or from memory. In either case,

this CPU retains a read-only copy. This tran-

sition is initiated by the reception of a “read”

message, and this CPU responds with a “read re-

sponse” message containing the requested data.

Transition (h): This CPU realizes that it will soon

need to write to some data item in this cache

line, and thus transmits an “invalidate” message.

The CPU cannot complete the transition until

it receives a full set of “invalidate acknowledge”

responses. Alternatively, all other CPUs eject

this cache line from their caches via “writeback”

messages (presumably to make room for other

cache lines), so that this CPU is the last CPU

caching it.

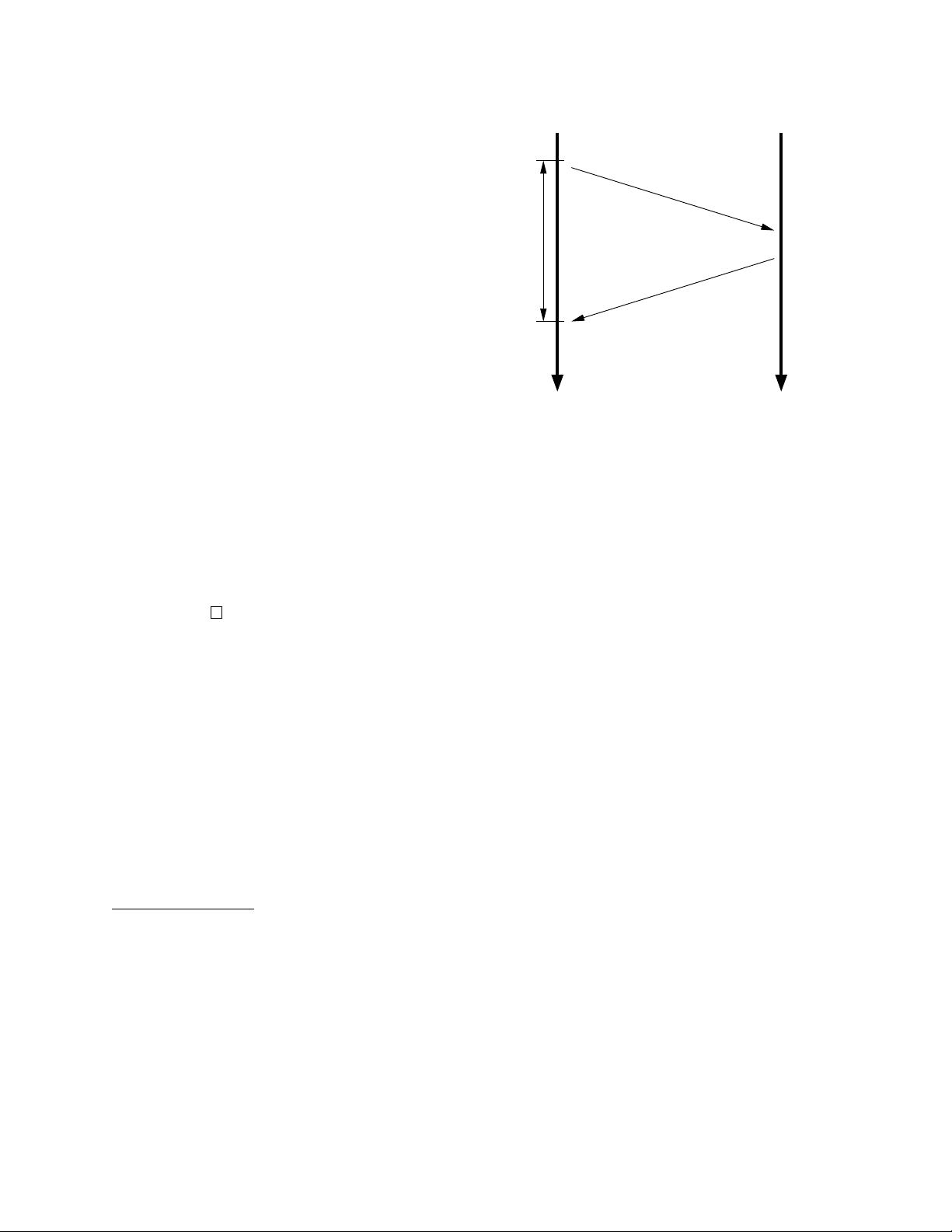

Transition (i): Some other CPU does an atomic

read-modify-write operation on a data item in a

cache line held only in this CPU’s cache, so this

CPU invalidates it from its cache. This transi-

tion is initiated by the reception of a “read in-

validate” message, and this CPU responds with

both a “read response” and an “invalidate ac-

knowledge” message.

Transition (j): This CPU does a store to a data

item in a cache line that was not in its cache,

and thus transmits a “read invalidate” message.

The CPU cannot complete the transition until it

receives the “read response” and a full set of “in-

validate acknowledge” messages. The cache line

will presumably transition to “modified” state

via transition (b) as soon as the actual store com-

pletes.

Transition (k): This CPU loads a data item in

a cache line that was not in its cache. The

CPU transmits a “read” message, and completes

the transition upon receiving the corresponding

“read response”.

Transition (l): Some other CPU does a store to a

data item in this cache line, but holds this cache

line in read-only state due to its being held in

other CPUs’ caches (such as the current CPU’s

cache). This transition is initiated by the recep-

tion of an “invalidate” message, and this CPU

responds with an “invalidate acknowledge” mes-

sage.

Quick Quiz 4: How does the hardware handle the

delayed transitions described above?

2.4 MESI Protocol Example

Let’s now look at this from the perspective of a cache

line’s worth of data, initially residing in memory at

address 0, as it travels through the various single-line

direct-mapped caches in a four-CPU system. Table 1

shows this flow of data, with the first column show-

ing the sequence of operations, the second the CPU

performing the operation, the third the operation be-

ing performed, the next four the state of each CPU’s

cache line (memory address followed by MESI state),

and the final two columns whether the corresponding

memory contents are up to date (“V”) or not (“I”).

Initially, the CPU cache lines in which the data

would reside are in the “invalid” state, and the data

is valid in memory. When CPU 0 loads the data at

5