VHDL设计:序列检测器实现与QuartusII仿真实战

下载需积分: 9 | DOC格式 | 1.49MB |

更新于2024-07-26

| 162 浏览量 | 举报

本实验指导书主要围绕电子设计自动化(EDA)技术以及VHDL语言展开,目标是通过实际项目来培养学生对VHDL编程的理解和应用能力。具体涉及以下几个关键知识点:

1. **实验背景**:VHDL是一种硬件描述语言(HDL),在EDA(电子设计自动化)中扮演着重要角色,用于设计和实现数字电路。学生需要利用QuartusII软件进行VHDL设计和仿真,这是一款流行的FPGA/CPLD开发工具。

2. **实验内容与目标**:

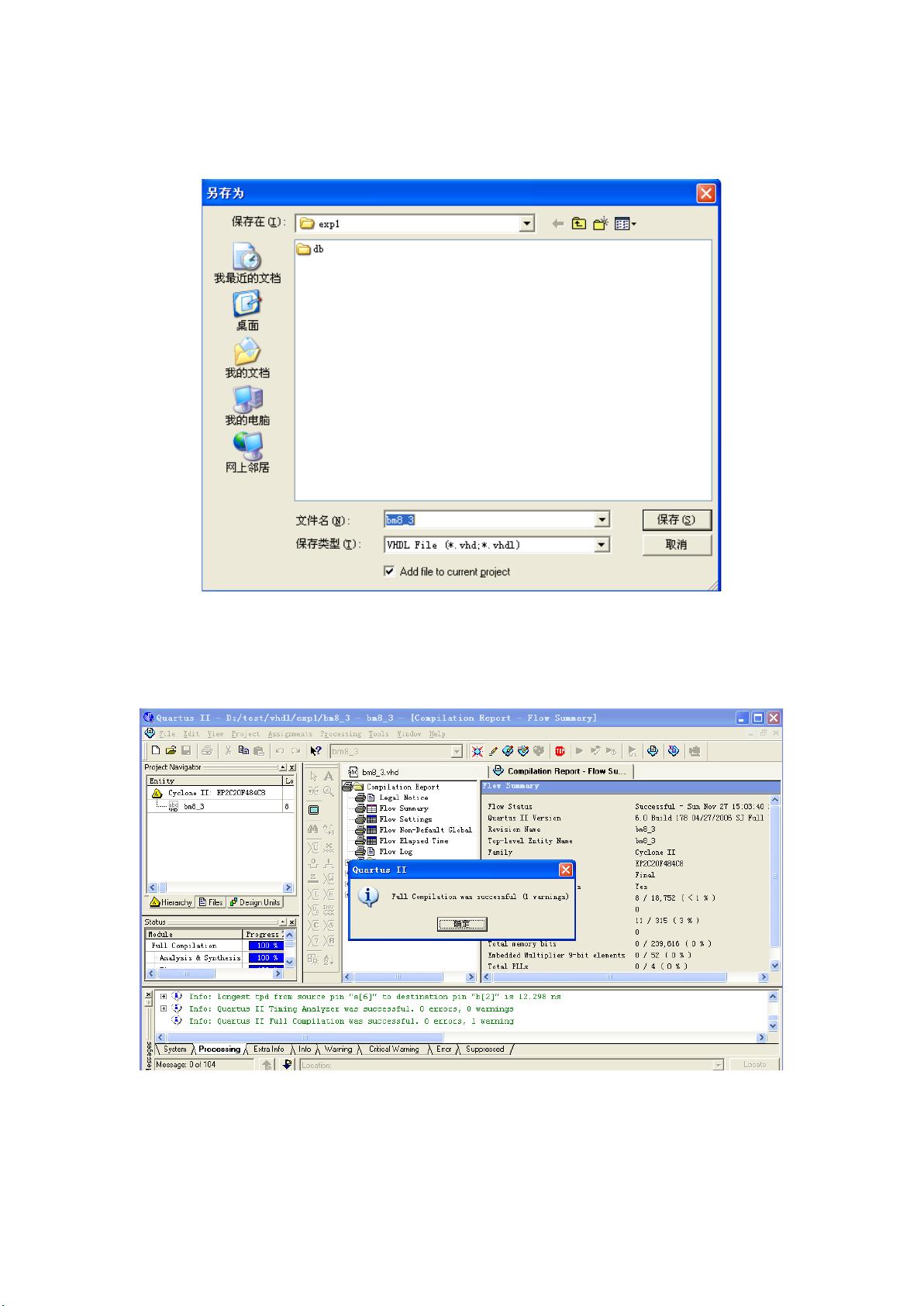

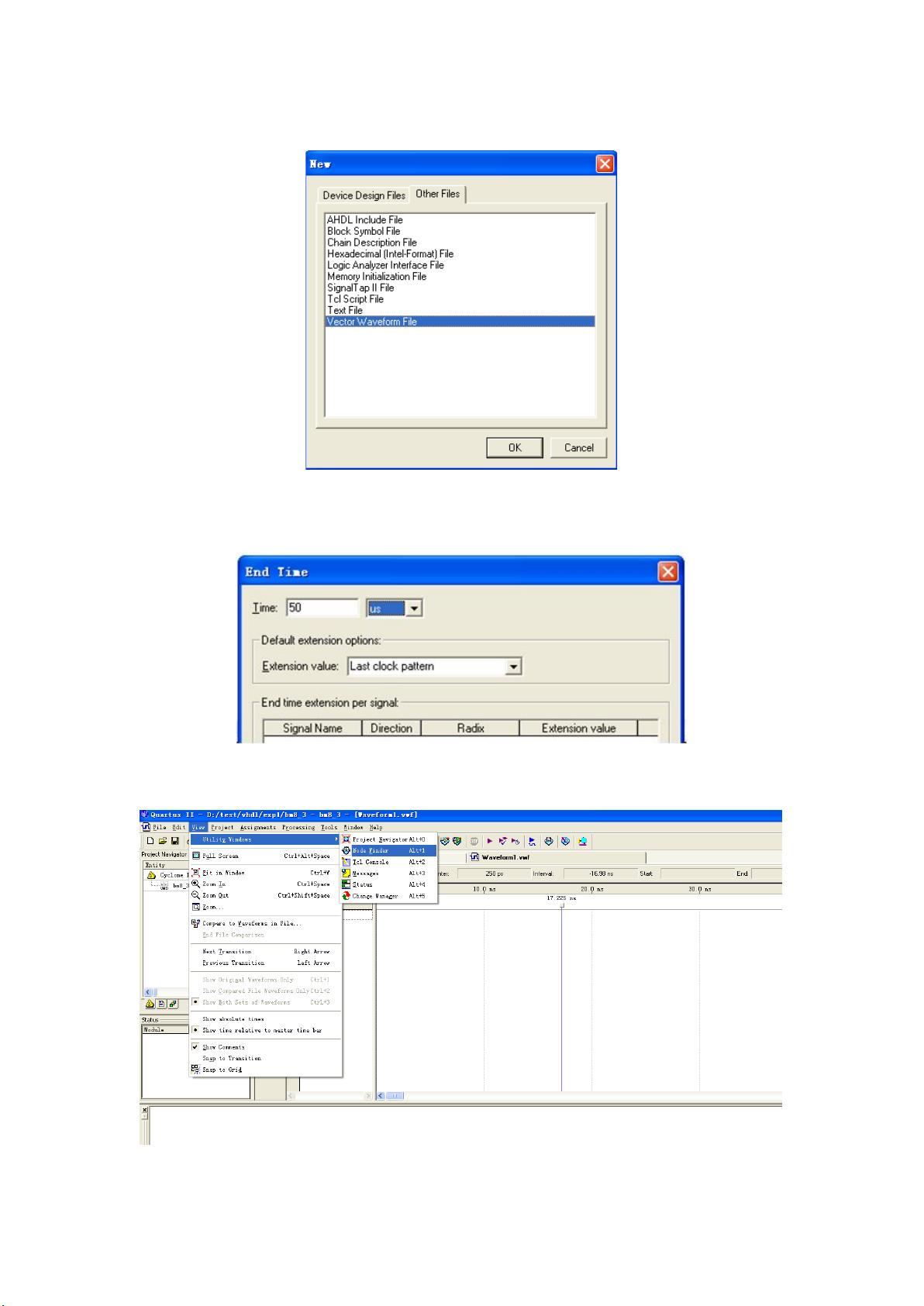

- 实验一:实验环境和平台的建立,重点在于熟悉QuartusII的VHDL设计流程,通过设计和仿真8-3编码器来掌握基本的VHDL编写和调试方法。

- 后续的实验逐级递进,包括组合逻辑电路设计、多层次设计,以及时序逻辑电路设计,如分频器、通用移位寄存器、数码管扫描显示和正弦信号发生器的设计,这些都涵盖了基本的数字电路设计技巧和高级设计技术。

- 最后,实验十中的“序列检测器”设计任务,要求学生用VHDL实现一个能够检测连续串行码(1110010)的逻辑电路,输出对应的状态,进一步提升时序逻辑设计的能力。

3. **编码器与加法器基础**:实验中提到的编码器,是将多路输入转换为单一输出的逻辑电路,如8-3编码器和10-4编码器,它们是数字逻辑设计中的基础组件。全加器则是能处理加法和进位的更复杂组件,由半加器和或门构成,是设计更高级电路的关键部分。

4. **实验步骤**:每个实验都包括明确的步骤,如创建工程、编写VHDL文件、设置可调用元件、编译和仿真,这些步骤展示了实际设计过程中的实践操作。

5. **软件工具**:使用Altera Quartus II作为实验环境,它提供了全面的VHDL开发工具链,包括文本设计、编译、综合、配置和仿真等功能。

通过这个系列的实验,学生不仅能掌握VHDL编程,还能了解和实践EDA技术的基本应用,培养电路设计和逻辑思维能力。同时,通过实际项目,他们可以深入理解数字电路的工作原理,提升实际操作技能。

相关推荐

o0YouYou0o

- 粉丝: 0

最新资源

- Vue.js波纹效果组件:Vue-Touch-Ripple使用教程

- VHDL与Verilog代码转换实用工具介绍

- 探索Android AppCompat库:兼容性支持与Java编程

- 探索Swift中的WBLoadingIndicatorView动画封装技术

- dwz后台实例:全面展示dwz控件使用方法

- FoodCMS: 一站式食品信息和搜索解决方案

- 光立方制作教程:雨滴特效与呼吸灯效果

- mybatisTool高效代码生成工具包发布

- Android Graphics 绘图技巧与实践解析

- 1998版GMP自检评定标准的回顾与方法

- 阻容参数快速计算工具-硬件设计计算器

- 基于Java和MySQL的通讯录管理系统开发教程

- 基于JSP和JavaBean的学生选课系统实现

- 全面的数字电路基础大学课件介绍

- WagtailClassSetter停更:Hallo.js编辑器类设置器使用指南

- PCB线路板电镀槽尺寸核算方法详解