微纳电子器件复习关键:等比例缩小定律、CMOS问题与高k栅介质

需积分: 50 60 浏览量

更新于2024-07-17

2

收藏 11.08MB DOCX 举报

"微纳电子器件期末考试复习思考题涵盖了微纳电子器件的重要概念和技术,如等比例缩小定律(CE律、CV律、QCE律)、CMOS器件的热量问题、MOS绝缘层减薄的影响、EOT概念、高k金属栅极(HKMG)的引入、窄沟道效应、热载流子效应、源漏穿通和次开启抑制、迁移率退化和漂移速度饱和、小尺寸MOS器件阈值电压的影响、漏工程、沟道工程、栅工程、SOI技术、3D集成、TSV技术以及多种封装技术如MCP、3D IC、SIP、SOP和SOC。此外,还涉及了碳纳米管和引线电迁移现象。"

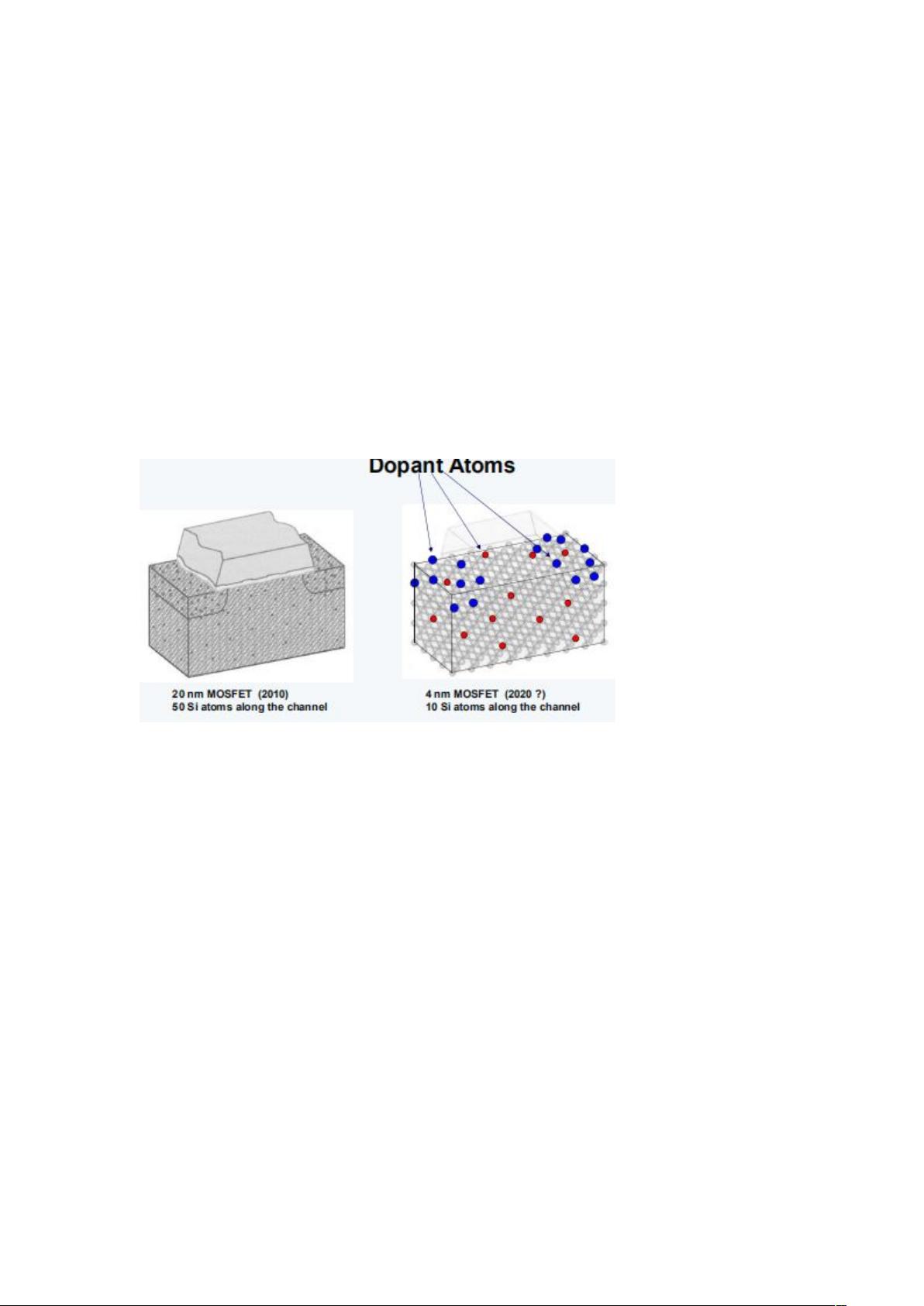

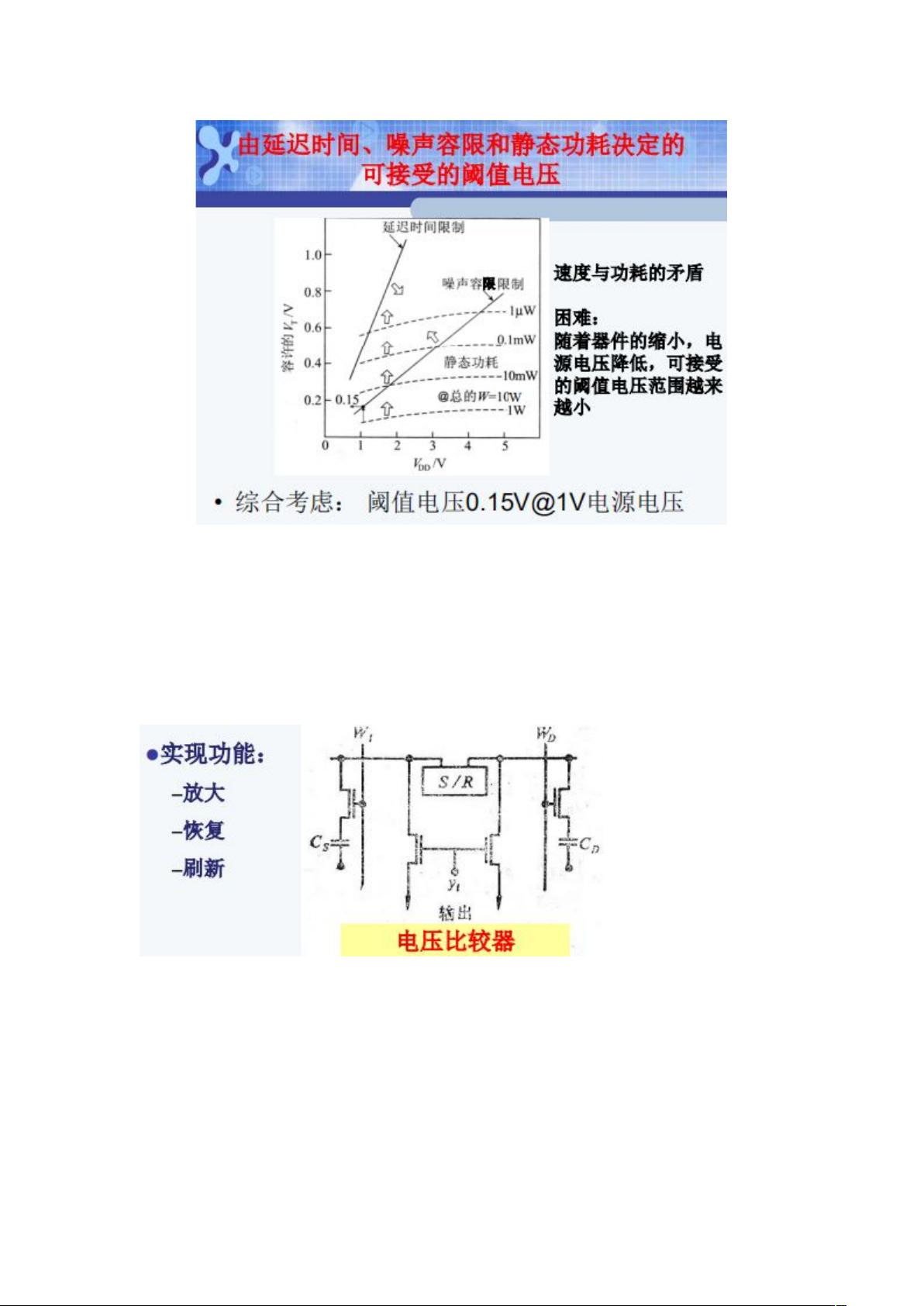

微纳电子器件是现代电子技术的核心,其发展依赖于器件尺寸的持续缩小。等比例缩小定律(Scaling-down)是摩尔定律(MORE定律)的基础,主要包括CE律、CV律和QCE律。CE律主张保持内部电场不变,通过缩小器件尺寸提高性能,但会面临阈值电压降低和源漏耗尽区宽度无法缩小等问题。CV律则保持电源电压和阈值电压不变,适用于较大型器件,但对短沟道器件效果不佳。QCE律则是对CE和CV律的补充。

CMOS器件的"Heat death"是指随着器件尺寸减小,发热问题加剧,影响芯片的稳定性和寿命。随着MOS器件绝缘层减薄,泄漏电流增加,导致功耗上升和器件寿命缩短,同时多晶硅栅耗尽和反型层量子化效应使得栅电容下降,等效氧化层厚度(EOT)增加。

EOT是衡量高k材料栅介质性能的关键参数,当高k材料与传统SiO2达到相同电容时,EOT用于比较。随着技术进步,传统SiO2栅介质变得过薄,引入高k金属栅极(HKMG)以解决直隧道效应和其他性能问题,通过增大栅介质物理厚度来维持电荷控制能力。

缩小的器件尺寸也带来了引线延迟问题,需要通过优化布线设计和采用新型封装技术(如TSV、MCP、3D IC、SIP、SOP和SOC)来克服。这些技术促进了更高密度和更快的电路集成。

此外,纳米尺度MOS器件的物理效应,如窄沟道效应,会影响载流子迁移率和漂移速度,导致性能饱和。为了解决这些问题,研究者实施了漏工程、沟道工程和栅工程,以优化器件性能。SOI(Silicon-on-Insulator)技术利用绝缘层隔离沟道,减少短沟道效应,提高器件性能。

微纳电子器件的复习涵盖了众多关键技术点,对于理解和掌握现代电子技术至关重要,尤其对于应对期末考试或从事相关研究的人员,这些都是必不可少的知识。

2019-07-11 上传

2021-09-18 上传

2023-02-23 上传

2023-02-23 上传

2022-12-15 上传

2022-12-06 上传

weixin_41222105

- 粉丝: 0

- 资源: 9

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析