TMS320VC5509A DSP驱动的JPEG视频压缩系统详解

163 浏览量

更新于2024-08-30

收藏 473KB PDF 举报

在现代信息技术领域,嵌入式微处理器中的数字信号处理器(DSP)因其灵活性、高速性和易于嵌入式应用的特点,被广泛应用于复杂算法处理,尤其是在数字视频图像压缩系统中。本文主要探讨的是基于TMS320VC5509A型DSP的JPEG视频压缩系统的设计和实现。

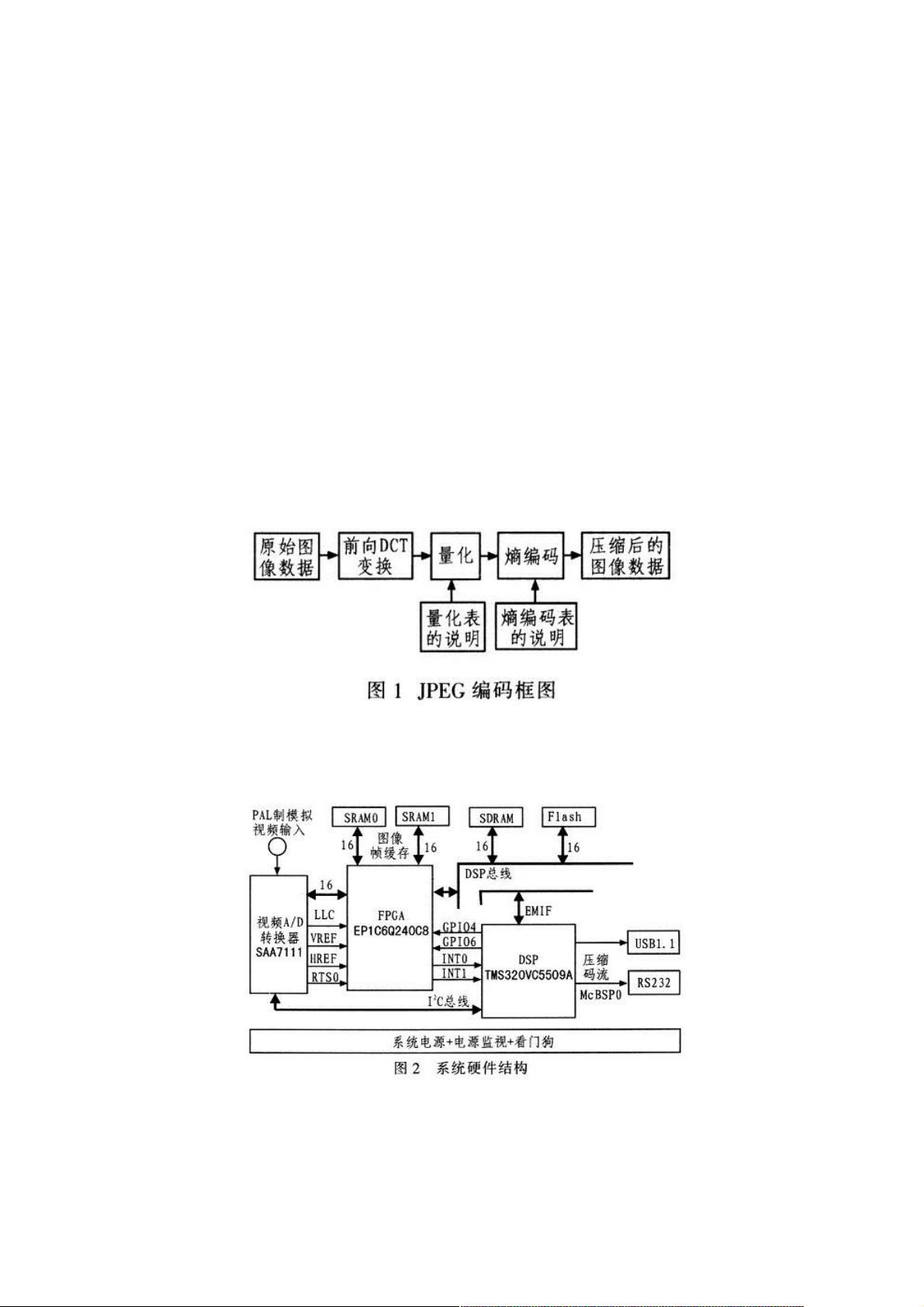

JPEG (Joint Photographic Experts Group) 是一种静止图像的压缩编码标准,它采用了离散余弦变换(DCT)技术。JPEG标准提供了几种编码模式,如基本系统、递增模式和无失真编码模式,以适应不同的应用场景和传输需求。基本系统采用顺序扫描图像,适合实时处理;递增模式则按图像细节从粗到细编码,适用于对清晰度有要求的场景;而无失真编码模式确保重建图像与原始图像完全一致,主要用于对图像质量要求极高的场合。

文章的核心部分着重介绍了硬件系统设计,该视频压缩系统设计包括TMS320VC5509A DSP作为中央处理器,SDRAM作为外置数据存储器,Flash用作程序存储器,用于系统启动。此外,系统还包括模拟摄像头、视频A/D转换器、FPGA(现场可编程门阵列)以及相关的存储和控制模块。FPGA在这里主要负责地址译码、隔行运算以及数字图像的暂存,通过选择Altera公司Cyclone系列的EPIC6Q240C8型FPGA,可以最大化利用器件的I/O引脚资源。

视频采集电路方面,文章提到了Philips公司的SAA7111高性能视频A/D转换器,这款芯片集成了模拟前端、数字视频编码器和多种功能,如多制式数字解码器、亮度/对比度/饱和度控制等,能够高效地将模拟视频信号转化为16位的数字信号,满足后续的处理和压缩要求。

基于TMS320VC5509A DSP的JPEG视频压缩系统实现了JPEG编码的高效处理,结合了硬件选型的优势,确保了图像的实时采集、预处理和压缩,同时兼顾了成本效益和性能优化,是嵌入式图像处理系统的一个典型实例。这一系统不仅适用于IPTV(交互式网络电视)和VoIP(语音-over-IP)等通信领域,也广泛应用于其他需要实时视频压缩的场合。

2020-10-20 上传

2020-11-10 上传

点击了解资源详情

2020-08-29 上传

2020-10-21 上传

2021-04-16 上传

2020-07-30 上传

2020-08-13 上传

2008-12-14 上传

weixin_38673235

- 粉丝: 3

- 资源: 912

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜