高压功率运算放大器输入级设计:JFET差分对套筒式共源共栅电路

174 浏览量

更新于2024-08-31

收藏 404KB PDF 举报

"本文介绍了一种适用于高压功率运算放大器的输入级电路设计,采用p沟道JFET组成的差分对套筒式共源共栅结构,具有低偏置电流、低失调电压、高共模抑制比等特点,并通过共集-共射负载提升电压增益。"

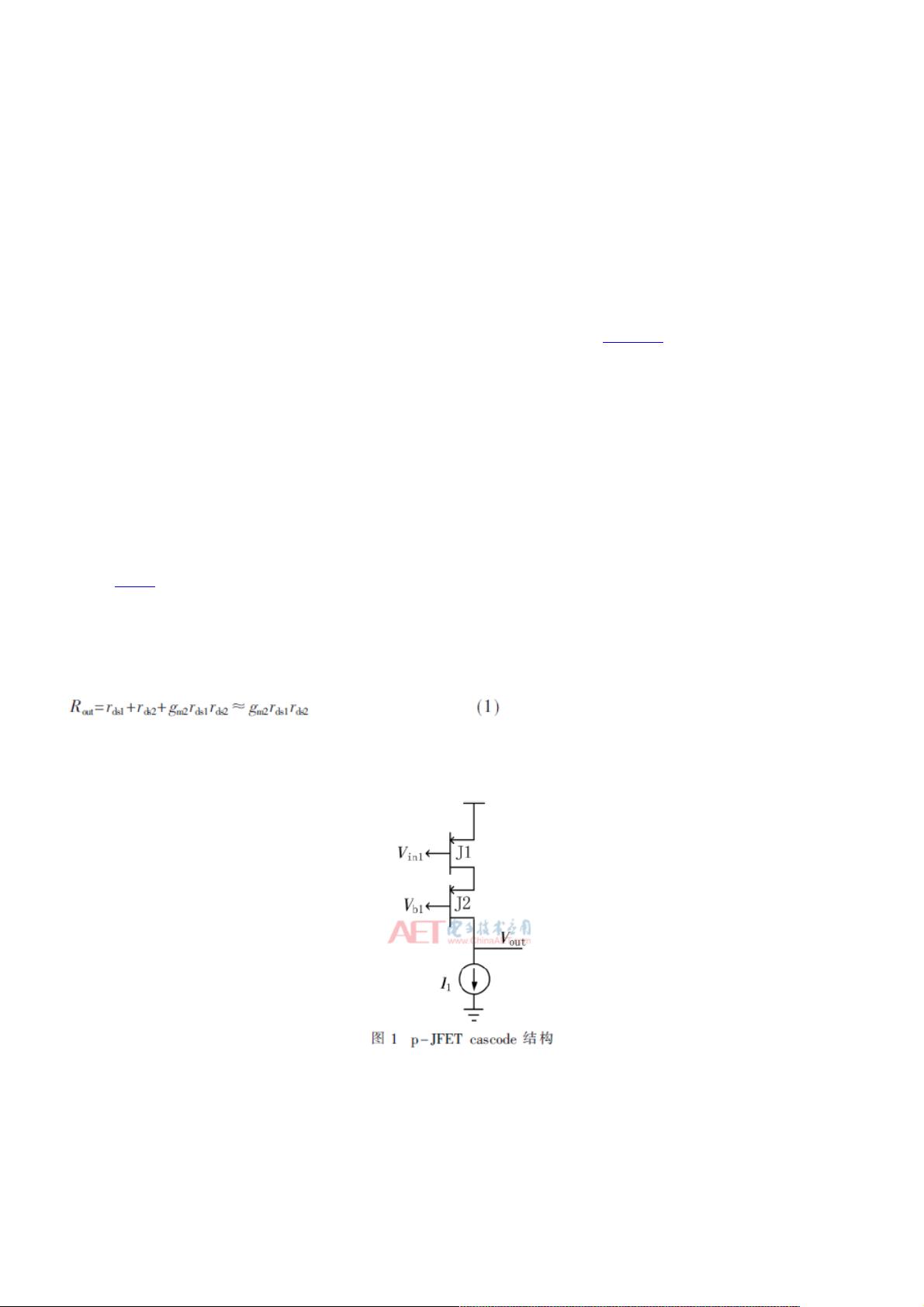

本文探讨了在高压大功率运算放大器应用中的输入级电路设计,特别是在需要高电压驱动能力的工业、汽车、航空等领域的关键需求。传统的共极-共射(CC-CE)结构在高压环境下可能导致较高的功耗。因此,作者提出了一种创新设计,利用70V高压双极型工艺,结合p沟道结型场效应晶体管(JFET)的差分对套筒式共源共栅结构,解决了这一问题。

差分对套筒式共源共栅结构的优势在于其能够显著降低输入偏置电流,同时减少失调电压和失调电流,从而提高了电路的线性度和稳定性。这种结构还具备高共模抑制比,意味着电路对共模信号的抑制能力强,能够更准确地放大所需的差分信号。为了进一步优化性能,输入级电路采用了共集-共射(CC-CE)作为负载,这种结构不仅减轻了负载对输入级的影响,还能提升电路的电压增益。

Spectre仿真结果显示,该输入级电路的性能出色,输入偏置电流仅为20pA,失调电压低至0.11mV,失调电流为0.57fA,这意味着在实际操作中,电路能保持高度的精度。此外,连接负载后的增益可达89dB,单位增益带宽达到8.13MHz,证明了其在高频应用中的适用性。

这种设计的创新之处在于将CMOS集成运算放大器中的差分套筒式共源共栅结构与高压双极型工艺相结合,成功应用于高压大功率运算放大器领域。这种结合不仅保留了原有结构的优点,还克服了传统双极型CC-CE结构的功耗问题,为高压运算放大器的设计提供了新的思路。

该设计为高压大功率运算放大器输入级提供了一个高性能、低功耗的解决方案,有望在多种工业和工程应用中发挥重要作用,提高系统的整体效率和精度。通过采用JFET的差分对套筒式共源共栅结构并配合优化的负载配置,电路的性能得到了显著提升,满足了对高压大功率运算放大器的严格要求。

2011-07-22 上传

389 浏览量

183 浏览量

208 浏览量

261 浏览量

405 浏览量

250 浏览量

115 浏览量

178 浏览量

weixin_38657139

- 粉丝: 9

最新资源

- 易二维码签到系统:会议活动签到解决方案

- Ceres库与SDK集成指南:C++环境配置及测试程序

- 深入理解Servlet与JSP技术应用与源码分析

- 初学者指南:掌握VC摄像头抓图源代码实现

- Java实现头像剪裁与上传的camera.swf组件

- FileTime 2013汉化版:单文件修改文件时间的利器

- 波斯语话语项目:实现discourse-persian配置指南

- MP4视频文件数据恢复工具介绍

- 微信与支付宝支付功能封装工具类介绍

- 深入浅出HOOK编程技术与应用

- Jettison 1.0.1源码与Jar包免费下载

- JavaCSV.jar: 解析CSV文档的Java必备工具

- Django音乐网站项目开发指南

- 功能全面的FTP客户端软件FlashFXP_3.6.0.1240_SC发布

- 利用卷积神经网络在Torch 7中实现声学事件检测研究

- 精选网站设计公司官网模板推荐