计算机原理:存储器与CPU连接及地址分配

版权申诉

52 浏览量

更新于2024-07-03

收藏 915KB PPT 举报

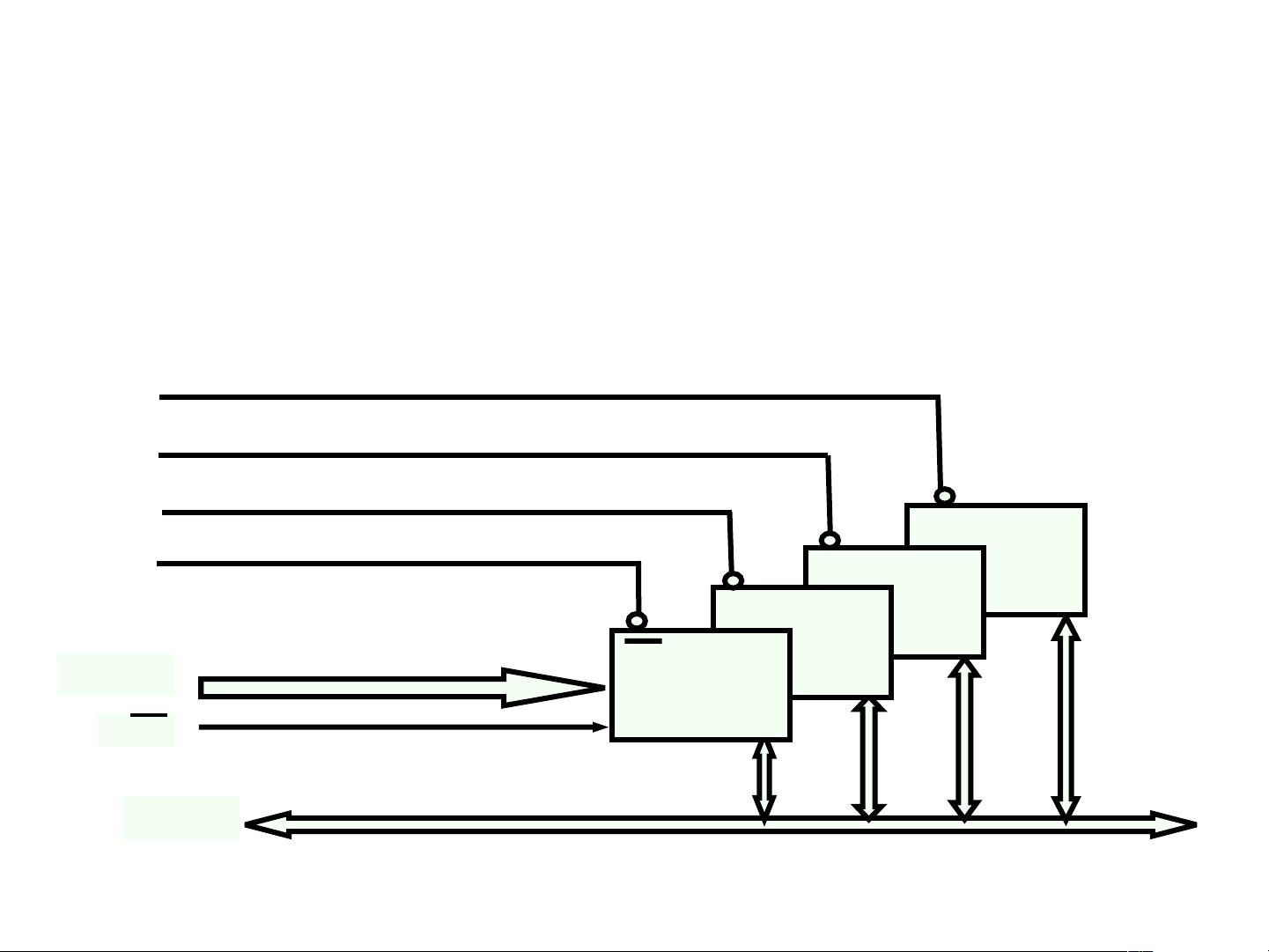

"该资源是关于计算机原理的第四章半导体存储器讲解的第二部分,主要讨论存储器与CPU的连接,包括地址分配、速度配合、总线负载能力以及片选译码方法。"

在计算机系统中,存储器与CPU之间的连接是确保数据快速准确传输的关键。本章首先介绍了地址分配,这涉及到如何在计算机的整个存储器空间中为不同的存储器电路分配物理地址。地址分配要考虑ROM区和RAM区,其中RAM又分为系统区和用户区。地址连续性是个重要问题,如果地址不够,可以通过增加驱动器来解决;若速度匹配存在问题,CPU可能会插入等待周期以适应慢速设备。

接着,内容提到了内存地址空间的分配,特别是在个人计算机(PC)中,大部分地址已经被系统占用或预留,用户能够扩展的存储器地址通常位于0C0000H到0DFFFFH的范围内,但实际设计时需根据系统配置和可能的地址范围调整。

片选译码是连接存储芯片到总线的重要技术,主要有线选法、部分译码法和全译码法。线选法是通过高位地址线直接选中芯片,适用于存储器容量小且CPU寻址空间远大于存储器容量的情况。然而,这种方法要求高位地址线不能同时为低电平,并可能导致地址重叠问题。部分译码法则使用部分高位地址进行译码,产生片选信号,可以减少地址重叠问题,但仍有部分地址线未参与译码。全译码法则对所有高位地址线进行译码,避免了地址重叠,更适用于大容量存储器系统。

示例中,线选法使用4个片选信号(CS)对应4根地址线,虽然电路结构简单,但有其局限性。部分译码法通过2-4译码器使用A13至A14进行译码,减少了对高位地址线的依赖,更适合中等容量的存储系统。而全译码方式则对所有高位地址线进行译码,提供了更为精确的地址映射,适合大规模存储器的配置。

总结来说,这部分内容深入探讨了存储器与CPU连接中的关键要素,包括地址分配策略和片选译码技术,这些都是构建高效计算机系统的基础。了解这些知识对于设计和优化计算机系统的存储架构至关重要。

2022-06-15 上传

2021-09-17 上传

2022-06-09 上传

2022-07-05 上传

2022-06-21 上传

2022-06-21 上传

2022-06-10 上传

2021-09-21 上传

2022-07-11 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 单片机串口通信仿真与代码实现详解

- LVGL GUI-Guider工具:设计并仿真LVGL界面

- Unity3D魔幻风格游戏UI界面与按钮图标素材详解

- MFC VC++实现串口温度数据显示源代码分析

- JEE培训项目:jee-todolist深度解析

- 74LS138译码器在单片机应用中的实现方法

- Android平台的动物象棋游戏应用开发

- C++系统测试项目:毕业设计与课程实践指南

- WZYAVPlayer:一个适用于iOS的视频播放控件

- ASP实现校园学生信息在线管理系统设计与实践

- 使用node-webkit和AngularJS打造跨平台桌面应用

- C#实现递归绘制圆形的探索

- C++语言项目开发:烟花效果动画实现

- 高效子网掩码计算器:网络工具中的必备应用

- 用Django构建个人博客网站的学习之旅

- SpringBoot微服务搭建与Spring Cloud实践