Xilinx FPGA驱动的数字示波器:模块设计与稳定性提升

200 浏览量

更新于2024-09-01

1

收藏 197KB PDF 举报

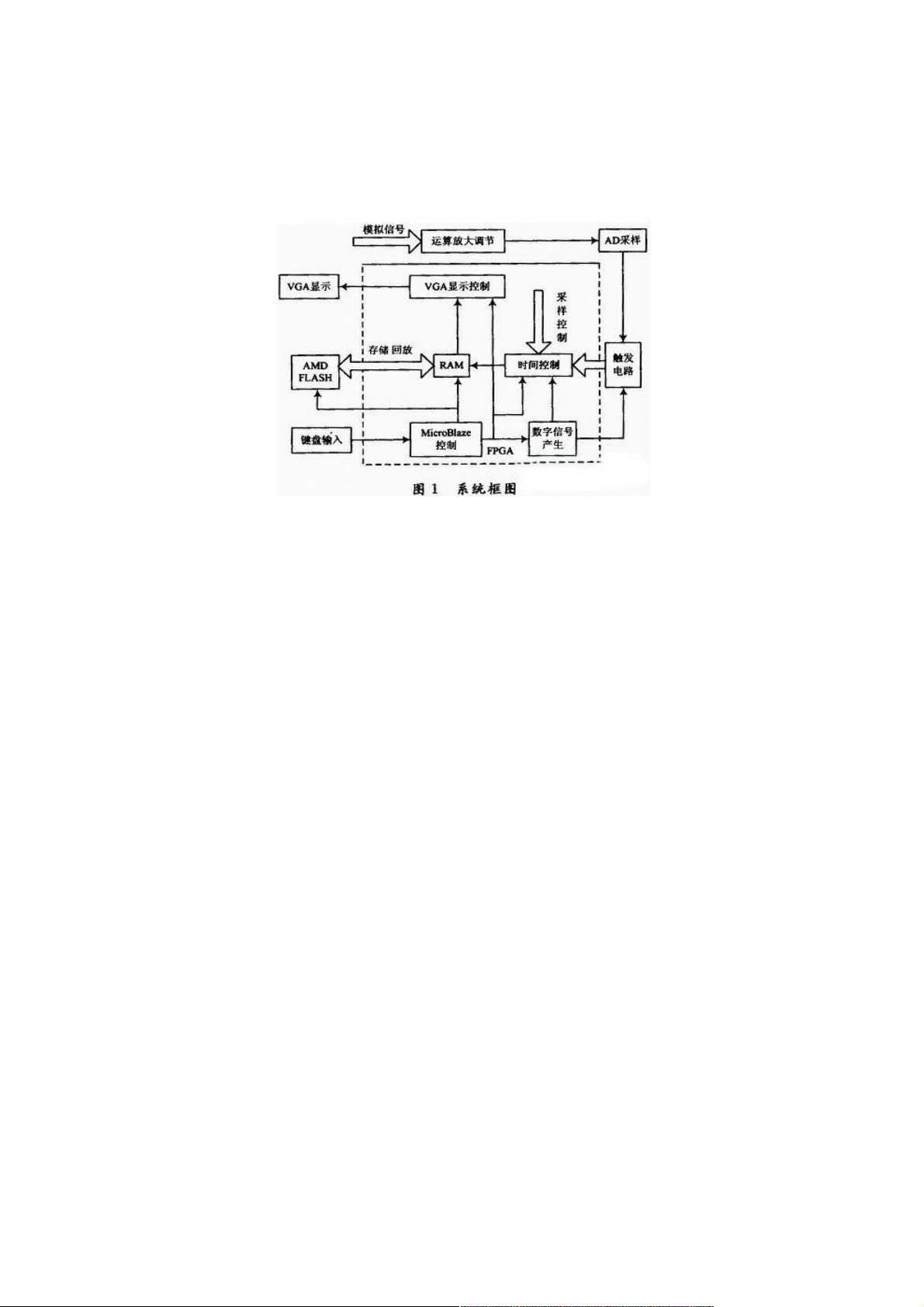

本文档详细介绍了基于FPGA的数字示波器设计,其核心目标是利用Xilinx开发环境构建高效且稳定的测量设备。设计的关键组成部分包括:

1. 系统方案设计:系统采用XPS技术,32位的VGA显示部分采用了双缓冲机制,通过FPGA内部的RAM存储缓存数据,确保图像的流畅显示。这种设计策略有助于提高系统的响应速度和稳定性。

2. 硬件设计

- 信号调理电路:针对输入的模拟信号,首先进行电压提升和比例缩小处理,确保满足ADS804这类12位高速A/D转换器的工作范围。

- A/D转换电路:采用并行数据处理方法,实时采样技术(10MHz)确保每个周期能捕捉足够多的数据点以获取完整信号。

- 触发电路模块:采用电压比较器实现外触发功能,允许对模拟信号进行任意电平触发。

- 存储模块:包含内存储和外存储,其中外存储采用16KB的E2PROM芯片,用于数据的持久保存。

- VGA显示模块:内置MicroBlaze软核,支持多页面切换,提供中文信息显示、彩色通道和波形显示,具有灵活的颜色控制。

- 键盘模块:4×4矩阵键盘用于用户交互,支持多种功能选择,如数字通道、模拟通道等操作。

3. 基于FPGA的软件设计:整个系统软件流程图展示了硬件组件的协作,包括触发电路、数字信号发生器、存储管理、键盘控制以及VGA显示驱动。这些模块共同作用,实现了数字示波器的功能和用户界面。

本设计通过FPGA技术,实现了高效的硬件集成和优化,提高了系统性能和稳定性,同时提供了友好的用户交互界面,使得数字示波器具有较高的实用价值和可靠性。

199 浏览量

317 浏览量

2021-10-07 上传

225 浏览量

weixin_38729438

- 粉丝: 3

- 资源: 915

最新资源

- Pusher_Backend

- Mini-proyectos:资料库3

- 基于po模式编写的自动化测试(pytest)

- (15.2.2)--网络爬虫进阶项目实战.zip

- 行业文档-设计装置-顶升移动工作平台.zip

- 正交报告

- books_list:书单作业

- 鱼跃CMS-轻量开源企业CMS v1.0.4

- WINDOWS11强制停止WindowsUpdate服务

- matlab2017b的gui转exe.zip

- 回形针-用于类型安全的编译时检查HTTP API的OpenAPI工具库-Rust开发

- nSchedule:学习TBSchedule

- dfti2

- 千博HTML5自适应企业网站系统 v2019 Build0424

- 行业文档-设计装置-一种平台式网版印刷机的自动出料装置.zip

- jdk1.8 下载。 hotspot (包含源码)