CPLD实验教程:基于VHDL和ispLEVER的数字电路设计

需积分: 9 55 浏览量

更新于2024-08-02

收藏 507KB DOC 举报

"电子电路制作实验指导书,专注于CPLD部分,利用VHDL语言、CPLD和Lattice公司的ispLEVER软件进行实践学习。实验内容包括基础的LED控制、数码管显示、计数器、分频器以及音乐发生器等,旨在通过实例深入理解VHDL语言和ispLEVER软件的使用,体验数字电路设计的仿真、下载与扩展设计过程。ispLEVER软件是一款全面的EDA工具,支持多种输入方式,具备功能和时序仿真能力,适用于教学、科研及产品开发,尤其突出其ISP技术在硬件重构和升级中的优势。"

本文主要介绍了电子电路制作实验的CPLD部分,该实验依托于硬件描述语言VHDL,这是一种用于描述电子系统的高级语言,特别是在可编程逻辑器件(如CPLD)的设计中广泛应用。VHDL允许工程师以结构化的方式描述电路的逻辑功能,便于设计、验证和实现。

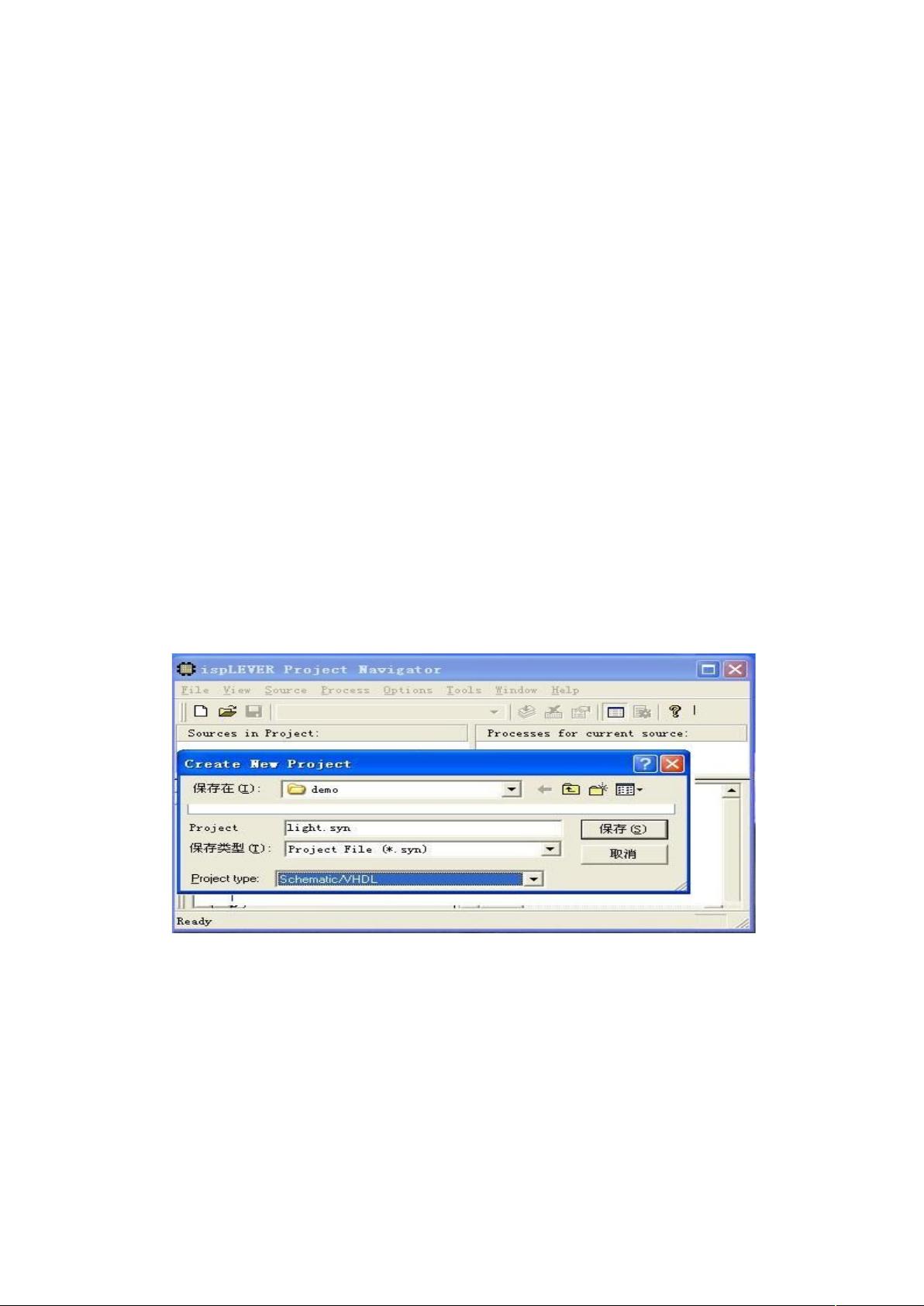

CPLD,即复杂可编程逻辑器件,是一种可以重新配置的集成电路,用于实现用户自定义的数字逻辑功能。在本实验中,CPLD作为核心元件,通过ispLEVER软件进行编程和管理。Lattice公司的ispLEVER是一款强大的电子设计自动化软件,集成了原理图输入、VHDL和Verilog-HDL等硬件描述语言输入,以及逻辑模拟和编译等功能。其ISP(In-System Programming)技术使得CPLD的逻辑配置可以在不从电路板上移除芯片的情况下进行更新,极大地提高了设计效率和灵活性。

实验内容涵盖了一系列基础到进阶的数字电路设计,包括实验一的LED控制,实验二的数码管显示,实验三的N进制计数器,实验四的分频器,以及实验五的简易乐曲发生器。这些实验旨在帮助学生逐步熟悉VHDL语言,掌握ispLEVER软件的使用,并实际操作CPLD来实现各种数字逻辑功能。

通过这些实验,学习者不仅可以学习到数字电路的基本原理,还能了解到现代电子设计流程中的关键步骤,包括逻辑设计、仿真验证、编程下载以及实际电路测试。实验还强调了硬件设计的动态可配置性,这是现代电子系统设计的一个重要特点,尤其是随着现场可编程门阵列(FPGA)和CPLD等技术的发展,硬件设计更加趋向于软件化和灵活化。

这份电子电路制作实验指导书提供了一个理论与实践相结合的学习平台,对于理解和掌握VHDL、CPLD以及现代EDA工具的使用具有极大的价值,对于电子工程的学生和爱好者来说是一份宝贵的参考资料。

2024-02-22 上传

2024-05-08 上传

点击了解资源详情

2022-01-10 上传

233 浏览量

1058 浏览量

495 浏览量

526 浏览量

143 浏览量

ggj_jack

- 粉丝: 0

- 资源: 9

最新资源

- SandeshEPaper-Downloader

- 县干部在组织工作和关心后代工作会上的发言

- openlayers v6.3.1-dist.zip

- matlab的slam代码-Graph-SLAM-MATLAB:使用MATLAB代码绘制SLAM分配图

- openlayers v6.3.1.zip

- Leetcode-April-Challenge-2021:它包含《 Leetcode 2021年4月挑战》中的问题的解决方案

- jma-weather-api:取消日本气象厅的天气预报

- 五金模具维修经验

- automata:一个用于模拟有限自动机,下推自动机和图灵机的Python库

- cb-khayeemate

- powershell-pong:在powershell中乒乓! 因为为什么不

- Java编写的游戏服务端引擎.zip

- Redis-x64-3.0.500.zip

- 响应式博客设计网站模板

- FluentWPF:WPF的流利设计系统

- java版sm4源码-gmssl-java-sdk:gmssl-java-sdk