FPGA实现的视频帧同步机设计与应用

需积分: 34 181 浏览量

更新于2024-09-12

收藏 305KB PDF 举报

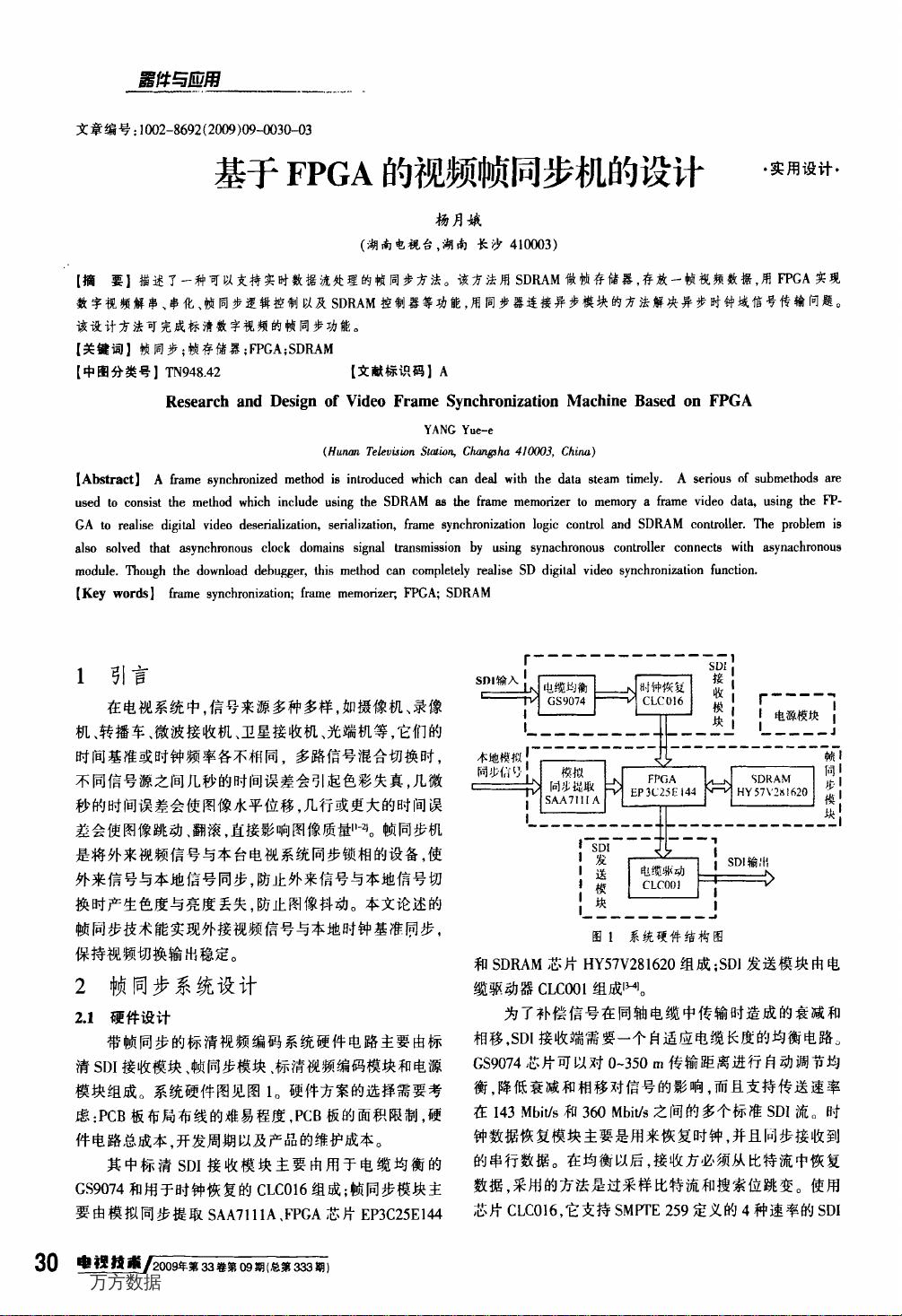

"基于FPGA的视频帧同步机设计,适用于实时数据流处理,通过SDRAM作为帧存储器,FPGA实现数字视频解串、串化、帧同步逻辑控制及SDRAM控制器,解决异步时钟域信号传输问题。"

在现代数字视频处理系统中,帧同步是一个至关重要的环节,它确保视频数据按照正确的时间顺序被处理和显示,避免画面撕裂或跳帧现象。基于FPGA(Field-Programmable Gate Array)的视频帧同步机设计提供了一个高效且灵活的解决方案。

该设计利用FPGA的并行处理能力,实现了数字视频的解串(Deserializer)和串化(Serializer)过程。解串器将高速串行数据转化为并行数据,便于FPGA内部处理;而串化器则将处理后的并行数据转换回串行形式,以适应外部接口的要求。这样的设计提高了数据传输速率,满足了实时视频处理的需求。

帧同步逻辑控制是该设计的核心部分,它确保每一帧视频数据的准确捕获和处理。通常,视频数据以帧为单位连续传输,帧同步逻辑控制负责检测帧起始和结束的标志,从而确定数据的正确边界。这一步对于保持视频流的连贯性至关重要。

为了存储一帧视频数据,设计中采用了SDRAM(Synchronous Dynamic Random-Access Memory),这是一种同步动态随机存取内存,其读写操作与系统时钟同步,提供了高带宽和大容量的数据存储。FPGA作为SDRAM的控制器,管理数据的读写操作,确保数据在正确的时序下进入和离开存储器。

在不同的时钟域之间传输数据通常会遇到同步问题,设计中采用同步器来解决这一问题。同步器是一种用于在不同时钟域间传递数据的电路,它可以有效地消除由于时钟偏移引起的 metastability( metastability指的是两个不同时钟域中的信号在转换过程中可能出现的不稳定状态),保证数据的完整性和正确性。

通过调试和验证,该设计能够完全实现标清数字视频的帧同步功能。FPGA的可编程特性使得这种设计方案具有很高的灵活性和可扩展性,可以根据不同的视频标准和应用需求进行定制。对于那些涉及视频处理的领域,如视频编码、解码、图像分析等,基于FPGA的帧同步机设计都具有广泛的应用前景。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-05-22 上传

2021-07-13 上传

2020-10-19 上传

2021-07-13 上传

106 浏览量

2021-05-20 上传

鬼谷清泉

- 粉丝: 5

- 资源: 136

最新资源

- mpu6050 + dmp .rar

- fallapalooza-v3:用于使用新的解析方法来测试Fallapalooza流输出的测试平台

- 视频帧图片提取器一款可提取视频帧数目每隔自定义帧数提取.rar

- cdkappsync-dynamo-pipeline

- berstend.github.io

- portfolio

- AITrainingSpace:我的个人工作台空间,用于测试人工智能算法

- ele:侍者

- Clam Sentinel-开源

- 离散数学及其应用第七版习题答案.zip

- Path-Finding-Problem:节点之间的最短路径查找问题!

- ENSE375-groupB

- ufabc-classes:课堂上的个人程序-练习,理论等等

- website:密歇根州生态数据俱乐部的网站

- e:演示,电子学习,幻灯片,漫画

- goit-markup-hw-03