没有合适的资源?快使用搜索试试~ 我知道了~

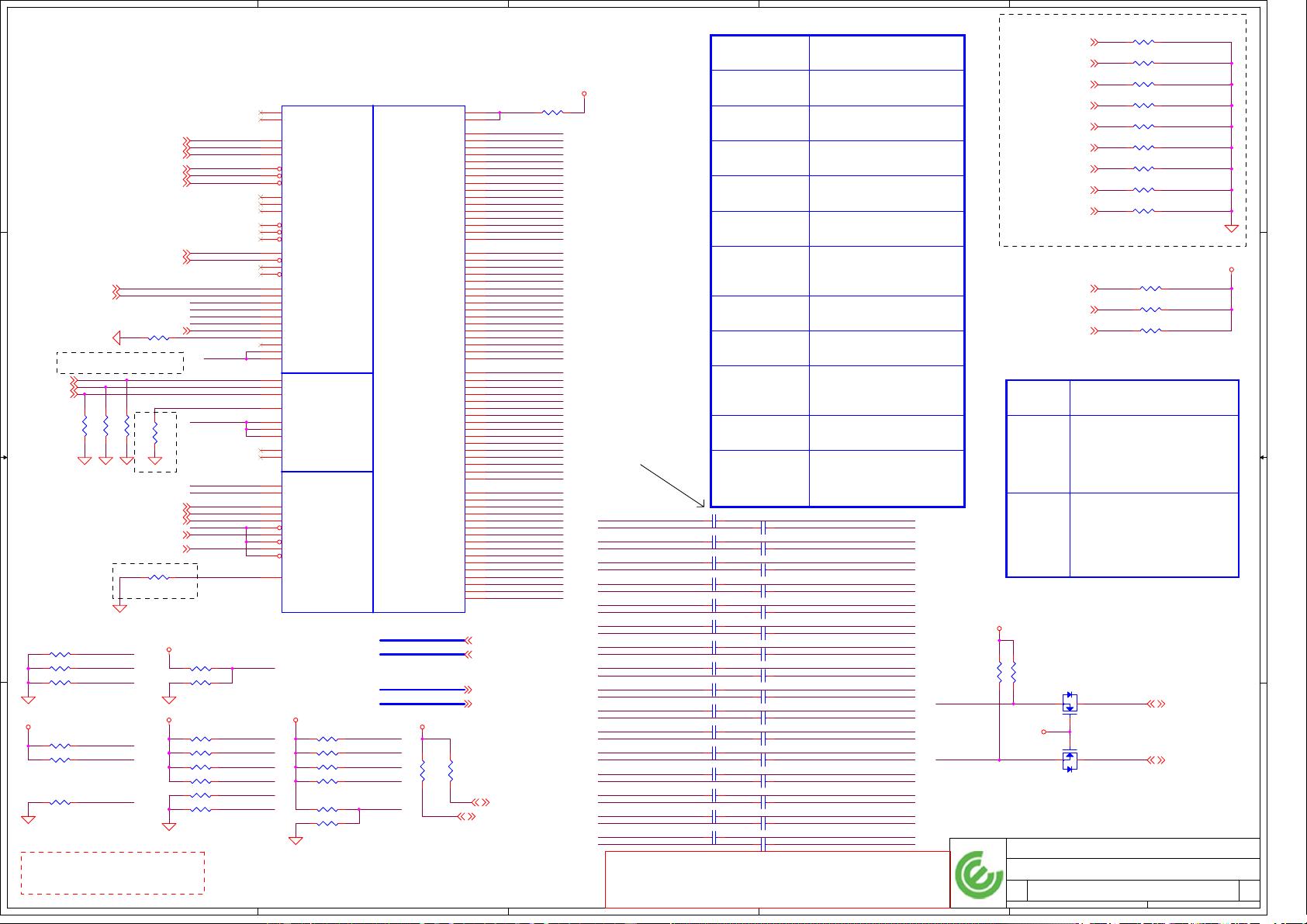

首页DELL M1210笔记本主板详细设计图纸

DELL M1210图纸是一份详细的设计文档,由Compal Electronics, Inc.为Dell制造的笔记本电脑提供技术支持。这份图纸针对的是型号为HAL31(离散)和HAL30(统一内存架构,即UMA)的笔记本,采用了uFCPGAMobile Yonah平台,集成了Intel Calistoga处理器和ICH7M芯片组。修订版本为0.5,标有DELL的X03标识,表明是专属于Dell的机密设计。 图纸编号LA-3001P,其中包含PCB(印刷电路板)的相关信息,如PCB零件编号DA800004W0L,以及BOM(Bill of Materials,物料清单)号码,用于跟踪各个组件的使用情况。对于离散部件,使用了45140031L11,而对于UMA,使用了两次45140031L01。该图纸也包括了一个MBPCB(主板)的设计,其尺寸为0.4毫米,并且是一个封面页,列出了标题、尺寸、文档编号、修订版本、日期等基本信息。 值得注意的是,图纸上的保密条款非常重要,强调未经 Dell 的明确书面授权,不得转移或复制此图纸。此外,未经 Dell 明确书面同意,也不得将图纸或其中的信息透露给第三方。这体现了在IT行业中,尤其是硬件设计过程中对知识产权和商业秘密的保护。 这份图纸的内容涵盖了笔记本电脑的核心组件布局、连接方式、电源管理、数据传输等多个关键领域,对笔记本维修工程师和制造商来说,是理解和修复M1210笔记本内部结构,进行故障诊断和升级的重要参考资料。通过阅读和理解这份图纸,技术人员可以更好地定位和处理问题,确保设备的正常运行和维护效率。

资源详情

资源推荐

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DMI_MTX_IRX_N0

H_D#11

DMI_MTX_IRX_P0

H_D#23

H_D#31

H_D#2

H_D#37

H_D#58

H_D#50

H_D#5

H_D#35

H_D#39

H_D#52

H_D#27

H_D#60

H_D#10

H_D#44

H_D#51

H_D#8

H_D#59

H_D#43

H_D#56

H_D#4

H_D#18

H_D#3

H_D#14

H_D#48

H_D#28

H_D#34

H_D#36

H_D#55

H_D#62

H_D#13

H_D#24

H_D#22

H_D#29

H_D#16

H_D#57

H_D#20

H_D#9

H_D#0

H_D#17

H_D#1

H_D#53

H_D#26

H_D#7

H_D#45

H_D#40

H_D#54

H_D#41

H_D#15

H_D#38

H_D#25

H_D#42

H_D#61

H_D#32

H_D#6

H_D#12

H_D#63

H_D#19

DREF_SSCLK

DREF_SSCLK#

MCH_DREFCLK#

MCH_DREFCLK

CLK_3GPLLREQ#

MCH_ICH_SYNC#

CFG8

CFG10

CFG14

CFG15

CFG17

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

PM_EXTTS#1_R

CFG3

CFG4

DREF_SSCLK#

MCH_DREFCLK#

CFG11

MCH_DREFCLK

DREF_SSCLK

DPRSLPVR

H_VREF H_SWNG0 H_SWNG1

PM_EXTTS#0V_DDR_MCH_REF

PM_EXTTS#1_R

H_ADSTB#1

H_A#28

H_A#15

H_SWNG1

H_XRCOMP

H_RS#0

CPU_MCH_BSEL1

H_REQ#0

H_A#16

CFG7

CFG5

H_HIT#

H_DSTBP#0

M_CLK_DDR3

DDR_CKE0_DIMMA

H_REQ#4

H_A#20

H_A#17

H_A#13

H_SWNG0

H_REQ#2

H_BNR#

M_OCDOCMP0

DMI_MRX_ITX_N0

DDR_CKE1_DIMMA

H_A#8

M_ODT1

H_DSTBP#2

H_A#26

H_A#19

H_D#46

CFG13

H_REQ#3

CFG9

H_DINV#2

CLK_MCH_BCLK#

H_REQ#1

H_A#7

H_YSCOMP

M_CLK_DDR#0

ICH_PWRGD

CPU_MCH_BSEL0

H_BPRI#

H_DINV#0

H_A#22

DDR_CKE3_DIMMB

H_D#21

CFG18

H_CPUSLP#

H_DPWR#

H_ADS#

H_DSTBP#3

H_DSTBN#3

H_A#27

H_A#6

H_A#3

M_CLK_DDR#1

H_D#30

H_D#33

CFG16

CLK_MCH_BCLK

PLTRST_MCH_R#

CFG19

CFG12

SMRCOMPN

V_DDR_MCH_REF

DDR_CS1_DIMMA#

H_DSTBP#1

H_DINV#3

H_RS#2

H_ADSTB#0

H_A#25

CFG6

H_LOCK#

DDR_CKE2_DIMMB

H_RESET#

H_A#12

H_A#11

M_ODT3

H_DBSY#

H_DSTBN#0

H_DSTBN#1

H_BR0#

M_CLK_DDR#2

M_OCDOCMP1

H_A#18

H_A#10

H_DSTBN#2

H_RS#1

H_A#14

H_XSCOMP

CPU_MCH_BSEL2

H_A#21

PM_BMBUSY#

H_DRDY#

H_HITM#

M_CLK_DDR#3

DDR_CS0_DIMMA#

DDR_CS3_DIMMB#

H_D#47

H_A#31

H_A#30

H_A#29

H_A#24

H_A#23

PM_EXTTS#1_R

PM_EXTTS#0

M_ODT2

M_ODT0

DDR_CS2_DIMMB#

H_D#49

H_TRDY#

H_DINV#1

H_A#9

H_A#5

H_A#4

THERMTRIP_MCH#

H_DEFER#

M_CLK_DDR2

M_CLK_DDR0

M_CLK_DDR1

H_YRCOMP

DMI_MRX_ITX_P1

DMI_MRX_ITX_N2

DMI_MRX_ITX_P0

DMI_MTX_IRX_N3

DMI_MTX_IRX_P3

DMI_MTX_IRX_N2

DMI_MTX_IRX_N1

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CFG20

THERMTRIP_MCH#

DMI_MRX_ITX_N1

DMI_MRX_ITX_N3

SMRCOMPP

H_VREF

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

+1.05V_VCCP

+1.05V_VCCP+1.05V_VCCP+1.05V_VCCP

+3.3V_RUN

+1.8V_SUS

+1.05V_VCCP

+1.5V_RUN

H_A#[3..31] <7>

H_ADSTB#1 <7>

H_ADSTB#0 <7>

H_TRDY# <7>

H_HIT# <7>

H_LOCK# <7>

H_DEFER# <7>

H_BPRI# <7>

H_BR0# <7>

H_RESET# <7>

H_DPWR# <7>

H_DRDY# <7>

H_DBSY# <7>

CLK_MCH_BCLK# <6>

CLK_MCH_BCLK <6>

H_BNR# <7>

H_ADS# <7>

H_DINV#1 <7>

H_DINV#0 <7>

H_DINV#2 <7>

H_DINV#3 <7>

H_CPUSLP# <7,22>

CFG12 <12>

CPU_MCH_BSEL1 <6,8>

CLK_MCH_3GPLL# <6>

M_ODT0<17>

CFG7 <12>

PLTRST_MCH#<21>

CLK_MCH_3GPLL <6>

M_ODT3<18>

CFG9 <12>

CFG19 <12>

MCH_ICH_SYNC#<21>

M_ODT2<18>

CPU_MCH_BSEL0 <6,8>

CFG16 <12>

THERMTRIP_MCH#<16>

CFG5 <12>

CPU_MCH_BSEL2 <6,8>

CFG20 <12>

CFG13 <12>

V_DDR_MCH_REF<17,18,41>

M_ODT1<17>

CFG18 <12>

H_HITM# <7>

CFG11 <12>

DMI_MTX_IRX_P1<23>

DMI_MRX_ITX_P0<23>

M_CLK_DDR#3<18>

DMI_MTX_IRX_N1<23>

DMI_MRX_ITX_N3<23>

DMI_MTX_IRX_P0<23>

DDR_CS2_DIMMB#<18>

M_CLK_DDR#0<17>

DMI_MTX_IRX_N0<23>

DMI_MRX_ITX_N2<23>

DDR_CS1_DIMMA#<17>

DMI_MTX_IRX_N3<23>

M_CLK_DDR1<17>

M_CLK_DDR3<18>

DMI_MRX_ITX_P3<23>

DMI_MRX_ITX_N1<23>

DMI_MRX_ITX_P2<23>

DDR_CS0_DIMMA#<17>

DMI_MRX_ITX_N0<23>

DDR_CKE1_DIMMA<17>

DMI_MTX_IRX_P3<23>

DDR_CKE2_DIMMB<18>

DDR_CS3_DIMMB#<18>

DMI_MTX_IRX_P2<23>

DMI_MRX_ITX_P1<23>

M_CLK_DDR#2<18>

DDR_CKE3_DIMMB<18>

M_CLK_DDR0<17>

DDR_CKE0_DIMMA<17>

DMI_MTX_IRX_N2<23>

M_CLK_DDR#1<17>

M_CLK_DDR2<18>

PM_BMBUSY#<23>

H_D#[0..63]<7>

H_RS#1 <7>

H_RS#2 <7>

H_RS#0 <7>

H_DSTBN#1 <7>

H_DSTBN#0 <7>

H_DSTBN#3 <7>

H_DSTBN#2 <7>

H_DSTBP#1 <7>

H_DSTBP#0 <7>

H_DSTBP#3 <7>

H_DSTBP#2 <7>

H_REQ#0 <7>

H_REQ#1 <7>

H_REQ#2 <7>

H_REQ#3 <7>

H_REQ#4 <7>

PM_EXTTS#0<17>

DREF_SSCLK# <6>

MCH_DREFCLK <6>

MCH_DREFCLK# <6>

DREF_SSCLK <6>

CLK_3GPLLREQ# <6>

ICH_PWRGD<23,33>

CFG6 <12>

CFG10 <12>

DPRSLPVR<23,42>

Title

Size Document Number Rev

Date: Sheet

of

LA-3001P

0.4

Calistoga(1 of 6)

10 73Monday, April 17, 2006

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

Layout Note:

H_XRCOMP & H_YRCOMP / H_SWNG0 &

H_SWNG1 trace width and spacing is 10/20

Description at page12

UMA use 945GM A2 ( P/N: SA00000592L )

Discrete use 945PM A2 ( P/N: SA00000KD1L)

Note :

CFG3:17 has

internal pullup,

CFG18:19 has

internal pulldown

For Discrete Only

Place closed to U9 pinAK1,pinAK41

R300

10K_0402_5%~D

12

C509

0.1U_0402_16V4Z~D

1

2

R50 0_0402_5%~D2@

1 2

R318

221_0402_1%~D

12

R354

200_0402_1%~D

12

R49 0_0402_5%~D2@

1 2

C398

0.1U_0402_16V4Z~D

1

2

C326

0.1U_0402_16V4Z~D

1

2

R365

100_0402_1%~D

12

HOST

U9A

CALISTOGA A0_FCBGA1466~D

HD0#

F1

HD1#

J1

HD2#

H1

HD3#

J6

HD4#

H3

HD5#

K2

HD6#

G1

HD7#

G2

HD8#

K9

HD9#

K1

HD10#

K7

HD11#

J8

HD12#

H4

HD13#

J3

HD14#

K11

HD15#

G4

HD16#

T10

HD17#

W11

HD18#

T3

HD19#

U7

HD20#

U9

HD21#

U11

HD22#

T11

HD23#

W9

HD24#

T1

HD25#

T8

HD26#

T4

HD27#

W7

HD28#

U5

HD29#

T9

HD30#

W6

HD31#

T5

HD32#

AB7

HD33#

AA9

HD34#

W4

HD35#

W3

HD36#

Y3

HD37#

Y7

HD38#

W5

HD39#

Y10

HD40#

AB8

HD41#

W2

HD42#

AA4

HD43#

AA7

HD44#

AA2

HD45#

AA6

HD46#

AA10

HD47#

Y8

HD48#

AA1

HD49#

AB4

HD50#

AC9

HD51#

AB11

HD52#

AC11

HD53#

AB3

HD54#

AC2

HD55#

AD1

HD56#

AD9

HD57#

AC1

HD58#

AD7

HD59#

AC6

HD60#

AB5

HD61#

AD10

HD62#

AD4

HD63#

AC8

HVREF1

K13

HXRCOMP

E1

HXSCOMP

E2

HYRCOMP

Y1

HYSCOMP

U1

HXSWING

E4

HYSWING

W1

HA3#

H9

HA4#

C9

HA5#

E11

HA6#

G11

HA7#

F11

HA8#

G12

HA9#

F9

HA10#

H11

HA11#

J12

HA12#

G14

HA13#

D9

HA14#

J14

HA15#

H13

HA16#

J15

HA17#

F14

HA18#

D12

HA19#

A11

HA20#

C11

HA21#

A12

HA22#

A13

HA23#

E13

HA24#

G13

HA25#

F12

HA26#

B12

HA27#

B14

HA28#

C12

HA29#

A14

HA30#

C14

HA31#

D14

HREQ#0

D8

HREQ#1

G8

HREQ#2

B8

HREQ#3

F8

HREQ#4

A8

HADSTB#0

B9

HADSTB#1

C13

HRS0#

B4

HRS1#

E6

HRS2#

D6

HCLKN

AG1

HCLKP

AG2

HDINV#0

J7

HDINV#1

W8

HDINV#2

U3

HDINV#3

AB10

HDSTBN#0

K4

HDSTBN#1

T7

HDSTBN#2

Y5

HDSTBN#3

AC4

HDSTBP#0

K3

HDSTBP#1

T6

HDSTBP#2

AA5

HDSTBP#3

AC5

HCPURST#

B7

HADS#

E8

HTRDY#

E7

HDPWR#

J9

HDRDY#

H8

HDEFER#

C3

HHITM#

D4

HHIT#

D3

HLOCK#

B3

HBREQ0#

C7

HBNR#

C6

HBPRI#

F6

HDBSY#

A7

HCPUSLP#

E3

HVREF0

J13

R425 100_0402_1%~D

12

R436 80.6_0402_1%~D

1 2

R432 80.6_0402_1%~D

1 2

DMI

DDR MUXING

CFG

PM

CLKNC

RESERVED

U9B

CALISTOGA A0_FCBGA1466~D

DMIRXN0

AE35

DMIRXN1

AF39

DMIRXN2

AG35

DMIRXN3

AH39

DMIRXP0

AC35

DMIRXP1

AE39

DMIRXP2

AF35

DMIRXP3

AG39

DMITXN0

AE37

DMITXN1

AF41

DMITXN2

AG37

DMITXN3

AH41

DMITXP0

AC37

DMITXP1

AE41

DMITXP2

AF37

DMITXP3

AG41

SM_CK0

AY35

SM_CK1

AR1

SM_CK2

AW7

SM_CK3

AW40

SM_CK0#

AW35

SM_CK1#

AT1

SM_CK2#

AY7

SM_CK3#

AY40

SM_OCDCOMP0

AL20

SM_OCDCOMP1

AF10

SM_ODT0

BA13

SM_ODT1

BA12

SM_ODT2

AY20

SM_ODT3

AU21

SM_RCOMPN

AV9

SM_RCOMPP

AT9

SM_VREF0

AK1

SM_VREF1

AK41

SM_CKE0

AU20

SM_CKE1

AT20

SM_CKE2

BA29

SM_CKE3

AY29

SM_CS0#

AW13

SM_CS1#

AW12

SM_CS2#

AY21

SM_CS3#

AW21

CFG16

G18

CFG1

K18

CFG2

J18

CFG3

F18

CFG4

E15

CFG5

F15

CFG6

E18

CFG7

D19

CFG8

D16

CFG9

G16

CFG10

E16

CFG11

D15

CFG12

G15

CFG13

K15

CFG14

C15

CFG15

H16

CFG0

K16

CFG17

H15

CFG18

J25

CFG19

K27

CFG20

J26

G_CLKP

AG33

G_CLKN

AF33

D_REF_CLKN

A27

D_REF_CLKP

A26

D_REF_SSCLKN

C40

D_REF_SSCLKP

D41

NC0

A3

NC1

A39

NC2

A4

NC3

A40

NC4

AW1

NC5

AW41

NC6

AY1

NC7

BA1

NC8

BA2

NC9

BA3

NC10

BA39

NC11

BA40

NC12

BA41

NC13

C1

NC14

AY41

NC15

B2

NC16

B41

NC17

C41

NC18

D1

PM_BMBUSY#

G28

PM_EXTTS0#

F25

PM_EXTTS1#

H26

PM_THERMTRIP#

G6

PWROK

AH33

RSTIN#

AH34

RESERVED1

T32

RESERVED2

R32

RESERVED3

F3

RESERVED4

F7

RESERVED5

AG11

RESERVED6

AF11

RESERVED7

H7

RESERVED8

J19

RESERVED9

A41

RESERVED10

A34

RESERVED11

D28

RESERVED12

D27

RESERVED13

A35

ICH_SYNC#

K28

CLK_REQ#

H32

R297

10K_0402_5%~D

@

12

R330

100_0402_1%~D

12

C300

0.1U_0402_16V4Z~D

1

2

R397

221_0402_1%~D

12

R79

54.9_0402_1%~D

12

R396

100_0402_1%~D

12

R326 0_0402_5%~D2@

1 2

R337 0_0402_5%~D2@

1 2

R296

0_0402_5%~D

R383

54.9_0402_1%~D

12

C704

0.1U_0402_16V4Z~D

1

2

R313

75_0402_5%~D

1 2

R81

24.9_0402_1%~D

12

R395

24.9_0402_1%~D

12

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_B_D11

DDR_B_D57

DDR_B_D46

DDR_B_D7

DDR_B_D0

DDR_B_D44

DDR_B_D40

DDR_B_D30

DDR_B_D27

DDR_B_D15

DDR_B_D3

DDR_B_D35

DDR_B_D25

DDR_B_D23

DDR_B_D49

DDR_B_D37

DDR_B_D19

DDR_B_D48

DDR_B_D47

DDR_B_D36

DDR_B_D18

DDR_B_D8

DDR_B_D62

DDR_B_D60

DDR_B_D9

DDR_B_D2

DDR_B_D52

DDR_B_D50

DDR_B_D22

DDR_B_D56

DDR_B_D51

DDR_B_D39

DDR_B_D28

DDR_B_D17

DDR_B_D45

DDR_B_D6

DDR_B_D61

DDR_B_D58

DDR_B_D1

DDR_B_D54

DDR_B_D41

DDR_B_D31

DDR_B_D12

DDR_B_D5

DDR_B_D38

DDR_B_D32

DDR_B_D20

DDR_B_D16

DDR_B_D14

DDR_B_D33

DDR_B_D63

DDR_B_D59

DDR_B_D42

DDR_B_D55

DDR_B_D53

DDR_B_D43

DDR_B_D29

DDR_B_D26

DDR_B_D13

DDR_B_D4

DDR_B_BS2

DDR_B_D34

DDR_B_D24

DDR_B_D21

DDR_B_D10

DDR_B_CAS#

DDR_B_WE#

DDR_B_RAS#

SB_RCVENIN#

DDR_B_DQS7

DDR_B_MA9

DDR_B_MA0

DDR_B_MA7

DDR_B_DQS0

DDR_B_DM3

DDR_B_DQS1

DDR_B_DM1

DDR_B_DQS5

DDR_B_DM0

DDR_B_MA2

DDR_B_MA13

DDR_B_DM5

DDR_B_BS1

DDR_B_MA4

DDR_B_DM6

DDR_B_DQS4

DDR_B_MA5

DDR_B_MA3

DDR_B_MA11

DDR_B_BS0

DDR_B_MA6

DDR_B_DQS3

DDR_B_MA8

DDR_B_MA10

DDR_B_DM7

DDR_B_MA12

DDR_B_DM4

DDR_B_MA1

DDR_B_DQS2

DDR_B_DQS6

DDR_B_DM2

DDR_B_DQS#1

DDR_B_DQS#3

DDR_B_DQS#0

DDR_B_DQS#7

DDR_B_DQS#5

DDR_B_DQS#4

DDR_B_DQS#6

DDR_B_DQS#2

SB_RCVENOUT#

DDR_A_D48

DDR_A_D43

DDR_A_D3

DDR_A_DM6

DDR_A_MA1

DDR_A_MA9

DDR_A_D51

DDR_A_D18

DDR_A_D0

DDR_A_D40

SA_RCVENOUT#

DDR_A_DQS5

DDR_A_DM3

DDR_A_MA10

DDR_A_D52

DDR_A_D33

DDR_A_D23

DDR_A_D16

DDR_A_D9

DDR_A_DQS2

DDR_A_DQS4

DDR_A_MA5

DDR_A_MA2

DDR_A_D35

DDR_A_D39

DDR_A_DQS#3

DDR_A_DQS#2

DDR_A_D46

DDR_A_RAS#

DDR_A_D50

DDR_A_DM1

DDR_A_D45

DDR_A_D32

DDR_A_D20

DDR_A_D53

DDR_A_DQS#6

DDR_A_D58

DDR_A_D54

DDR_A_DQS#7

DDR_A_DM7

DDR_A_D31

DDR_A_DQS3

DDR_A_DQS#1

DDR_A_DM4

DDR_A_D57

DDR_A_D25

DDR_A_MA7

DDR_A_D44

DDR_A_D41

DDR_A_D2

DDR_A_D4

DDR_A_MA8

DDR_A_D13

DDR_A_D26

DDR_A_BS0

DDR_A_D11

DDR_A_D47

DDR_A_CAS#

DDR_A_D22

DDR_A_D7

DDR_A_D5

DDR_A_DM2

DDR_A_MA0

DDR_A_D56

DDR_A_BS1

DDR_A_D42

DDR_A_D8

DDR_A_DQS1

DDR_A_D27

DDR_A_D19

DDR_A_DQS#0

DDR_A_MA11

DDR_A_DQS#5

DDR_A_D30

DDR_A_D29

DDR_A_D49

DDR_A_D21

DDR_A_DQS7

DDR_A_MA4

DDR_A_D28

DDR_A_D55

DDR_A_D34

DDR_A_BS2

DDR_A_D24

DDR_A_D15

DDR_A_D10

DDR_A_MA13

DDR_A_D17

DDR_A_DM0

DDR_A_D1

DDR_A_D36

DDR_A_D38

DDR_A_DQS6

DDR_A_MA6

DDR_A_DM5

DDR_A_MA3

DDR_A_D14

DDR_A_DQS0

DDR_A_D12

DDR_A_DQS#4

DDR_A_D37

DDR_A_D59

DDR_A_MA12

DDR_A_D62

DDR_A_D6

DDR_A_D60

DDR_A_D61

DDR_A_D63

DDR_A_WE#

SA_RCVENIN#

DDR_B_D[0..63] <18>DDR_A_D[0..63] <17>

DDR_B_BS2<18>

DDR_B_DQS[0..7]<18>

DDR_B_CAS#<18>

DDR_B_RAS#<18>

DDR_B_MA[0..13]<18>

DDR_B_DQS#[0..7]<18>

DDR_B_WE#<18>

DDR_B_DM[0..7]<18>

DDR_B_BS0<18>

DDR_B_BS1<18>

DDR_A_WE#<17>

DDR_A_BS0<17>

DDR_A_DQS#[0..7]<17>

DDR_A_BS1<17>

DDR_A_MA[0..13]<17>

DDR_A_BS2<17>

DDR_A_RAS#<17>

DDR_A_DQS[0..7]<17>

DDR_A_CAS#<17>

DDR_A_DM[0..7]<17>

Title

Size Document Number Rev

Date: Sheet

of

LA-3001P

0.4

Calistogo(2 of 6)

11 73Monday, April 17, 2006

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Add a test point Add a test point

T4 PAD~D T5 PAD~D

DDR SYS MEMORY B

U9E

CALISTOGA A0_FCBGA1466~D

SB_DQ0

AK39

SB_DQ1

AJ37

SB_DQ2

AP39

SB_DQ3

AR41

SB_DQ4

AJ38

SB_DQ5

AK38

SB_DQ6

AN41

SB_DQ7

AP41

SB_DQ8

AT40

SB_DQ9

AV41

SB_DQ10

AU38

SB_DQ11

AV38

SB_DQ12

AP38

SB_DQ13

AR40

SB_DQ14

AW38

SB_DQ15

AY38

SB_DQ16

BA38

SB_DQ17

AV36

SB_DQ18

AR36

SB_DQ19

AP36

SB_DQ20

BA36

SB_DQ21

AU36

SB_DQ22

AP35

SB_DQ23

AP34

SB_DQ24

AY33

SB_DQ25

BA33

SB_DQ26

AT31

SB_DQ27

AU29

SB_DQ28

AU31

SB_DQ29

AW31

SB_DQ30

AV29

SB_DQ31

AW29

SB_DQ32

AM19

SB_DQ33

AL19

SB_DQ34

AP14

SB_DQ35

AN14

SB_DQ36

AN17

SB_DQ37

AM16

SB_DQ38

AP15

SB_DQ39

AL15

SB_DQ40

AJ11

SB_DQ41

AH10

SB_DQ42

AJ9

SB_DQ43

AN10

SB_DQ44

AK13

SB_DQ45

AH11

SB_DQ46

AK10

SB_DQ47

AJ8

SB_DQ48

BA10

SB_DQ49

AW10

SB_DQ50

BA4

SB_DQ51

AW4

SB_DQ52

AY10

SB_DQ53

AY9

SB_DQ54

AW5

SB_DQ55

AY5

SB_DQ56

AV4

SB_DQ57

AR5

SB_DQ58

AK4

SB_DQ59

AK3

SB_DQ60

AT4

SB_DQ61

AK5

SB_DQ62

AJ5

SB_DQ63

AJ3

SB_BS0

AT24

SB_BS1

AV23

SB_BS2

AY28

SB_CAS#

AR24

SB_RAS#

AU23

SB_WE#

AR27

SB_RCVENIN#

AK16

SB_RCVENOUT#

AK18

SB_DM0

AK36

SB_DM1

AR38

SB_DM2

AT36

SB_DM3

BA31

SB_DM4

AL17

SB_DM5

AH8

SB_DM6

BA5

SB_DM7

AN4

SB_DQS0

AM39

SB_DQS1

AT39

SB_DQS2

AU35

SB_DQS3

AR29

SB_DQS4

AR16

SB_DQS5

AR10

SB_DQS6

AR7

SB_DQS7

AN5

SB_DQS0#

AM40

SB_DQS1#

AU39

SB_DQS2#

AT35

SB_DQS3#

AP29

SB_DQS4#

AP16

SB_DQS5#

AT10

SB_DQS6#

AT7

SB_DQS7#

AP5

SB_MA0

AY23

SB_MA1

AW24

SB_MA2

AY24

SB_MA3

AR28

SB_MA4

AT27

SB_MA5

AT28

SB_MA6

AU27

SB_MA7

AV28

SB_MA8

AV27

SB_MA9

AW27

SB_MA10

AV24

SB_MA11

BA27

SB_MA12

AY27

SB_MA13

AR23

DDR SYS MEMORY A

U9D

CALISTOGA A0_FCBGA1466~D

SA_DQ0

AJ35

SA_DQ1

AJ34

SA_DQ2

AM31

SA_DQ3

AM33

SA_DQ4

AJ36

SA_DQ5

AK35

SA_DQ6

AJ32

SA_DQ7

AH31

SA_DQ8

AN35

SA_DQ9

AP33

SA_DQ10

AR31

SA_DQ11

AP31

SA_DQ12

AN38

SA_DQ13

AM36

SA_DQ14

AM34

SA_DQ15

AN33

SA_DQ16

AK26

SA_DQ17

AL27

SA_DQ18

AM26

SA_DQ19

AN24

SA_DQ20

AK28

SA_DQ21

AL28

SA_DQ22

AM24

SA_DQ23

AP26

SA_DQ24

AP23

SA_DQ25

AL22

SA_DQ26

AP21

SA_DQ27

AN20

SA_DQ28

AL23

SA_DQ29

AP24

SA_DQ30

AP20

SA_DQ31

AT21

SA_DQ32

AR12

SA_DQ33

AR14

SA_DQ34

AP13

SA_DQ35

AP12

SA_DQ36

AT13

SA_DQ37

AT12

SA_DQ38

AL14

SA_DQ39

AL12

SA_DQ40

AK9

SA_DQ41

AN7

SA_DQ42

AK8

SA_DQ43

AK7

SA_DQ44

AP9

SA_DQ45

AN9

SA_DQ46

AT5

SA_DQ47

AL5

SA_DQ48

AY2

SA_DQ49

AW2

SA_DQ50

AP1

SA_DQ51

AN2

SA_DQ52

AV2

SA_DQ53

AT3

SA_DQ54

AN1

SA_DQ55

AL2

SA_DQ56

AG7

SA_DQ57

AF9

SA_DQ58

AG4

SA_DQ59

AF6

SA_DQ60

AG9

SA_DQ61

AH6

SA_DQ62

AF4

SA_DQ63

AF8

SA_BS0

AU12

SA_BS1

AV14

SA_BS2

BA20

SA_CAS#

AY13

SA_RAS#

AW14

SA_WE#

AY14

SA_RCVENIN#

AK23

SA_RCVENOUT#

AK24

SA_DM0

AJ33

SA_DM1

AM35

SA_DM2

AL26

SA_DM3

AN22

SA_DM4

AM14

SA_DM5

AL9

SA_DM6

AR3

SA_DM7

AH4

SA_DQS0

AK33

SA_DQS1

AT33

SA_DQS2

AN28

SA_DQS3

AM22

SA_DQS4

AN12

SA_DQS5

AN8

SA_DQS6

AP3

SA_DQS7

AG5

SA_DQS0#

AK32

SA_DQS1#

AU33

SA_DQS2#

AN27

SA_DQS3#

AM21

SA_DQS4#

AM12

SA_DQS5#

AL8

SA_DQS6#

AN3

SA_DQS7#

AH5

SA_MA0

AY16

SA_MA1

AU14

SA_MA2

AW16

SA_MA3

BA16

SA_MA4

BA17

SA_MA5

AU16

SA_MA6

AV17

SA_MA7

AU17

SA_MA8

AW17

SA_MA9

AT16

SA_MA10

AU13

SA_MA11

AT17

SA_MA12

AV20

SA_MA13

AV12

T3 PAD~DT2 PAD~D

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

G_CLK_DDC2

PEG_MRX_GTX_N0

PEG_MRX_GTX_P0

VGA_VSYNC

VGA_HSYNC

PEG_MTX_GRX_C_N0

PEG_MRX_GTX_N2

PEG_MRX_GTX_N1

PEG_MRX_GTX_P7

PEG_MRX_GTX_P4

PEG_MRX_GTX_P6

PEG_MRX_GTX_P3

PEG_MRX_GTX_P2

PEG_MRX_GTX_P8

PEG_MRX_GTX_P5

PEG_MRX_GTX_P10

PEG_MRX_GTX_P15

PEG_MRX_GTX_P14

PEG_MRX_GTX_P9

PEG_MRX_GTX_P11

PEG_MRX_GTX_P12

PEG_MTX_GRX_C_N6

PEG_MTX_GRX_C_N2

PEG_MTX_GRX_C_N1

PEG_MTX_GRX_C_N4

PEG_MTX_GRX_C_N3

PEG_MTX_GRX_C_N8

PEG_MTX_GRX_C_N9

PEG_MTX_GRX_C_N5

PEG_MRX_GTX_P13

PEG_MTX_GRX_C_N15

PEG_MTX_GRX_C_N11

PEG_MTX_GRX_C_N10

PEG_MTX_GRX_C_N12

PEG_MTX_GRX_C_N13

PEG_MTX_GRX_C_P1

PEG_MTX_GRX_C_P3

PEG_MTX_GRX_C_P0

PEG_MTX_GRX_C_P2

PEG_MTX_GRX_C_P9

PEG_MTX_GRX_C_P13

PEG_MTX_GRX_C_P11

PEG_MTX_GRX_C_P8

PEG_MTX_GRX_C_P10

PEG_MTX_GRX_C_P6

PEG_MTX_GRX_C_P7

PEG_MTX_GRX_C_P12

PEG_MTX_GRX_C_P5

PEG_MTX_GRX_C_P14

PEG_MTX_GRX_C_P15

PEG_MTX_GRX_C_P4

PEGCOMP

VGA_BLU

CRT_RGB#

CRT_RGB#

LCD_ACLK+_NB

L_IBG

ENVDD

LCTLA_CLK

LCTLB_DATA

LDDC_DATA

LDDC_CLK

LCD_A0+_NB

LCD_A1+_NB

LCD_ACLK-_NB

LCD_A2+_NB

LCD_A2-_NB

LCD_A1-_NB

LCD_A0-_NB

PEG_MTX_GRX_C_N7

PEG_MTX_GRX_C_N14

VGA_GRN

VGA_RED

CRT_IREF

PEG_MTX_GRX_N0

PEG_MTX_GRX_P0PEG_MTX_GRX_C_P0

PEG_MTX_GRX_C_N0

PEG_MTX_GRX_C_P1

PEG_MTX_GRX_C_N1

PEG_MTX_GRX_C_P2

PEG_MTX_GRX_C_N2

PEG_MTX_GRX_C_N3

PEG_MTX_GRX_C_P3

PEG_MTX_GRX_C_P4

PEG_MTX_GRX_C_N4

PEG_MTX_GRX_C_N5

PEG_MTX_GRX_C_P5

PEG_MTX_GRX_C_P6

PEG_MTX_GRX_C_N6

TV_C_NB

TV_CVBS_NB

TVIREF

TV_Y_NB

PEG_MTX_GRX_C_P7

PEG_MTX_GRX_C_N7

PEG_MTX_GRX_C_N8

PEG_MTX_GRX_C_P8

PEG_MTX_GRX_C_P9

PEG_MTX_GRX_C_N9

PEG_MTX_GRX_C_P10

PEG_MTX_GRX_C_N10

PEG_MTX_GRX_C_N11

PEG_MTX_GRX_C_P11

PEG_MTX_GRX_C_P12

PEG_MTX_GRX_C_N12

PEG_MTX_GRX_C_N13

PEG_MTX_GRX_C_P13

PEG_MTX_GRX_C_P14

PEG_MTX_GRX_C_N14

PEG_MTX_GRX_C_P15

PEG_MTX_GRX_C_N15

PEG_MTX_GRX_P1

PEG_MTX_GRX_N1

PEG_MTX_GRX_N2

PEG_MTX_GRX_P2

PEG_MTX_GRX_P3

PEG_MTX_GRX_N3

PEG_MTX_GRX_N4

PEG_MTX_GRX_P4

PEG_MTX_GRX_N5

PEG_MTX_GRX_P5

PEG_MTX_GRX_P6

PEG_MTX_GRX_P7

PEG_MTX_GRX_N6

PEG_MTX_GRX_N7

PEG_MTX_GRX_P8

PEG_MTX_GRX_P9

PEG_MTX_GRX_N8

PEG_MTX_GRX_P10

PEG_MTX_GRX_N9

PEG_MTX_GRX_N10

PEG_MTX_GRX_N11

PEG_MTX_GRX_P11

PEG_MTX_GRX_N12

PEG_MTX_GRX_P12

PEG_MTX_GRX_N13

PEG_MTX_GRX_P13

PEG_MTX_GRX_P14

PEG_MTX_GRX_P15

PEG_MTX_GRX_N14

PEG_MTX_GRX_N15

PEG_MTX_GRX_P[0:15]

PEG_MTX_GRX_N[0:15]

PEG_MRX_GTX_P[0:15]

PEG_MRX_GTX_N[0:15]

BIA_PWM

LVREF

PEG_MRX_GTX_N3

PEG_MRX_GTX_N4

PEG_MRX_GTX_N5

CLK_DDC2

PEG_MRX_GTX_N6

PEG_MRX_GTX_N7

G_CLK_DDC2

G_DAT_DDC2

VGA_RED

VGA_BLU

VGA_GRN

CRT_IREF

VGA_HSYNC

VGA_VSYNC

PEG_MRX_GTX_N8

PEG_MRX_GTX_N9

PEG_MRX_GTX_N10

LCTLA_CLK

LCTLB_DATA

PEG_MRX_GTX_N11

PEG_MRX_GTX_N12

PEG_MRX_GTX_N13

PEG_MRX_GTX_N14

PEG_MRX_GTX_N15

TV_IRTN

TV_IRTN

LVREF

PEG_MRX_GTX_P1

VGA_RED

VGA_BLU

VGA_GRN

DAT_DDC2G_DAT_DDC2

TV_CVBS_NB

TV_Y_NB

TV_C_NB

TVIREF

PANEL_BKEN

+3.3V_RUN

+1.5V_RUN_PCIE

+3.3V_RUN

+1.5V_RUN

+1.5V_RUN

+1.05V_VCCP

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

LCD_A2-_NB<19>

LCD_A1-_NB<19>

LCD_A0-_NB<19>

LCD_A2+_NB<19>

LCD_A1+_NB<19>

LCD_A0+_NB<19>

LCD_ACLK-_NB<19>

LCD_ACLK+_NB<19>

PEG_MRX_GTX_P[0:15] <44>

PEG_MRX_GTX_N[0:15] <44>

PEG_MTX_GRX_N[0:15] <44>

PEG_MTX_GRX_P[0:15] <44>

CFG5<10>

CFG7<10>

CFG18<10>

CFG19<10>

CFG9<10>

CFG20<10>

CFG12<10>

CFG13<10>

CFG16<10>

CFG11<10>

PANEL_BKEN<19>

ENVDD<19>

TV_C_NB<20>

TV_Y_NB<20>

TV_CVBS_NB<20>

VGA_BLU<20>

VGA_GRN<20>

VGA_RED<20>

VGA_HSYNC<20>

VGA_VSYNC<20>

LDDC_DATA <19>

LDDC_CLK <19>

BIA_PWM<19>

DAT_DDC2 <20>

CLK_DDC2 <20>

CFG6<10>

CFG10<10>

Title

Size Document Number Rev

Date: Sheet

of

LA-3001P

0.4

Calistoga(3 of 6)

12 73Monday, April 17, 2006

Compal Electronics, Inc.

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

CFG5

CFG10

Low = Reserved

High = Mobility

*

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

High = Reverse Lane

LVREF for Alviso N.C

for Calistoga to GND

(DMI Lane Reversal)

SDVO_CTRLDATA

Low = No SDVO Device Present

High = SDVO Device Present

(Default)

(Default)

*

(FSB Dynamic ODT)

CFG16

CFG18

CFG19

*

High = Calistoga

Low = Moby Dick

Low = Calistoga

*

High = Reserved

Close to U9.J20

CFG[18:19] have internal pulldown

*

*

*

(VCC Select)

*

*

*

CFG7

CFG6

Low = DT/Transportable CPU

High = Mobile CPU

CFG[13:12]

CFG[3:17] have internal pullup

Strap Pin Table

CFG20

(PCIE/SDVO select)

High = PCIE/SDVO are

operating simu.

Low = Only PCIE or SDVO is

operational.

*

Close to U9.J22

(Default)

CFG11

Low = Normal

Operation (Default):

Lane number in Order

00 = Reserved

Low = 1.05V (Default)

High = 1.5V

High = Enabled

Low = Disabled

Low = Reverse Lane

CFG9

High = Normal Operation

*

Trace CRT_IREF should be at

least 25 mils away from any

other toggling signal.

High = DMI x 4

Low = DMI x 2

SDVO_CTRLDATA have internal pull down

Resistors Stuff Table

UMA

Discrete

R290,R305,R307,R308,R360

,R366,R301,R302,R303,R294

,R295,R292,R306,R304,R38

,R39,298,R299,

R271,R272,R273,R270,R53,

R358,R345,R266,R267,R268,

R371,R269

Stuff AC Caps For Discrete

NOTE:

1@ is for UMA Implemetation.

2@ is for Discrete Implementation.

R267 0_0402_5%~D2@

12

R271 0_0402_5%~D2@

12

C107 0.1U_0402_16V4Z~D 2@

1 2

C123 0.1U_0402_16V4Z~D 2@

1 2

R276 2.2K_0402_5%~D

@

C106 0.1U_0402_16V4Z~D 2@

1 2

R56 1K_0402_5%~D@

1 2

C61 0.1U_0402_16V4Z~D 2@

1 2

R266 0_0402_5%~D2@

12

R301 150_0402_1%~D1@

1 2

R304 0_0402_5%~D1@

12

C124 0.1U_0402_16V4Z~D 2@

1 2

R269 0_0402_5%~D2@

12

C105 0.1U_0402_16V4Z~D 2@

1 2

C91 0.1U_0402_16V4Z~D 2@

1 2

R358 0_0402_5%~D2@

12

R268 0_0402_5%~D2@

12

C74 0.1U_0402_16V4Z~D 2@

1 2

R299

2.2K_0402_5%~D1@

12

C112 0.1U_0402_16V4Z~D 2@

1 2

C140 0.1U_0402_16V4Z~D 2@

1 2

R57 1K_0402_5%~D@

1 2

C134 0.1U_0402_16V4Z~D 2@

1 2

R295 10K_0402_5%~D1@

1 2

C94 0.1U_0402_16V4Z~D 2@

1 2

R277 2.2K_0402_5%~D@

1 2

R307

150_0402_1%~D1@

12

R294 10K_0402_5%~D1@

1 2

R329 2.2K_0402_5%~D@

1 2

C79 0.1U_0402_16V4Z~D 2@

1 2

R308

150_0402_1%~D1@

12

C147 0.1U_0402_16V4Z~D 2@

1 2

R273 0_0402_5%~D2@

12

G

D

S

Q18

BSS138_SOT23~D1@

2

13

C120 0.1U_0402_16V4Z~D 2@

1 2

R310 2.2K_0402_5%~D@

1 2

C63 0.1U_0402_16V4Z~D 2@

1 2

R306 0_0402_5%~D1@

12

R274 2.2K_0402_5%~D@

1 2

C87 0.1U_0402_16V4Z~D 2@

1 2

R302 150_0402_1%~D1@

1 2

R292 0_0402_5%~D1@

12

C116 0.1U_0402_16V4Z~D 2@

1 2

LVDS

TV CRT

PCI-EXPRESS GRAPHICS

U9C

CALISTOGA A0_FCBGA1466~D

SDVOCTRL_CLK

H28

SDVOCTRL_DATA

H27

LA_DATA0

B37

LA_DATA1

B34

LA_DATA2

A36

LVREFH

C33

LVREFL

C32

TVDAC_A

A16

TVDAC_B

C18

TVDAC_C

A19

TV_IREF

J20

TV_IRTNA

B16

TV_IRTNB

B18

TV_IRTNC

B19

DDCCLK

C26

DDCDATA

C25

LA_DATA#0

C37

LA_DATA#1

B35

LA_DATA#2

A37

LB_DATA0

F30

LB_DATA1

D29

LB_DATA2

F28

LB_DATA#0

G30

LB_DATA#1

D30

LB_DATA#2

F29

LA_CLK

A32

LA_CLK#

A33

LB_CLK

E26

LB_CLK#

E27

LBKLT_CTL

D32

LBKLT_EN

J30

LCTLA_CLK

H30

LCTLB_DATA

H29

LDDC_CLK

G26

LDDC_DATA

G25

LVDD_EN

F32

LIBG

B38

LVBG

C35

VSYNC

H23

HSYNC

G23

BLUE

E23

BLUE#

D23

GREEN

C22

GREEN#

B22

RED

A21

RED#

B21

CRT_IREF

J22

EXP_COMPI

D40

EXP_COMPO

D38

EXP_RXN0

F34

EXP_RXN1

G38

EXP_RXN2

H34

EXP_RXN3

J38

EXP_RXN4

L34

EXP_RXN5

M38

EXP_RXN6

N34

EXP_RXN7

P38

EXP_RXN8

R34

EXP_RXN9

T38

EXP_RXN10

V34

EXP_RXN11

W38

EXP_RXN12

Y34

EXP_RXN13

AA38

EXP_RXN14

AB34

EXP_RXN15

AC38

EXP_RXP0

D34

EXP_RXP1

F38

EXP_RXP2

G34

EXP_RXP3

H38

EXP_RXP4

J34

EXP_RXP5

L38

EXP_RXP6

M34

EXP_RXP7

N38

EXP_RXP8

P34

EXP_RXP9

R38

EXP_RXP10

T34

EXP_RXP11

V38

EXP_RXP12

W34

EXP_RXP13

Y38

EXP_RXP14

AA34

EXP_RXP15

AB38

EXP_TXN0

F36

EXP_TXN1

G40

EXP_TXN2

H36

EXP_TXN3

J40

EXP_TXN4

L36

EXP_TXN5

M40

EXP_TXN6

N36

EXP_TXN7

P40

EXP_TXN8

R36

EXP_TXN9

T40

EXP_TXN10

V36

EXP_TXN11

W40

EXP_TXN12

Y36

EXP_TXN13

AA40

EXP_TXN14

AB36

EXP_TXN15

AC40

EXP_TXP0

D36

EXP_TXP1

F40

EXP_TXP2

G36

EXP_TXP3

H40

EXP_TXP4

J36

EXP_TXP5

L40

EXP_TXP6

M36

EXP_TXP7

N40

EXP_TXP8

P36

EXP_TXP9

R40

EXP_TXP10

T36

EXP_TXP11

V40

EXP_TXP12

W36

EXP_TXP13

Y40

EXP_TXP14

AA36

EXP_TXP15

AB40

TV_DCONSEL1

J29

TV_DCONSEL0

K30

C58 0.1U_0402_16V4Z~D 2@

1 2

R272 0_0402_5%~D2@

12

G

D

S

Q19

BSS138_SOT23~D1@

2

13

C129 0.1U_0402_16V4Z~D 2@

1 2

C68 0.1U_0402_16V4Z~D 2@

1 2

C71 0.1U_0402_16V4Z~D 2@

1 2

C80 0.1U_0402_16V4Z~D 2@

1 2

C137 0.1U_0402_16V4Z~D 2@

1 2

R371 0_0402_5%~D2@

12

R53 0_0402_5%~D2@

12

R275 2.2K_0402_5%~D@

1 2

C65 0.1U_0402_16V4Z~D 2@

1 2

R290 1.5K_0402_1%~D1@

12

R366

255_0402_1%~D1@

12

R303 150_0402_1%~D1@

1 2

R38

2.2K_0402_5%~D1@

12

R309 2.2K_0402_5%~D

@

C113 0.1U_0402_16V4Z~D 2@

1 2

C136 0.1U_0402_16V4Z~D 2@

1 2

C109 0.1U_0402_16V4Z~D 2@

1 2

R312 2.2K_0402_5%~D@

1 2

R360

4.99K_0402_1%~D1@

12

R270 0_0402_5%~D2@

12

C84 0.1U_0402_16V4Z~D 2@

1 2

R55 1K_0402_5%~D@

1 2

R311 2.2K_0402_5%~D@

1 2

C96 0.1U_0402_16V4Z~D 2@

1 2

R298

2.2K_0402_5%~D1@

12

C90 0.1U_0402_16V4Z~D 2@

1 2

R345 0_0402_5%~D2@

12

R305

150_0402_1%~D1@

12

C142 0.1U_0402_16V4Z~D 2@

1 2

R353

24.9_0402_1%~D

1 2

R39

2.2K_0402_5%~D1@

12

剩余56页未读,继续阅读

cage1015

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 深入理解23种设计模式

- 制作与调试:声控开关电路详解

- 腾讯2008年软件开发笔试题解析

- WebService开发指南:从入门到精通

- 栈数据结构实现的密码设置算法

- 提升逻辑与英语能力:揭秘IBM笔试核心词汇及题型

- SOPC技术探索:理论与实践

- 计算图中节点介数中心性的函数

- 电子元器件详解:电阻、电容、电感与传感器

- MIT经典:统计自然语言处理基础

- CMD命令大全详解与实用指南

- 数据结构复习重点:逻辑结构与存储结构

- ACM算法必读书籍推荐:权威指南与实战解析

- Ubuntu命令行与终端:从Shell到rxvt-unicode

- 深入理解VC_MFC编程:窗口、类、消息处理与绘图

- AT89S52单片机实现的温湿度智能检测与控制系统

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功