Allegro 16.3 ImportLogic与BackAnnotate教程

需积分: 9 57 浏览量

更新于2024-07-22

收藏 987KB PDF 举报

"allegro16.3教程1——导入逻辑与回注、网络列表比较、高级布线、约束管理及差分对"

Allegro 16.3 是一款强大的PCB设计软件,用于电路板布局和布线。本教程主要介绍了几个关键功能,包括ImportLogic(导入逻辑)、BackAnnotate(回注)、NetlistCompare(网络列表比较)、AdvancedPlacement(高级布线)以及ConstraintManagement(约束管理)和DifferentialPair(差分对)。

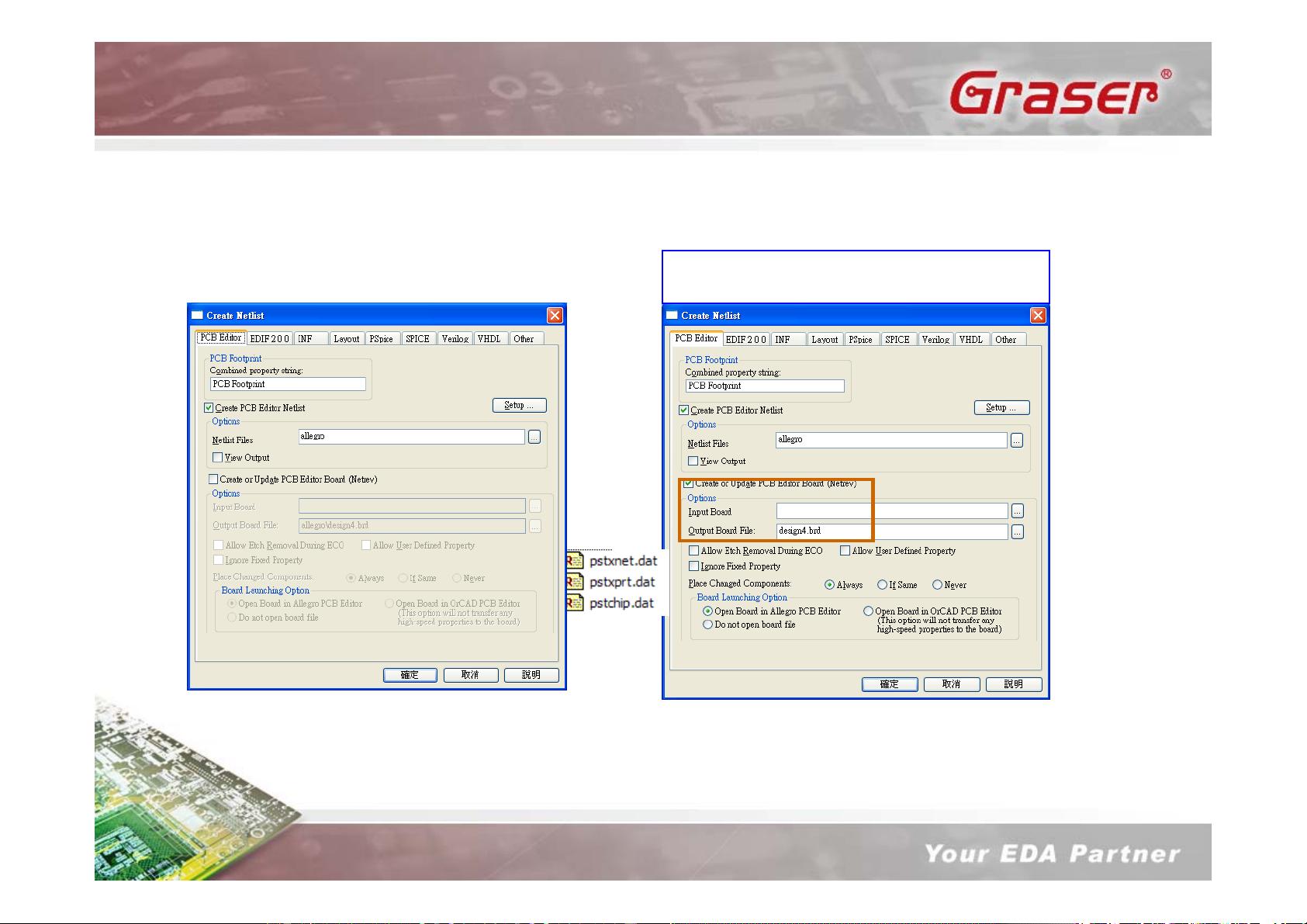

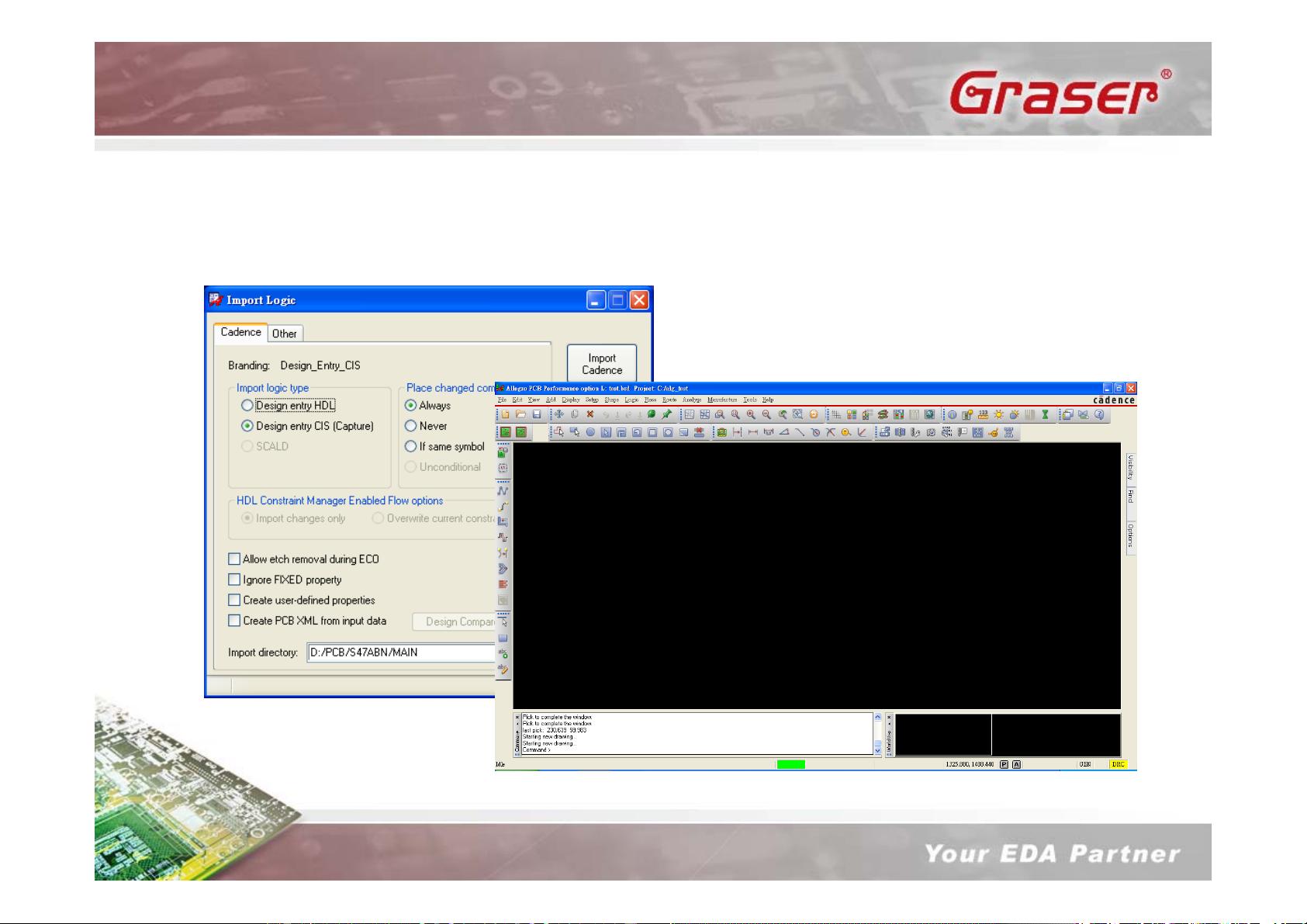

1. ImportLogic:

ImportLogic功能允许用户从其他设计工具,如Cadence OrcadCapture,导入或导出网络列表。这使得设计师能够在不同的设计环境中轻松地交换数据。通过Other选项,用户可以创建AllegroNetlist的.netfile,将Cadence Allegro与OrcadCaptureCIS之间的设计数据进行同步。然而,这种方法的一个缺点是,对于复杂的设计,导入和回注线路图可能变得困难,需要特定的Device文件和Swpfile。

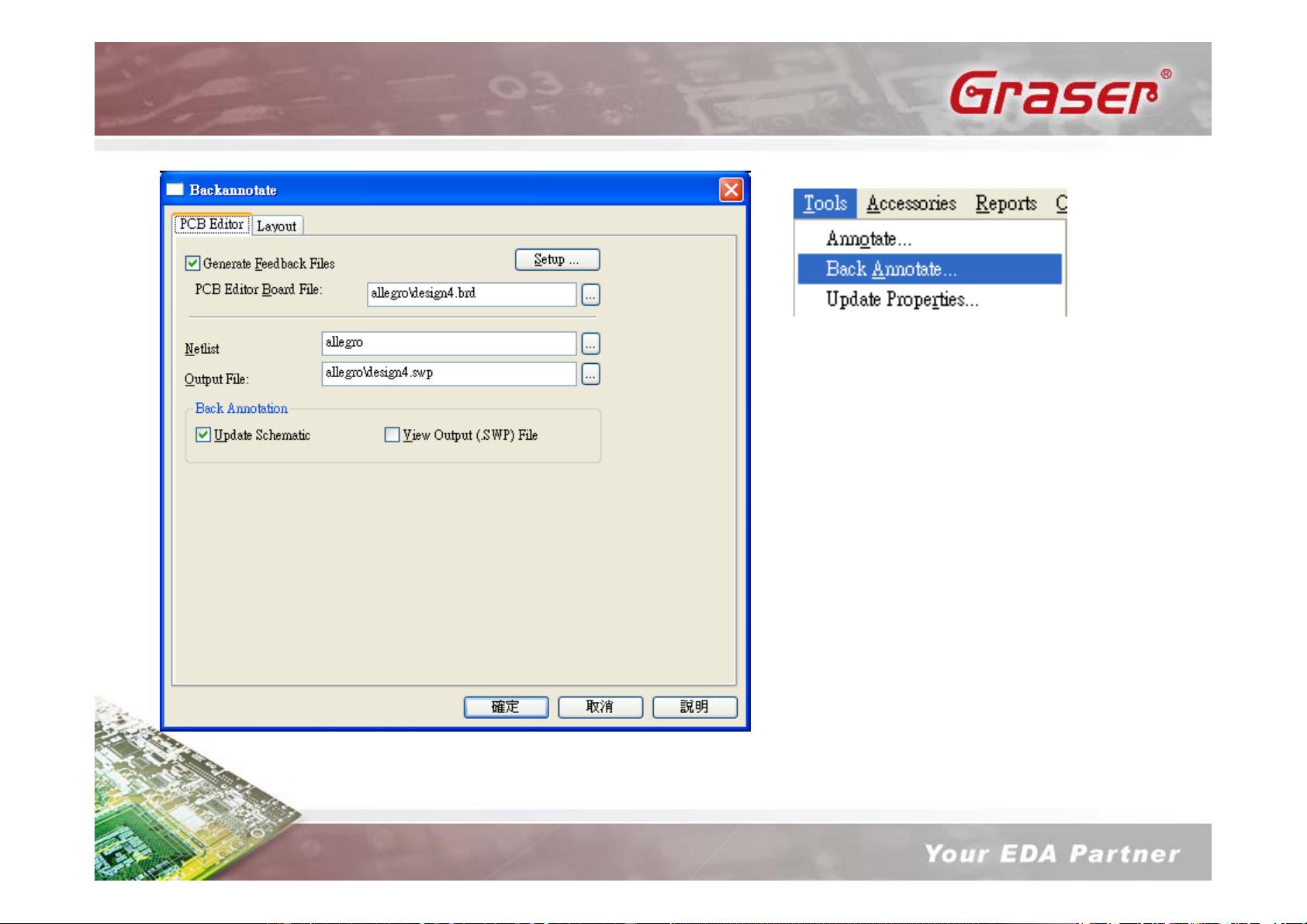

2. BackAnnotate:

BackAnnotate功能用于在Allegro中完成PCB布局后,将更改回注到原始的原理图(Capture)中。CaptureBackAnnotation .swpfile用于存储回注信息。优点是可以在Capture中定义设计变得更简单,但回注过程需要Swpfile,且对复杂设计可能较为繁琐。

3. NetlistCompare:

NetlistCompare工具用于比较两个不同版本的网络列表,帮助用户识别设计中的差异,确保更新的网络列表与之前的版本一致。这对于版本控制和团队协作至关重要,可以避免因设计更改导致的潜在错误。

4. AdvancedPlacement:

AdvancedPlacement特性提供了高级的元器件布局功能,允许用户根据规则和约束进行精确、高效的布线。这有助于优化PCB的空间利用率和电气性能。

5. ConstraintManagement:

约束管理功能使得设计者可以定义和管理各种设计规则,包括电气、物理和热约束。这些约束可以指导自动布线过程,确保设计符合规范和性能要求。

6. DifferentialPair:

DifferentialPair模块专注于差分信号对的布局和布线,这对于高速数字设计非常重要。它确保差分信号对保持正确的间距和匹配长度,以降低串扰,提高信号完整性。

在使用Allegro 16.3时,需要注意一个细节:在9.2版本之后,allegro.dll不再包含在程序中,需要从早期版本复制到新版本的指定路径下。这确保了与其他工具的兼容性和数据交换。

Allegro 16.3 提供了一整套工具来处理复杂的PCB设计任务,从网络列表的导入和导出,到回注,再到高级布线和约束管理,每个功能都旨在提高设计效率和质量。熟练掌握这些工具的使用,能帮助设计师在PCB设计领域取得更好的成果。

2013-04-19 上传

点击了解资源详情

2012-03-16 上传

2021-06-15 上传

2020-05-09 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

qq_28391533

- 粉丝: 0

- 资源: 1

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查