Allegro DFM Ravel Rule:丝印线段与亮铜PAD间距详细检查指南

56 浏览量

更新于2024-08-04

5

收藏 722KB PDF 举报

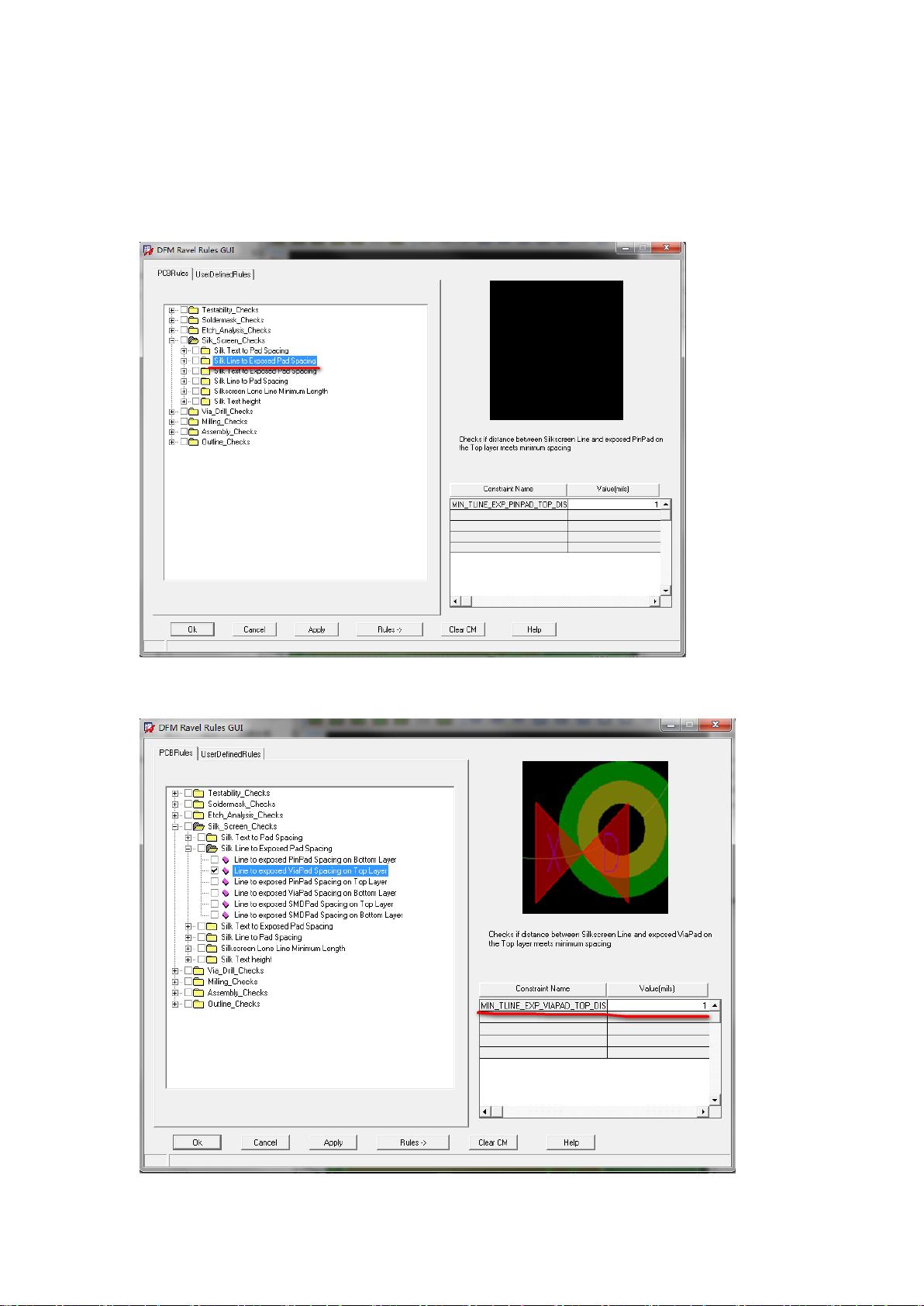

在 Allegro DFM (Design for Manufacturing) 的 Ravel Rule 功能中,丝印线段与亮铜PAD之间的间距检查是确保PCB制造质量的关键步骤。这个工具主要用于PCB设计阶段,特别是对于那些对精细间距控制有高要求的应用。以下是Ravel Rule在进行丝印线段与不同层次PAD间距检查时的具体内容:

1. **Top层过孔到丝印线段间距**:默认设置为1mil,但用户可以根据实际需要调整这一数值,以确保印刷电路板上的元件布局符合制造商的标准和最佳实践。

2. **Bottom层过孔到丝印线段间距**:同样检查这一层的连接性,以防止可能的干涉或制造问题。

3. **Top层通孔pin到丝印线段间距**:通孔针脚与丝印线段的距离需足够,避免印刷缺陷或电气干扰。

4. **Bottom层通孔pin到丝印线段间距**:这是另一个重要的电气隔离考虑,确保信号完整性不受影响。

5. **Top层表贴pad到丝印线段间距**:表贴元件(SMT)的间距管理至关重要,合适的间距有助于提高组装效率和减少不良品率。

6. **Bottom层表贴pad到丝印线段间距**:同样适用于SMT组件,保持合适的间距可以防止安装错误和提高整体设计质量。

Allegro Design and Analysis 工具集成了设计创作、PCB布局、库和设计数据管理功能,以实现从设计源头到成品的全程高质量、高效率流程。它通过灵活的逻辑约束驱动设计流,支持网络层次结构、总线和差分对的设计规则管理,显著提升了设计效率。具体而言:

- **设计创作**:提供模块化的设计过程,通过层次化和设计衍生功能优化复杂设计,提升编辑效率。强大的元件选择系统(CIS)帮助设计师快速确定适合的组件,缩短设计周期并降低成本。

- **并行工作**:让原理图设计者和PCB设计工程师能够协同工作,提高了设计团队的协作效率。

Allegro DFM Ravel Rule 的丝印线段到亮铜PAD间距检查是PCB制造流程中的一个关键环节,通过使用Allegro Design and Analysis的强大功能,设计师可以确保设计的可靠性和生产效率,从而减少产品上市时间。

2022-10-28 上传

2022-10-28 上传

2022-10-28 上传

2022-10-28 上传

2022-10-28 上传

2022-10-28 上传

点击了解资源详情

点击了解资源详情

2022-10-28 上传

不觉明了

- 粉丝: 3901

- 资源: 5759

最新资源

- 构建基于Django和Stripe的SaaS应用教程

- Symfony2框架打造的RESTful问答系统icare-server

- 蓝桥杯Python试题解析与答案题库

- Go语言实现NWA到WAV文件格式转换工具

- 基于Django的医患管理系统应用

- Jenkins工作流插件开发指南:支持Workflow Python模块

- Java红酒网站项目源码解析与系统开源介绍

- Underworld Exporter资产定义文件详解

- Java版Crash Bandicoot资源库:逆向工程与源码分享

- Spring Boot Starter 自动IP计数功能实现指南

- 我的世界牛顿物理学模组深入解析

- STM32单片机工程创建详解与模板应用

- GDG堪萨斯城代码实验室:离子与火力基地示例应用

- Android Capstone项目:实现Potlatch服务器与OAuth2.0认证

- Cbit类:简化计算封装与异步任务处理

- Java8兼容的FullContact API Java客户端库介绍