Cortex-M3技术详解:架构、编程模型与关键组件

Cortex-M3技术参考手册是一份详细介绍了ARM公司Cortex-M3微处理器架构和技术的文档。该手册旨在为开发人员提供关于Cortex-M3处理器设计、编程模型、系统控制、存储器映射以及异常处理的关键信息。

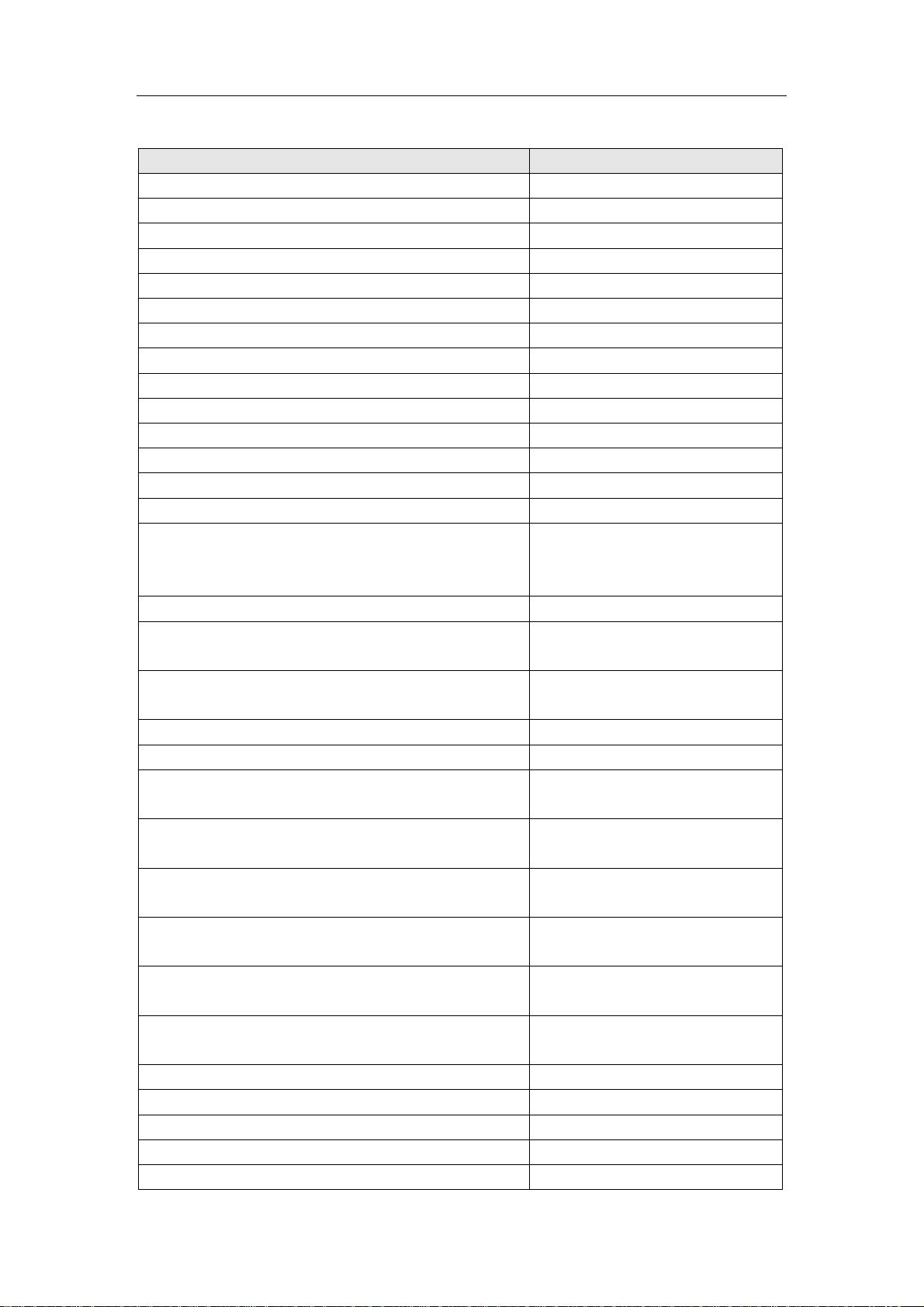

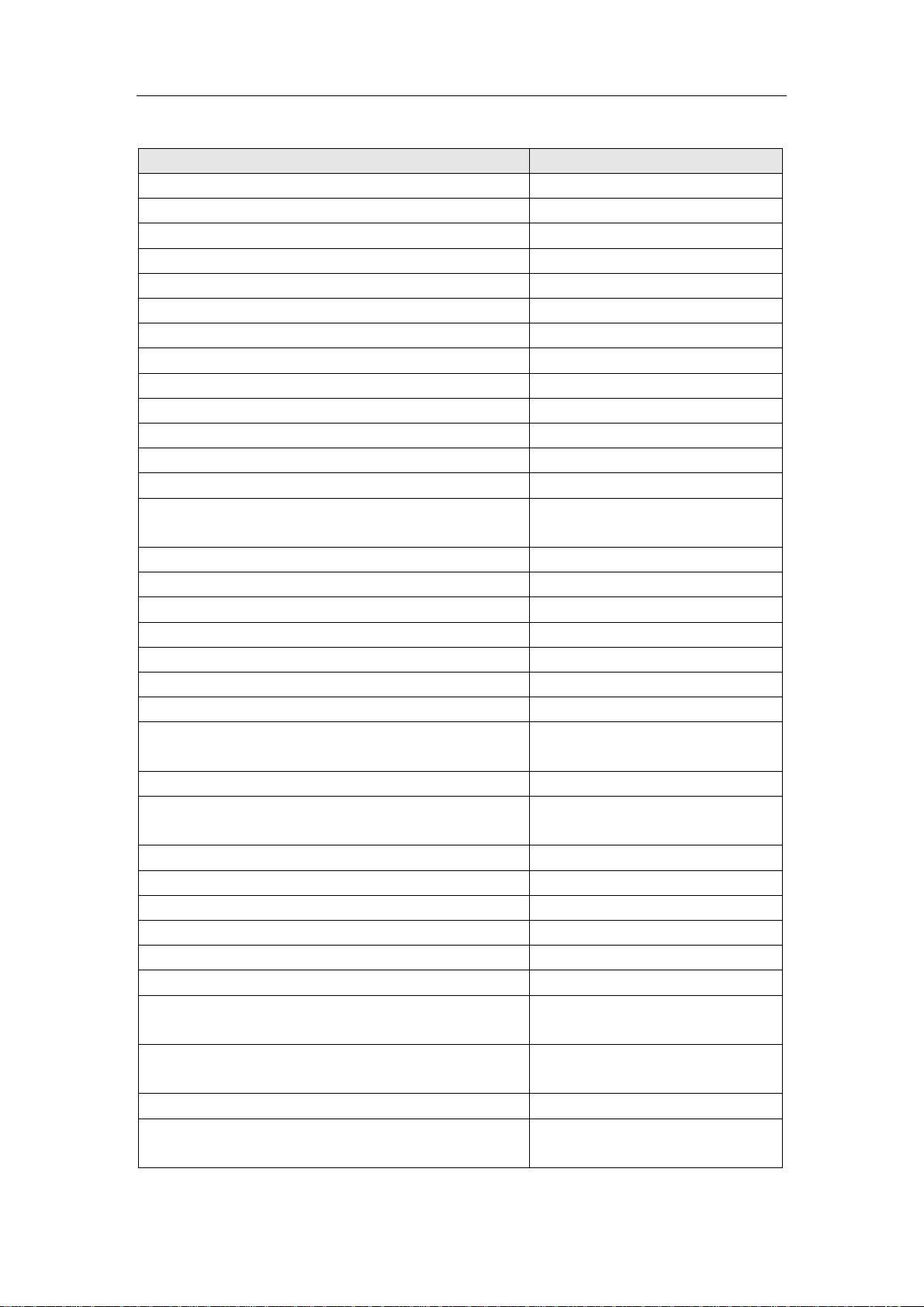

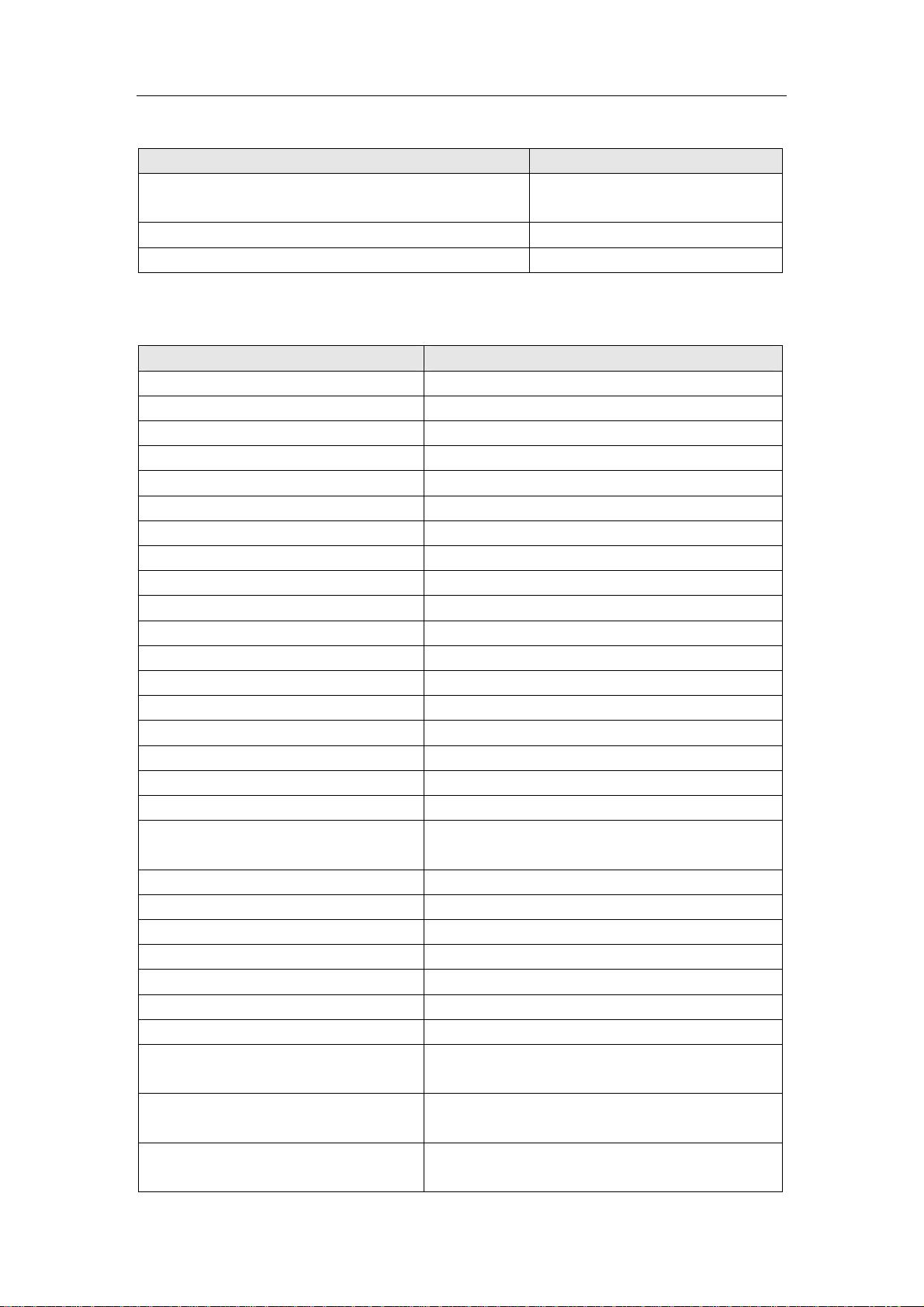

在第一章“概述”中,首先概述了处理器的基本概念,包括Cortex-M3处理器的特性和其组成部分。处理器内核是核心部分,负责执行指令;NVIC(Nested Vectored Interrupt Controller)是中断控制器,用于管理处理器的中断事件;总线矩阵支持数据传输;FPB(Flash Program Bus)、DWT(Data Watchpoint and Trace Unit)、ITM(In-Trace Macrocell)和ETM(Embedded Trace Macrocell)分别涉及闪存操作、调试功能和实时监控;MPU(Memory Protection Unit)用于内存空间管理和权限控制;TPIU(Trace Port Interface Unit)与ETM一起实现代码跟踪;SW/JTAG-DP(Software/JTAG Debug Port)则提供了调试接口。

第二章“编程模型”深入探讨了处理器的工作模式和状态,以及不同访问级别(特权和用户)的管理。通用寄存器和特殊用途的程序状态寄存器(xPSR)是编程中的关键要素。此外,数据类型和存储器格式也在此章节中得到详细介绍。

第三章“系统控制”主要关注处理器寄存器的组织和功能,如NVIC寄存器用于中断管理,调试寄存器支持调试操作,存储器保护单元的寄存器则确保了内存安全。跟踪端口接口和嵌入式跟踪宏单元的寄存器用于高级调试和追踪。

第四章“存储器映射”讨论了存储器的不同访问方式,包括Bit-banding技术,以及如何通过直接访问别名和bit-band区域进行操作。ROM存储器表的使用也在这一章有所提及。

第五章“异常”详述了异常处理机制,包括异常类型、优先级、特权和堆栈管理,以及异常的触发、处理流程,如中断的优先级分组、末尾连锁和延迟处理等。最后,复位过程及启动顺序的预期安排也进行了阐述。

这份技术参考手册为Cortex-M3微控制器的开发者提供了一套全面且深入的技术指南,涵盖了从硬件结构到软件编程的各个方面,是设计和优化Cortex-M3系统的重要参考资料。

137 浏览量

2022-07-14 上传

2010-08-18 上传

109 浏览量

点击了解资源详情

点击了解资源详情

白菜教主

- 粉丝: 29

- 资源: 48