LPDDR4信号完整性测试详解与指导

需积分: 0 54 浏览量

更新于2024-06-27

11

收藏 4.1MB DOCX 举报

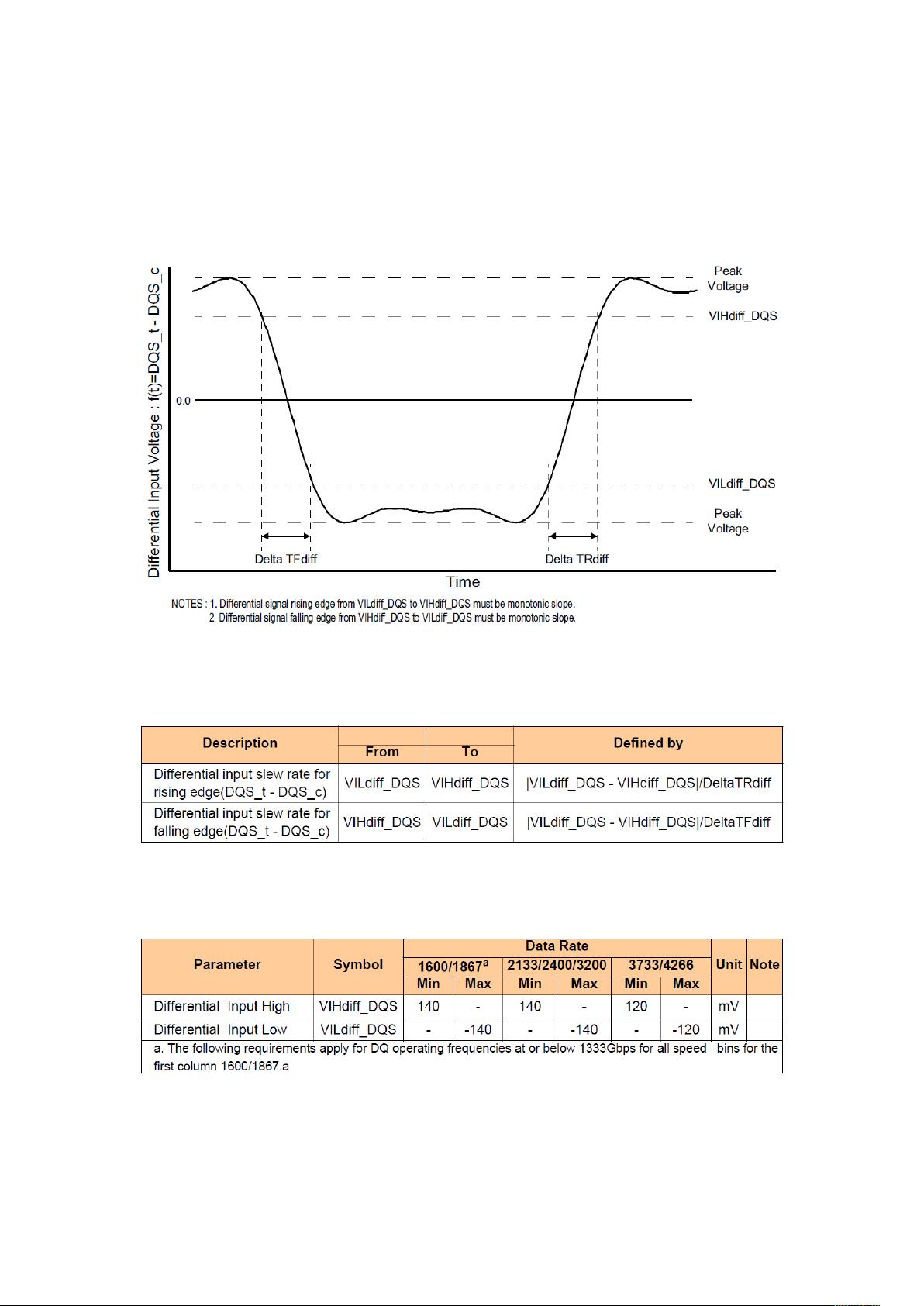

"本文档是关于LPDDR4(低功耗双倍数据速率第四代同步动态随机存取内存)信号完整性的测试指南,涵盖了CK时钟信号和DQS信号的测试,以及相关的时序测试标准。文档详细阐述了CK和DQS的差分和单端信号的各种参数,如电压、判定标准、输入斜率和交叉点,同时也提到了VREFCA和VREFDQ的调整。此外,还强调了平均时钟周期、平均高脉冲宽度和平均低脉冲宽度等关键时钟指标的测量方法,并对读时序进行了简要介绍。"

LPDDR4作为现代电子设备中的关键内存组件,其信号完整性对于系统的稳定运行至关重要。本测试指导主要关注两个核心信号:CK时钟信号和DQS数据选通信号。CK时钟信号是数据传输的基准,其差分和单端输入电压、判定标准、输入斜率和高低电平判决门限都需要精确测试和分析。测试过程中,CK的单端输入电压会受到VREFCA的影响,这需要通过查询寄存器MR12获取。

CK时钟信号的测试还包括对平均时钟周期(tCK(avg))、平均高脉冲宽度(tCH(avg))和平均低脉冲宽度(tCL(avg))的评估。这些指标用于确保时钟信号的稳定性,保证数据传输的准确性和速度。测量方法通常依赖于示波器,通过对多个时钟周期的采样来计算平均值。

DQS信号则是数据传输的同步信号,同样有差分和单端两种形式,测试内容与CK相似,但其单端输入电压受到VREFDQ的影响,需通过查询寄存器MR14获取。DQS的测试同样涉及交叉点判定标准,确保数据在正确的时间点被采样。

时序测试是确保LPDDR4性能的关键环节。对于每个Channel,需要分别测试LDQS和UDQS的读时序。其中,tDQSCK是重要的读时序参数,它描述了DQS输出访问时间相对于CK的时间关系,确保数据能够在正确的时钟边沿被读取。

这份LPDDR4信号完整性测试指导提供了详细的测试步骤和标准,有助于工程师在设计和调试过程中确保内存系统的可靠性和效率,从而保证整个系统性能的优化。

LSW20072007

- 粉丝: 10

最新资源

- Struts入门教程:从配置到实战

- Linux操作系统常用命令详解

- Struts入门:构建helloapp应用详解

- JavaMail API入门教程:发送与接收邮件

- Boson NetSim教程:静态路由与缺省路由配置实战

- BosonNetSim教程:Cisco设备模拟与实验环境搭建

- MATLAB图像处理命令概览:从applylut到bweuler

- O'Reilly《C#编程(第2版)》:入门与.NET框架详解

- Delphi单元测试工具DUnit详解与配置

- 创建JSP彩色验证码图像的方法

- WinSock网络编程:TCP/IP接口与应用

- 清华大学出版社《JAVA语言入门》

- C++/C编程最佳实践指南

- Div+CSS布局全攻略:从入门到高级实战

- Java Socket编程基础教程

- 面向对象设计模式:复用与灵活性的关键