使用Vivado HLS和System Generator实现浮点PID控制器

下载需积分: 16 | PDF格式 | 1.97MB |

更新于2024-07-22

| 32 浏览量 | 举报

"使用Vivado HLS和System Generator for DSP实现浮点PID控制器设计"

这篇文档“XAPP1163(v1.0)”是Xilinx公司于2013年1月发布的一份应用笔记,主要介绍了如何利用Vivado高速硬件描述语言(High-Level Synthesis, HLS)工具和System Generator for DSP来快速设计和优化浮点比例积分微分(PID)控制器的算法,并将其转化为硬件描述语言(RTL)设计。这个过程使得浮点算法设计师能够充分利用Xilinx FPGA设备的高性能、低成本和低功耗特性。

PID控制器是一种在工业控制领域广泛应用的算法,它通过比例(P)、积分(I)和微分(D)三个部分的组合来调整系统的响应。传统的PID控制器通常在微处理器上实现,因为C/C++代码能方便地捕捉、验证和调试这些算法,避免了硬件描述的复杂性。

Vivado HLS是一个强大的工具,它允许开发者用高级语言(如C、C++或OpenCL)来描述数字逻辑,然后自动生成相应的Verilog或VHDL代码。这种方式大大简化了FPGA设计流程,使设计人员可以更专注于算法本身,而非底层硬件细节。

System Generator for DSP是MathWorks公司的产品,它集成了Simulink环境和Xilinx的IP核,用于设计和仿真数字信号处理(DSP)系统。在这个案例中,它可以用来对Vivado HLS产生的设计进行分析和验证,确保浮点PID控制器的性能和正确性。

文档详细阐述了以下步骤:

1. **C/C++代码编写**:首先,将PID算法以C/C++的形式编写,包括比例、积分和微分部分。

2. **Vivado HLS集成开发**:导入C/C++代码到Vivado HLS环境中,设置相应的优化选项,比如循环展开、并行化等,以提升硬件执行效率。

3. **性能分析与调优**:通过Vivado HLS的性能报告,评估算法的延迟、资源利用率和功耗,根据需要进行代码优化。

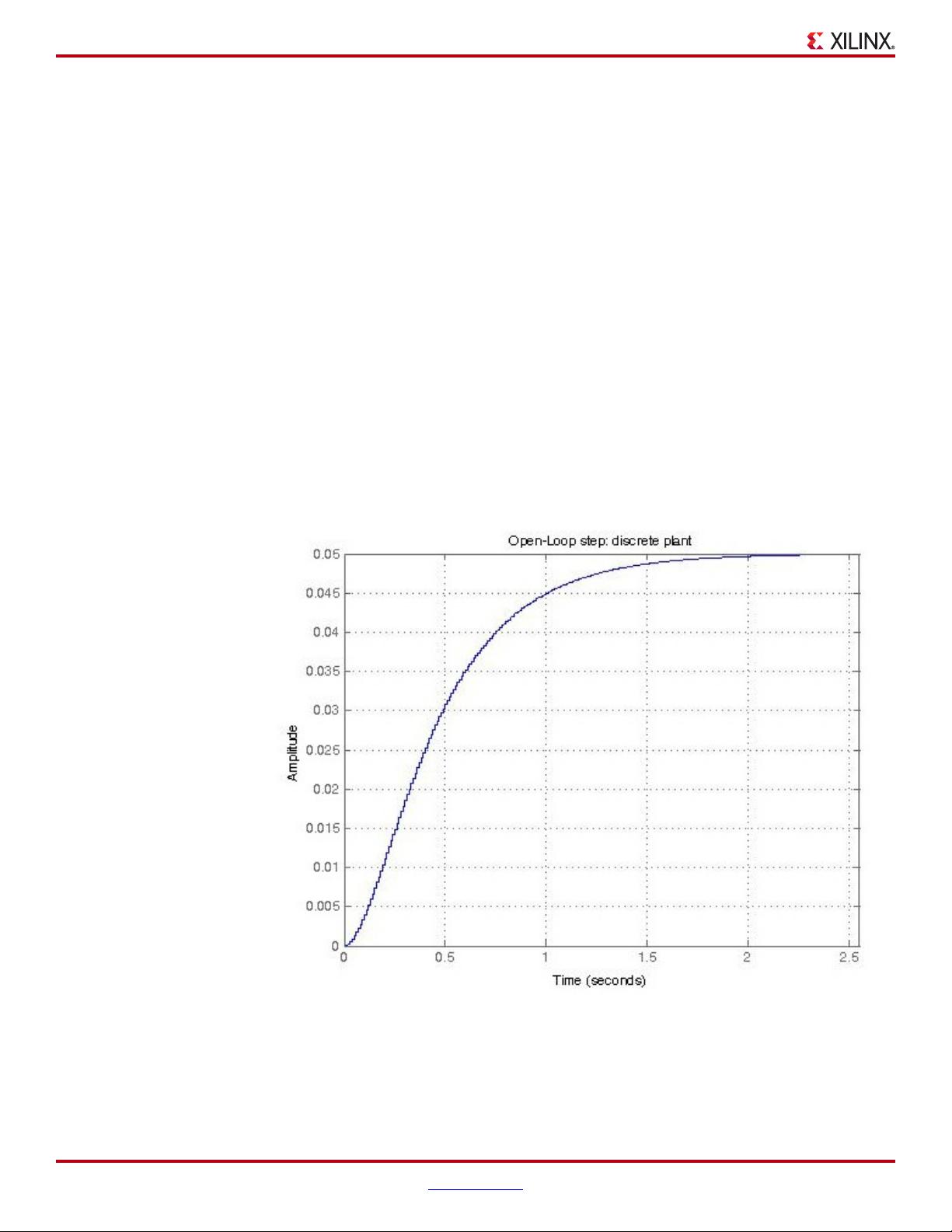

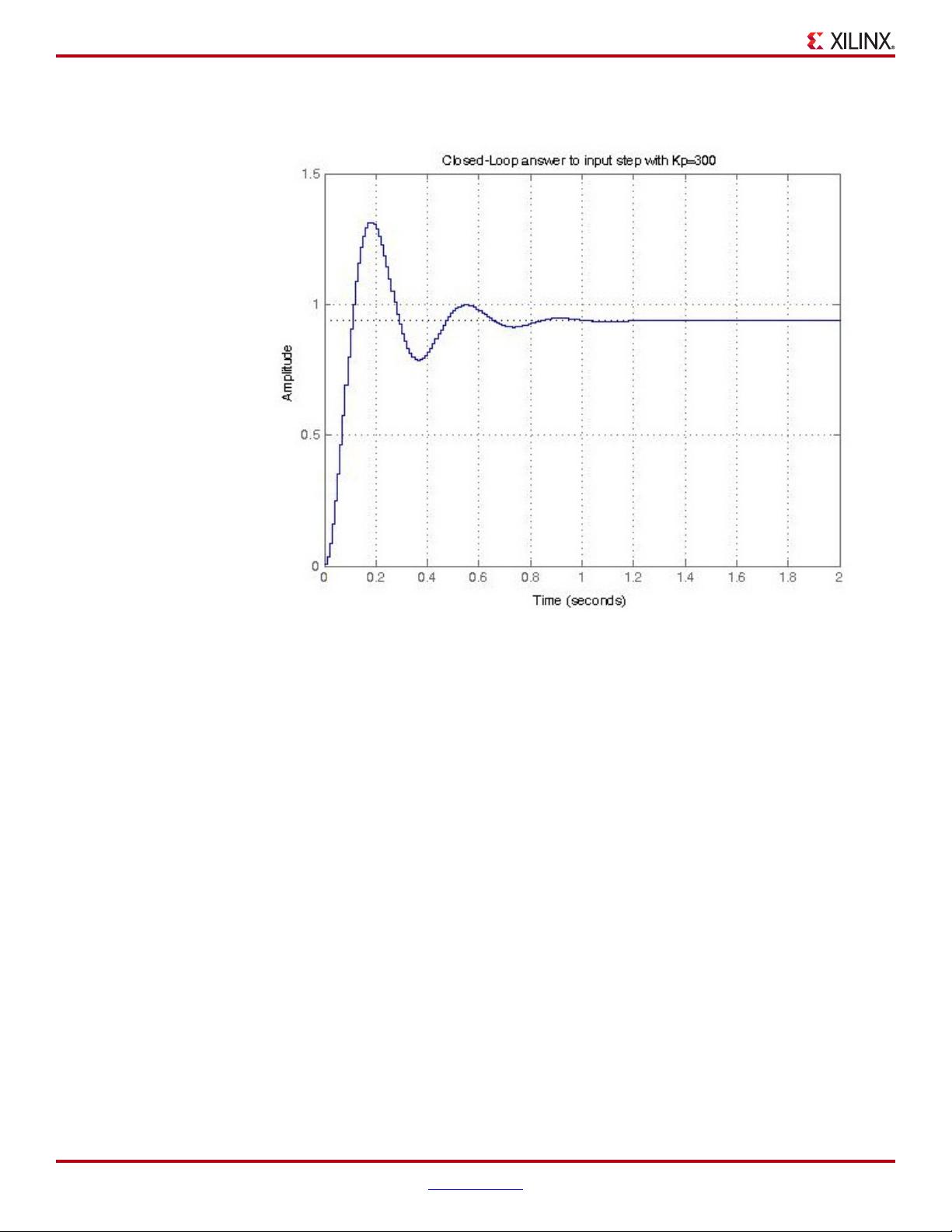

4. **System Generator验证**:在Simulink环境中建立模型,导入HLS生成的IP核,进行系统级仿真,验证控制器的控制效果和稳定性。

5. **综合与实现**:最后,将经过验证的设计综合成RTL代码,并在Xilinx FPGA平台上进行实现和部署。

通过这种方式,设计者可以在保持软件开发的便利性的同时,获得FPGA硬件加速的优势,实现了软硬件协同设计的高效流程。这种方法对于实时性和计算密集型的应用尤其有益,如工业自动化、航空航天、机器人控制等领域。

相关推荐

- 粉丝:

最新资源

- C#高效多线程下载器组件源码V1.12发布

- 32位Windows汇编语言程序设计大全

- Sketch插件库替换器:简化库更换流程

- 首版投资组合网站的开发与部署指南

- C语言实现农历与阳历转换的新库发布

- 探索Linux下的Vim优雅配色方案:Colibri.vim

- STM32 TFT显示技术与刷屏方法解析

- STM32单片机控制交通灯毕设资料整合

- Vitamio实现后台Service播放m3u8音频流

- 使用Docker封装的Alpine版Vim体验

- 步步高高级版WarNards开源项目发布

- 使用JNI实现Java调用VC6 DLL与Linux SO的DEMO教程

- STM32与OLED显示技术的实践应用

- 全面技术覆盖的小区物业管理系统设计与源码

- 清华版编译原理专业课答案解析

- Linux系统下nginx添加SSL配置的详细步骤