ModelSim 6.1入门:Verilog编程与工程建立教程

需积分: 13 156 浏览量

更新于2024-09-10

收藏 693KB PDF 举报

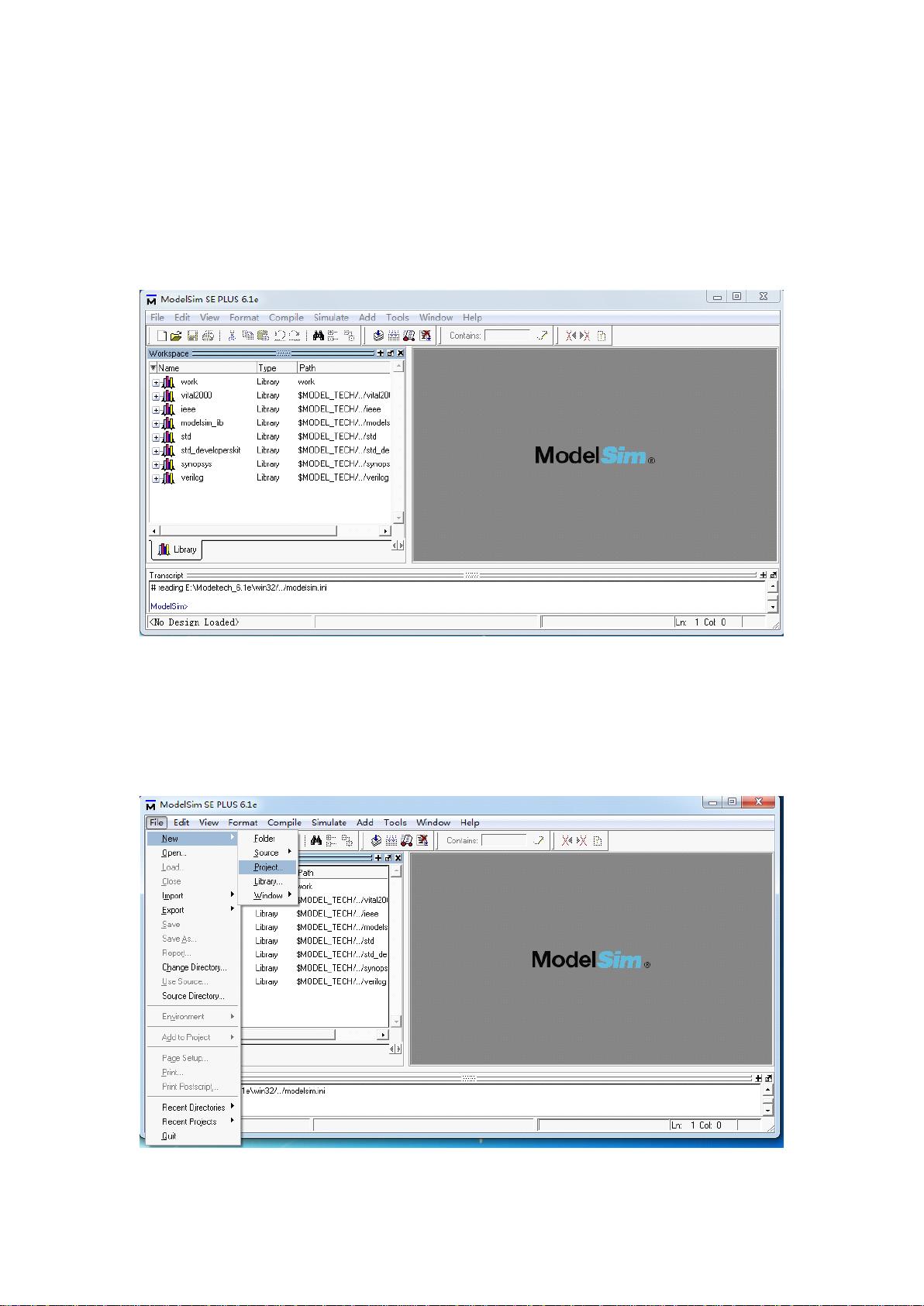

ModelSim 6.1入门级使用教程专注于帮助初学者快速掌握这款流行的FPGA验证工具。首先,我们了解到ModelSim的界面布局,它具有标准的Windows界面,包括菜单栏、快捷方式、工作空间、编辑区和交互区。工作空间用于管理项目中的文件,左边是库文件列表,右边则是代码编辑区域。

教程开始于创建工程,用户需在"ProjectName"中输入工程名称(例如"AND_2"),并选择存放路径。默认情况下,使用库名"work"。单击"OK"后,会在工作空间中看到新创建的工程文件,但此时文件状态显示为未编译的"?"。

接下来是编写Verilog代码,以一个简单的AND逻辑门电路为例。模块定义了输入clk、rst、A和B,以及输出C。使用always块来实现条件更新C的值。在编写完成后,确保模块名与工程名一致,以避免编译错误。

进行编译时,用户右键点击工程文件,选择"Compile" -> "Compile All",以对当前工程进行全面检查和编译。值得注意的是,尽管教程中的例子提到模块名和工程名可以不同,但在实际操作中保持一致通常更有利于理解和调试。

通过本教程,学习者将掌握如何使用ModelSim的基本操作,包括工程管理、代码编写和编译,这对于学习和实践Verilog设计至关重要。后续可能还会涉及仿真设置、波形观察和调试技巧,这些都将帮助用户逐步熟悉并熟练运用ModelSim进行FPGA的设计验证。

2018-01-06 上传

2014-06-26 上传

2012-07-09 上传

2007-09-04 上传

2010-05-16 上传

2010-02-26 上传

2008-12-18 上传

2013-08-26 上传

宁徛

- 粉丝: 3

- 资源: 6

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析