八路智力竞赛抢答器设计与改进

需积分: 12 25 浏览量

更新于2024-10-29

1

收藏 733KB PDF 举报

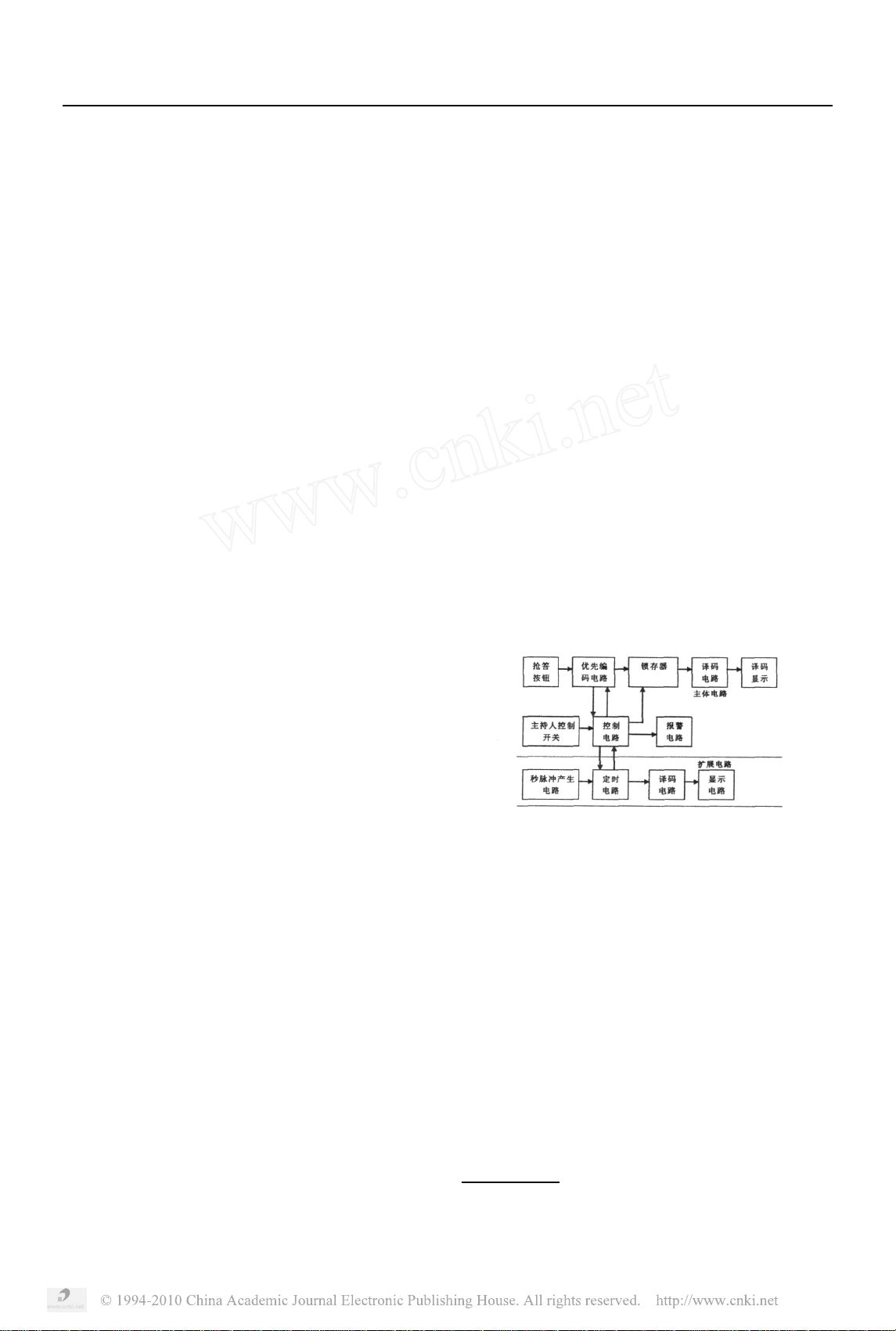

"八路智力竞赛抢答器的设计旨在提供一个适用于八组参赛者的电子电路设备,用于智力竞赛。该设备由主体电路和扩展电路两部分构成。主体电路包括优先编码电路、锁存器和译码电路,这些部分用于接收参赛组的输入,并在显示器上显示对应的信号。控制电路与主持人的开关结合,可以启动报警电路。扩展电路则通过定时电路和译码电路实现计时功能。设计方案详尽地阐述了抢答器的各个组成部分以及设计过程中的改良措施。"

本文中提到的八路智力竞赛抢答器是一个基于数字电路技术的装置,它利用了数字集成电路,如74LS148八路锁存器,来实现高集成度和低成本。该抢答器具备以下关键功能:

1. **优先编码**:当多个参赛者同时按下按钮时,优先编码电路确保最先按下按钮的参赛者信号被优先锁定。

2. **锁存器**:锁存器用于存储最先按下按钮的参赛组编号,直到主持人清除状态。

3. **译码电路**:译码电路负责将锁存的参赛组编号转换为显示器能显示的信号,通常使用数码管进行可视化。

4. **控制电路**:主持人通过控制开关启动或停止抢答过程,防止提前抢答的情况发生。

5. **报警电路**:一旦有选手成功抢答,或者在预设时间内无人抢答,报警电路会触发,通过扬声器发出声音提示。

6. **定时功能**:抢答器内置定时器,主持人可以设定抢答时间,如30秒。如果在设定时间内无人抢答,系统会发出警告,表示抢答时间结束。

7. **计时显示**:通过译码电路,定时电路的秒脉冲信号会在显示器上以倒计时的形式呈现,让所有参与者都能看到剩余时间。

这种抢答器相对于传统设计的改进之处在于其更先进的集成化设计,减少了分立元件的使用,降低了成本,同时增加了更多智能控制和保护机制,比如主持人控制的清零和开始功能,以及自动的计时和超时警告功能,提升了比赛的公平性和效率。

八路智力竞赛抢答器是一个集成了数字逻辑、时序控制和报警机制的复杂电子系统,它展示了数字电路在实际应用中的创新和实用性。这种设计不仅满足了现代电子技术对集成化和数字化的需求,也充分考虑了竞赛的规则和流程,确保了比赛的流畅进行。

2018-12-24 上传

2011-06-20 上传

点击了解资源详情

点击了解资源详情

2021-09-21 上传

2022-06-20 上传

kuangkaifeng

- 粉丝: 1

- 资源: 5

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析