基于Vivado的1Hz/64Hz LED驱动与256进制计数器设计

需积分: 5 155 浏览量

更新于2024-08-04

1

收藏 435KB PDF 举报

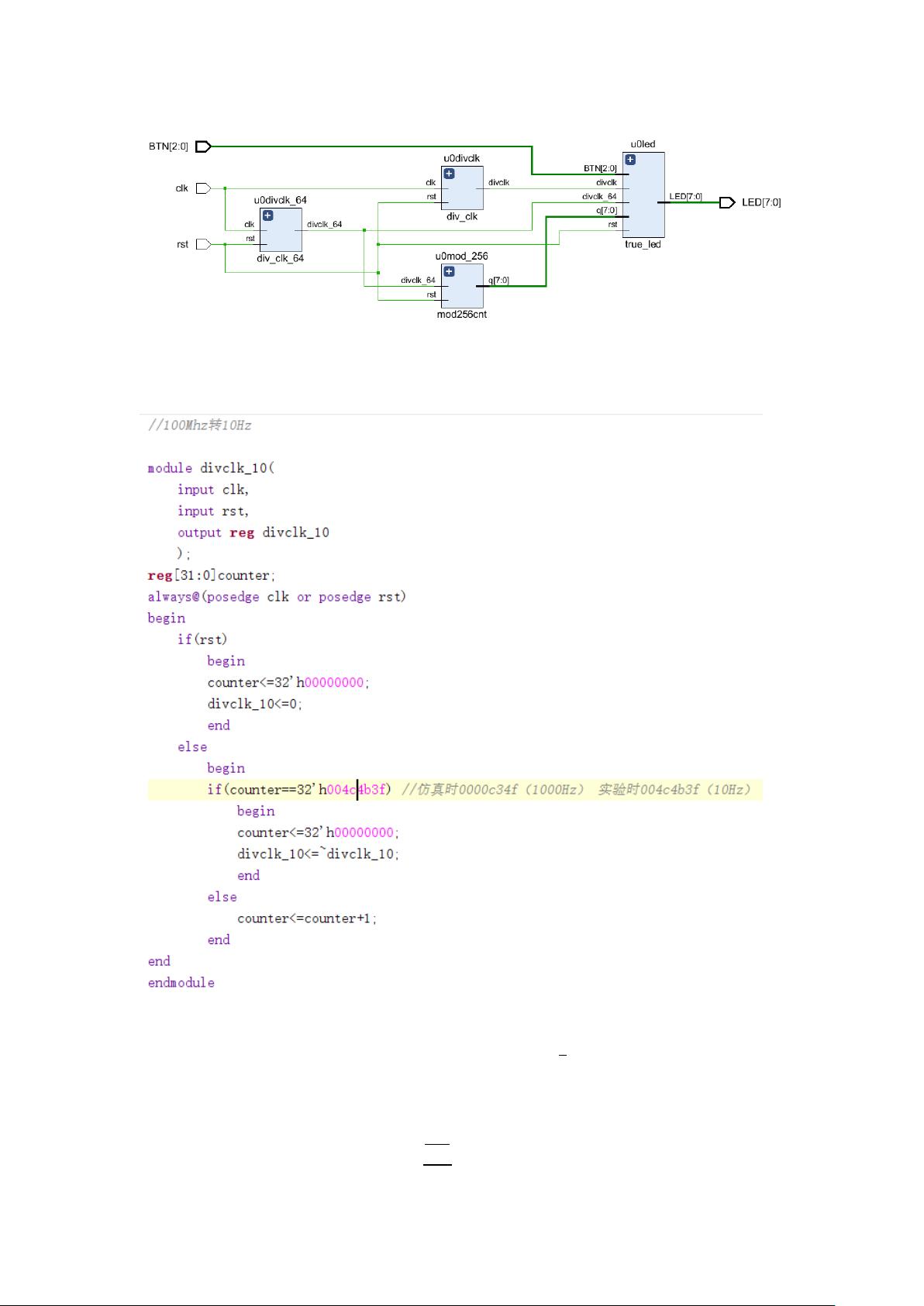

本实验是关于基于Xilinx Vivado平台实现LED驱动与控制的设计,采用Verilog语言进行编程。实验的主要目的是通过三个开关控制LED灯的不同显示模式,如全灭、左右移动、交替亮灭以及全亮状态,并模拟沙漏效果。硬件设备包括xc7a75tfgg484硬件开发板和Vivado工具。

实验内容分为两部分:

1. **LED控制逻辑**:

- 使用五个输入端口(rst, clk, 和三个按钮BTN)来控制LED灯的显示模式。开关组合对应不同的LED状态,如000代表全灭,001为左移,010为右移,011为交替亮灭,100为全亮。

- LED有7个输出端口,其中最后一个LED的亮灭周期需达到0.015625秒,即64Hz的频率,因此需要设计一个64Hz的分频器和一个256进制计数器,确保沙漏效果的正确显示。

2. **硬件与软件设计**:

- 实验设计采用Vivado工具,首先构建了一个1Hz的分频器(div_clk)以控制LED的总体变化周期,通过100MHz系统时钟分频得到1Hz的输出。实验频率调整为1000Hz时,用于仿真以便观察。

- 对于64Hz的分频器(div_clk_64),其工作原理与1Hz分频器类似,实验时的十六进制数值为000bebc1,而仿真时为00003d08(3200Hz)。

- mod256cnt计数器模块负责256进制计数,每64Hz时钟上升沿触发计数器加1,用于控制沙漏的周期性变化。

在整个设计过程中,学生需理解并运用Verilog语言进行模块化设计,包括顶层模块划分(div_clk, div_clk_64, mod256cnt, 和 true_ledLED设计模块),以及时序逻辑分析和计算分频因子。此外,实验还涉及硬件接口设计,如输入输出端口的连接和信号处理。通过这个项目,学生能够增强对数字逻辑设计、硬件描述语言以及Vivado工具的实际操作能力。

2023-04-14 上传

2021-09-20 上传

2024-03-10 上传

2020-08-10 上传

2021-09-30 上传

2021-11-20 上传

2014-07-14 上传

2021-09-30 上传

STDRM

- 粉丝: 0

- 资源: 4

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库