Verilog设计入门:3章综合解析

需积分: 9 118 浏览量

更新于2024-07-31

收藏 897KB PDF 举报

"EDA技术实用教程第4版的VERILOG课件主要讲解了Verilog语言在描述组合电路中的应用,特别关注了2选1、4选1和4选1多路选择器的Verilog描述,包括使用case语句、数据流描述方式以及if语句的表述方法。课程涵盖了模块定义、端口声明、赋值语句、关键字、标识符、程序格式、文件管理等多个方面,并深入探讨了reg型变量、过程语句、块语句、并位操作、等式操作符、连续赋值语句和wire型变量的定义。"

在Verilog HDL(硬件描述语言)中,用于描述组合电路的关键概念和元素有以下几个方面:

1. **模块表达**:Verilog中的基本单元是模块,它代表一个独立的硬件功能。模块包含输入、输出和内部信号,通过端口声明来定义。

2. **端口语句、端口信号名和端口模式**:端口声明定义了模块与其他模块之间的接口。端口可以设置为输入、输出或双向,并可以指定其信号类型。

3. **赋值语句**:Verilog有两种赋值方式,阻塞式赋值(`=`)和非阻塞式赋值(`<=`)。阻塞式赋值在当前时间步立即更新信号值,而非阻塞式赋值则在所有当前时间步的操作完成后才更新。

4. **条件操作符**:如`? :`,用于三元运算,可以在一条语句中实现条件判断和赋值。

5. **关键字和标识符**:Verilog预定义了一些关键字,如`module`、`input`、`output`等,而标识符用于定义自定义的变量、函数和模块名称。

6. **规范的程序书写格式**:良好的编程风格有助于代码的可读性和维护性,包括合理的缩进、注释和命名规则。

7. **文件取名和存盘**:正确命名和保存Verilog源文件对于项目的组织和编译至关重要。

在描述2选1、4选1和4选1多路选择器时,Verilog提供了多种方法:

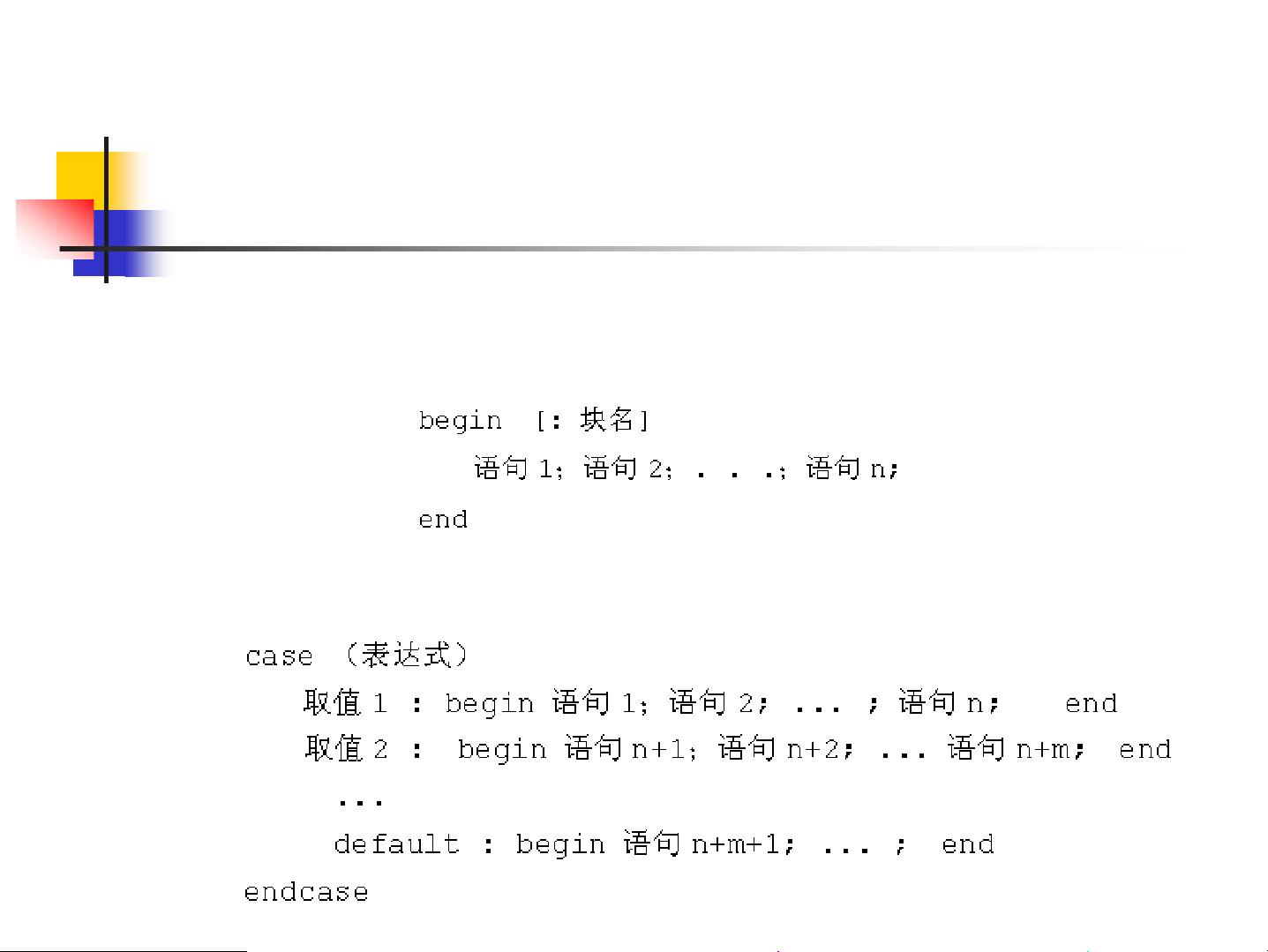

- **case语句**:常用于多路选择,根据输入选择相应的输出路径,例如在4选1多路选择器中,使用case语句可以简洁地表示逻辑选择。

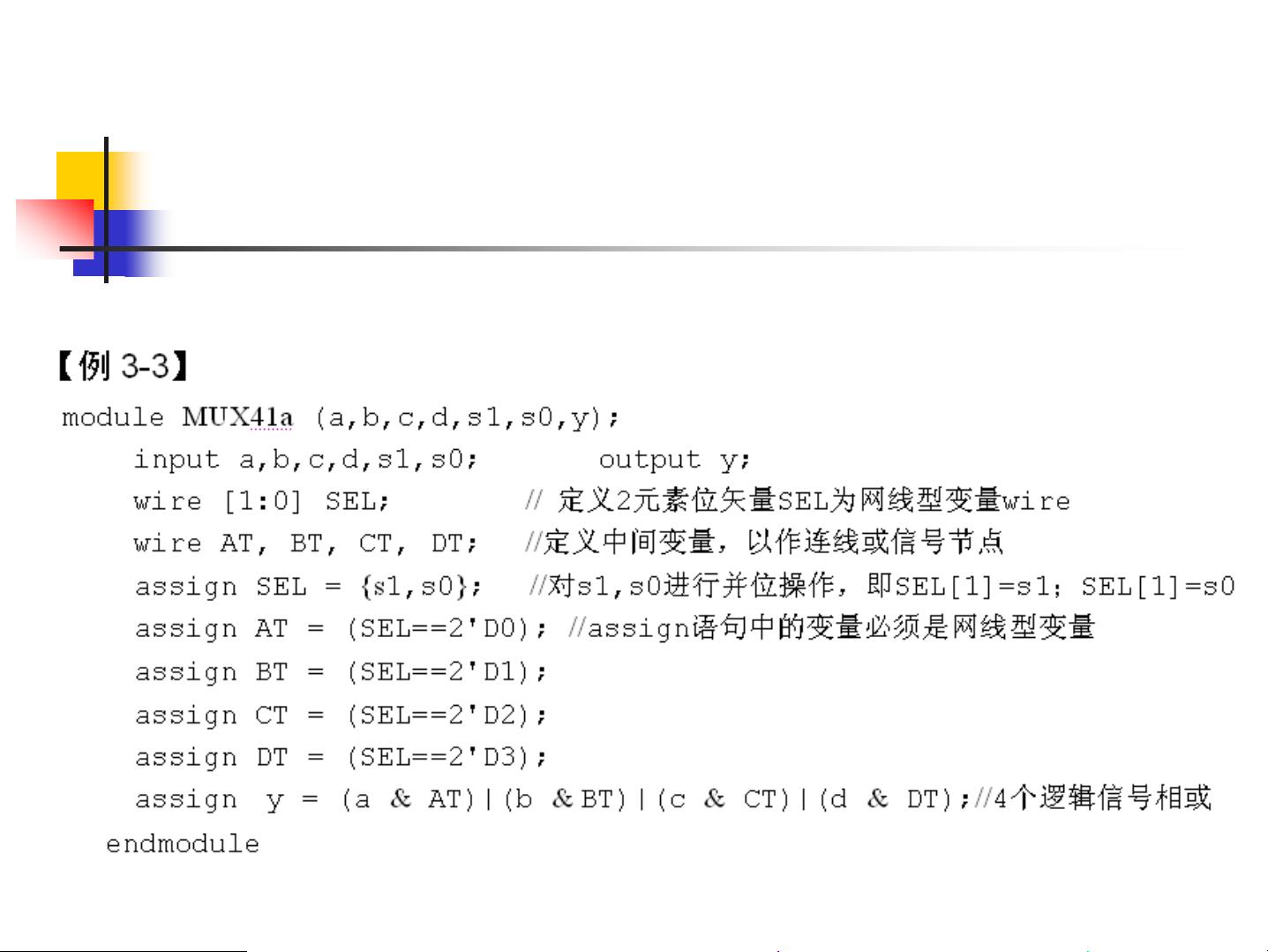

- **数据流描述方式**:使用`assign`语句进行连续赋值,适用于描述无延时的组合逻辑。在4选1多路选择器的实现中,可能用到按位逻辑操作符和等式操作符。

- **if语句**:if-else结构提供了一种条件分支的描述方法,可以根据不同的条件赋值给输出。

此外,`reg`型变量用于存储状态信息,而`wire`型变量则代表连接模块间的信号线。`begin-end`块语句用于组织代码,确保语句按照顺序执行。并位操作和注释符号也是Verilog编程中不可或缺的部分,它们帮助构建复杂的逻辑电路和提高代码可读性。

这个教程深入浅出地介绍了Verilog语言的基础知识,特别是如何利用这些知识来描述和实现各种组合逻辑电路,对于学习和理解EDA技术以及Verilog HDL编程具有极大的帮助。

点击了解资源详情

点击了解资源详情

172 浏览量

2022-07-14 上传

2018-02-28 上传

721 浏览量

105 浏览量

2023-10-14 上传

zq1057978105

- 粉丝: 0

最新资源

- Java搜索引擎指南:Lucene实战

- Windows设备驱动开发详解

- Oracle DBA在Unix下的命令参考手册

- SOA深度解析:架构、价值与构建技术

- ActiveReports实战教程:从入门到精通

- 优化ASP.Net性能:十大技巧解析

- C#数据库备份与恢复关键代码实现

- 国际开源大师齐聚北京:2008 Linux开发者研讨会

- ArcGIS二次开发实战指南

- 《开源》创刊:见证中国开源生态的崛起与转型

- Eclipse常用快捷键全解析:提升开发效率必备

- 使用Java将JTable数据导出到Excel

- 通用扑克牌程序源代码:数据结构与操作

- TortoiseSVN客户端安装与使用教程

- C#定时执行BAT脚本:8点、9点与13点任务

- DWR入门教程:快速掌握Ajax整合与开发