FPGA实现的RPE-LTP语音编解码IP核设计:GSM时代的新突破

版权申诉

32 浏览量

更新于2024-06-25

收藏 515KB DOC 举报

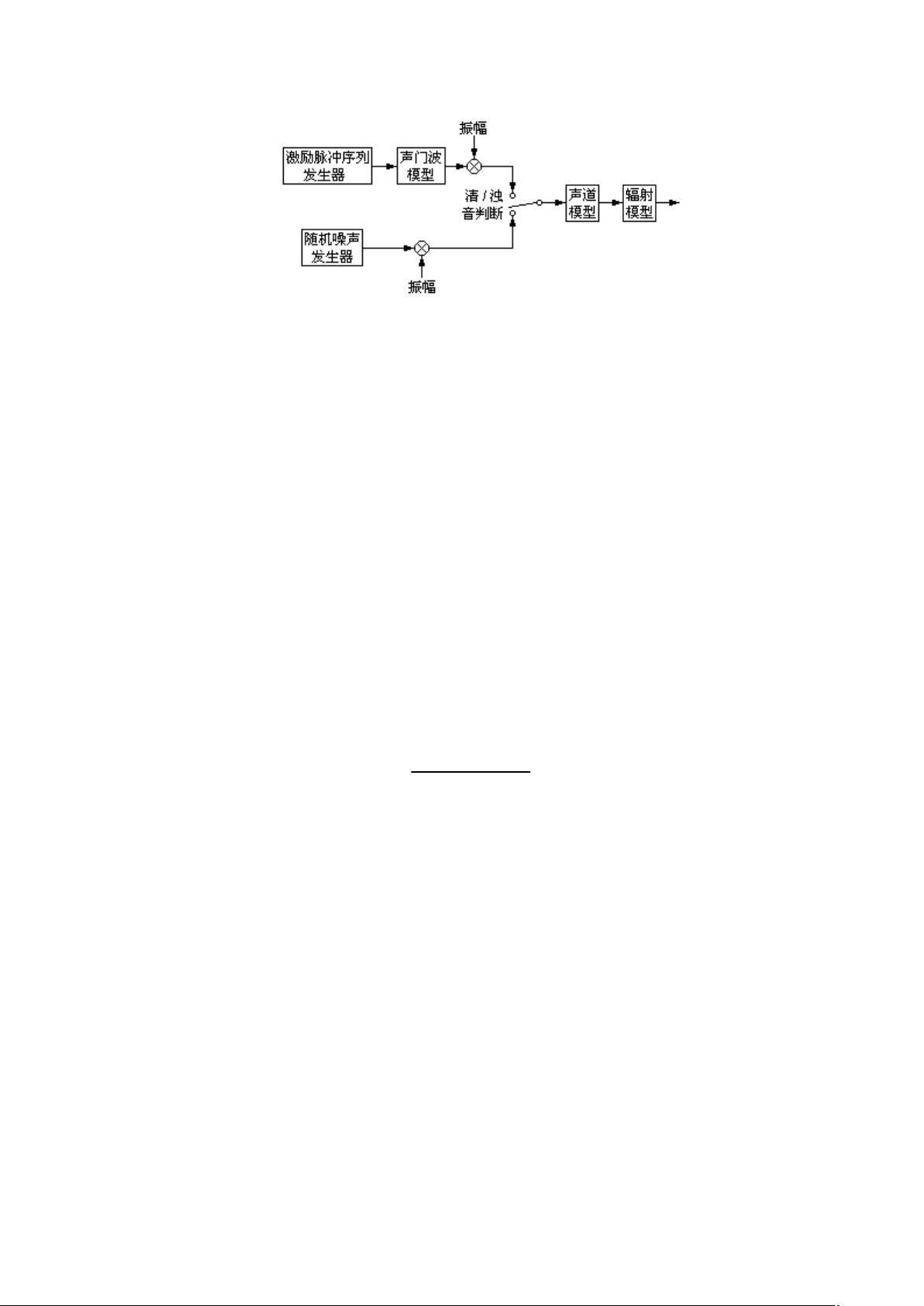

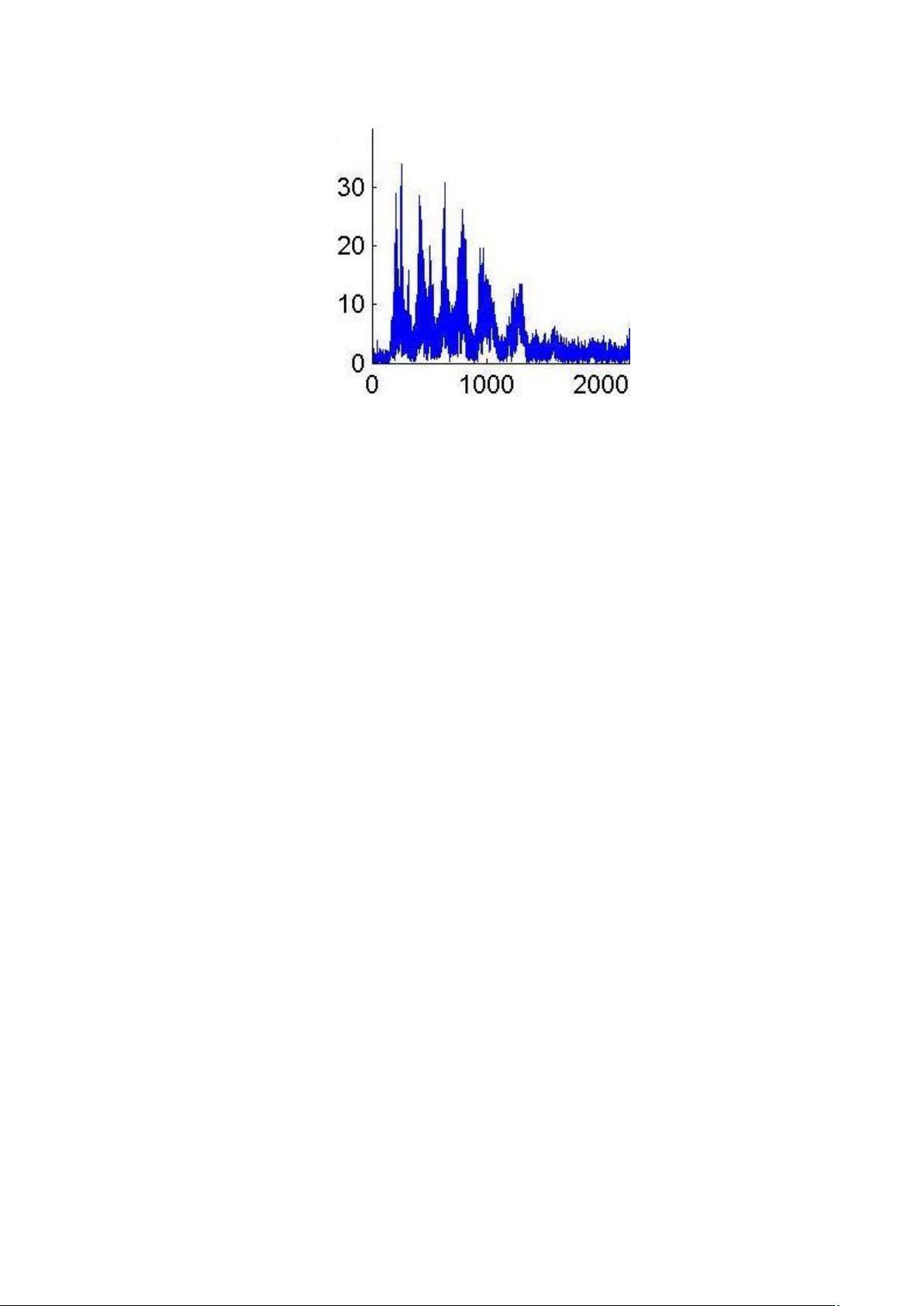

本文档主要探讨了基于FPGA(现场可编程门阵列)实现RPE-LTP(规则脉冲激励-长期预测)语音编解码算法的IP核设计。RPE-LTP算法是GSM全球移动通信系统中广泛使用的全速率语音编码标准,其特点是采用了20毫秒的帧结构,每帧包含160个语音样本,编码速率为13千比特每秒,能提供高质量的重建语音,MOS(Mean Opinion Score)评分超过3.6分。

尽管在早期的GSM通信系统中,由于DSP(数字信号处理器)技术的优势,大多数设计倾向于使用DSP来实现RPE-LTP算法。然而,随着集成电路技术的飞速发展,FPGA作为一种灵活且高性能的平台,逐渐被业界关注。FPGA提供了并行处理能力,能够实现实时和低延迟的语音编解码,对于现代移动通信设备中的基带处理来说,具有很大的吸引力。

本研究项目旨在推动GSM/CDMA双模手机基带物理层的关键技术研发,特别提出了将RPE-LTP语音编解码算法移植到FPGA上的创新设计思路。作者不仅完成了VHDL(Verilog Hardware Description Language)程序的编写和设计工作,还进行了详细的算法分析和仿真验证。根据不同的需求条件,设计团队探讨了多种实现策略,以适应FPGA的特性,如高效的硬件资源管理和优化的算法实现。

关键词:RPE-LTP,语音编解码,FPGA,GSM,数字信号处理器,基带物理层,VHDL。这项工作不仅提升了语音处理的性能,而且展示了如何利用现代集成电路技术来优化传统算法在移动通信设备中的应用,为后续的无线通信系统设计提供了新的参考和实践案例。

451 浏览量

2025-01-09 上传

2025-01-09 上传

2025-01-09 上传

2025-01-09 上传

omyligaga

- 粉丝: 97

- 资源: 2万+

最新资源

- vominhtri1991qn:我的GitHub个人资料的配置文件

- 2008最值得阅读的营销培训教材《口碑营销》

- 量子计算机仿真器

- learn-react-day-by-day:每天学习reactJs

- openvox-sms-app:Openvox-sms 演示

- Status-Page:开源状态页软件

- 高质量C#源码.rar

- CardGameLinkedList:在春假期间要做的简单项目。 两名玩家获得每套衣服的同等数量的卡牌,并且每位玩家将卡牌放置在桌上。 当玩家拥有匹配的卡牌时,他们将从牌桌上拿走所有卡牌。 游戏结束10回合后结束,或者一名玩家拥有了所有卡牌[需要增加更多回合]

- rt-thread-code-stm32f407-rt-spark.rar星火号 STM32F407是开发板

- 组织发展新人成长总动员

- git22:测试笔记本

- todolist自己版本02.zip

- 电子功用-基于嵌套混响室的材料电磁脉冲屏蔽效能测试系统及其测试方法

- notifications-test-app:Web应用程序以测试通知服务

- ANP

- ToolBot:bot Discord ToolBot的代码源