FPGA在变频率数据采集时序控制中的应用研究

需积分: 20 140 浏览量

更新于2024-07-25

1

收藏 782KB DOC 举报

“基于FPGA的变频率数据采集时序控制器设计,本科毕业论文,探讨了FPGA在变频率数据采集中的应用,通过FPGA实现时序控制器,以满足不同频率信号的采集需求。”

本文主要研究了基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的变频率数据采集时序控制器设计。在信号与信息系统中,变频率数据采集是一个至关重要的环节,它涉及到数字信号处理的关键技术。FPGA作为一种超大规模、超高速的可编程逻辑器件,由于其高集成度、高速度和可编程性,使得数字系统设计变得更加高效、灵活和可靠,尤其在处理超高速信号和实时测控领域具有广泛的应用。

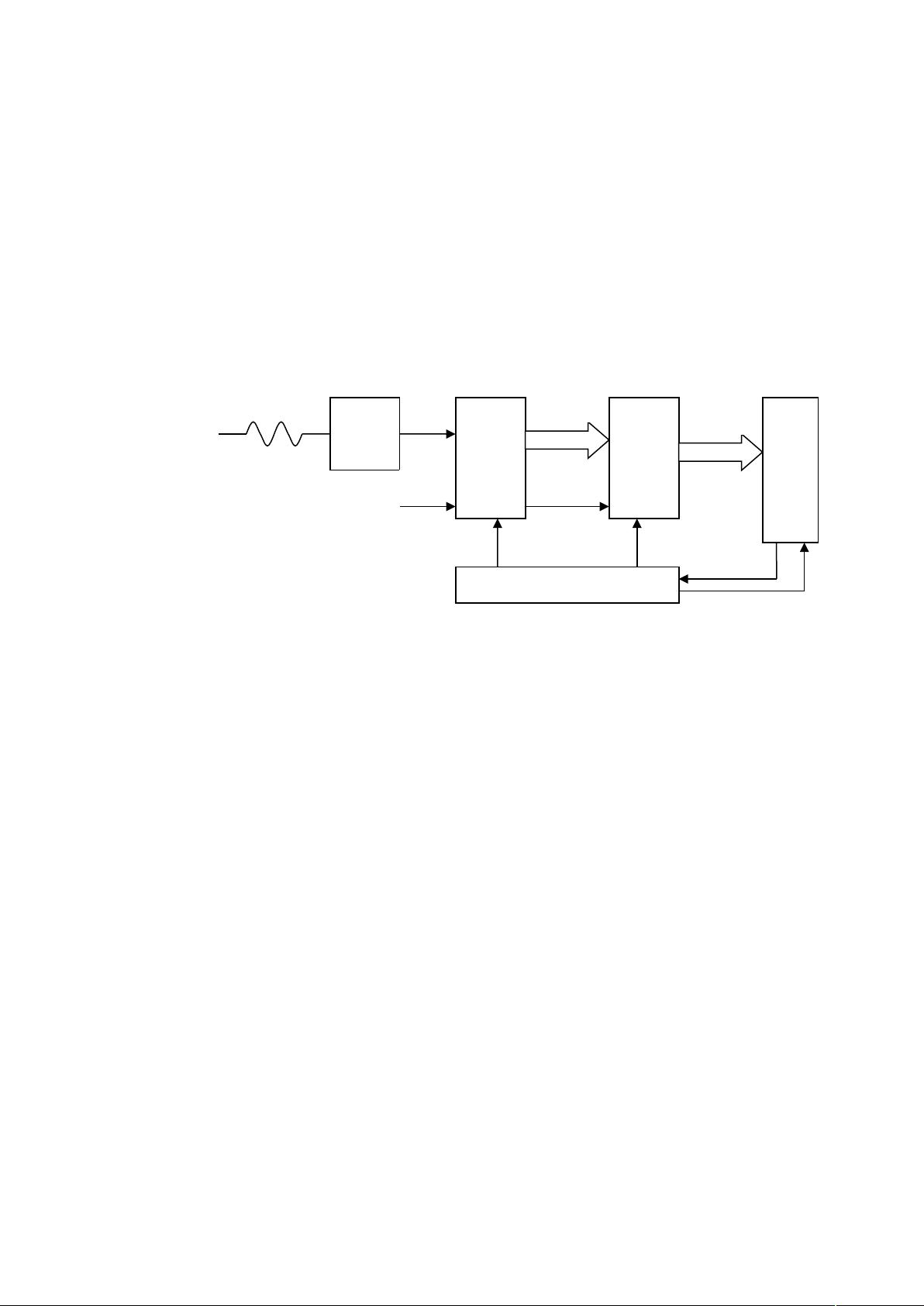

在设计过程中,作者采用了自顶向下的方法,将FPGA作为核心逻辑控制模块,将其功能划分为多个子模块。通过VHDL(Very High Speed Integrated Circuit Hardware Description Language)语言在Max+PlusII开发环境中进行设计和仿真,确保每个模块的功能完善和控制流程的正确性。具体来说,设计中可能包括采样控制模块、通道选择模块以及A/D转换控制模块等,这些模块协同工作以实现对不同频率模拟信号的精确采样。

在FPGA的单片系统研究中,为了适应数据采集和处理的需求,首先需要对FPGA进行选型,然后设计出基于FPGA的单片系统架构。其中,变频率多通道采样控制模块是一个关键部分,它利用ADS8364这种高性能的模数转换器,可以对多达6路的变频率模拟信号进行周期性采样。通道选择控制模块负责选择要采样的信号通道,而A/D转换控制模块则确保转换过程的同步和准确。

通过仿真验证,该设计能够完成基于FPGA的变频率采样时序控制,实现了对不同频率信号的实时、高效采集,提高了数据采集系统的灵活性和适应性。关键词如“FPGA”、“变频”、“数据采集”和“数模转换”揭示了论文的核心研究内容和技术焦点。

这篇本科毕业论文深入探讨了如何利用FPGA设计一个能适应不同频率信号的时序控制器,对于理解和实现变频率数据采集系统具有一定的理论指导和实践意义。

110 浏览量

点击了解资源详情

点击了解资源详情

163 浏览量

124 浏览量

305 浏览量

2020-10-21 上传

557 浏览量

2021-10-31 上传

hellohei_911

- 粉丝: 0

最新资源

- Openaea:Unity下开源fanmad-aea游戏开发

- Eclipse中实用的Maven3插件指南

- 批量查询软件发布:轻松掌握搜索引擎下拉关键词

- 《C#技术内幕》源代码解析与学习指南

- Carmon广义切比雪夫滤波器综合与耦合矩阵分析

- C++在MFC框架下实时采集Kinect深度及彩色图像

- 代码研究员的Markdown阅读笔记解析

- 基于TCP/UDP的数据采集与端口监听系统

- 探索CDirDialog:高效的文件路径选择对话框

- PIC24单片机开发全攻略:原理与编程指南

- 实现文字焦点切换特效与滤镜滚动效果的JavaScript代码

- Flask API入门教程:快速设置与运行

- Matlab实现的说话人识别和确认系统

- 全面操作OpenFlight格式的API安装指南

- 基于C++的书店管理系统课程设计与源码解析

- Apache Tomcat 7.0.42版本压缩包发布