FPGA与VHDL实现PCM码解调模块设计

191 浏览量

更新于2024-08-31

1

收藏 227KB PDF 举报

"EDA/PLD中的VHDL实现PCM码解调程序模块设计"

本文主要探讨了如何利用VHDL语言在EDA/PLD(电子设计自动化/可编程逻辑器件)平台上实现PCM码的解调程序模块设计,特别是在FPGA(现场可编程门阵列)中进行应用。PCM码,即脉冲编码调制,是一种广泛用于数字通信的模拟信号数字化方法,它通过将连续的输入信号转化为离散的时间和振幅值,然后转换为数字代码进行传输,以提高通信系统的效率、稳定性和安全性。

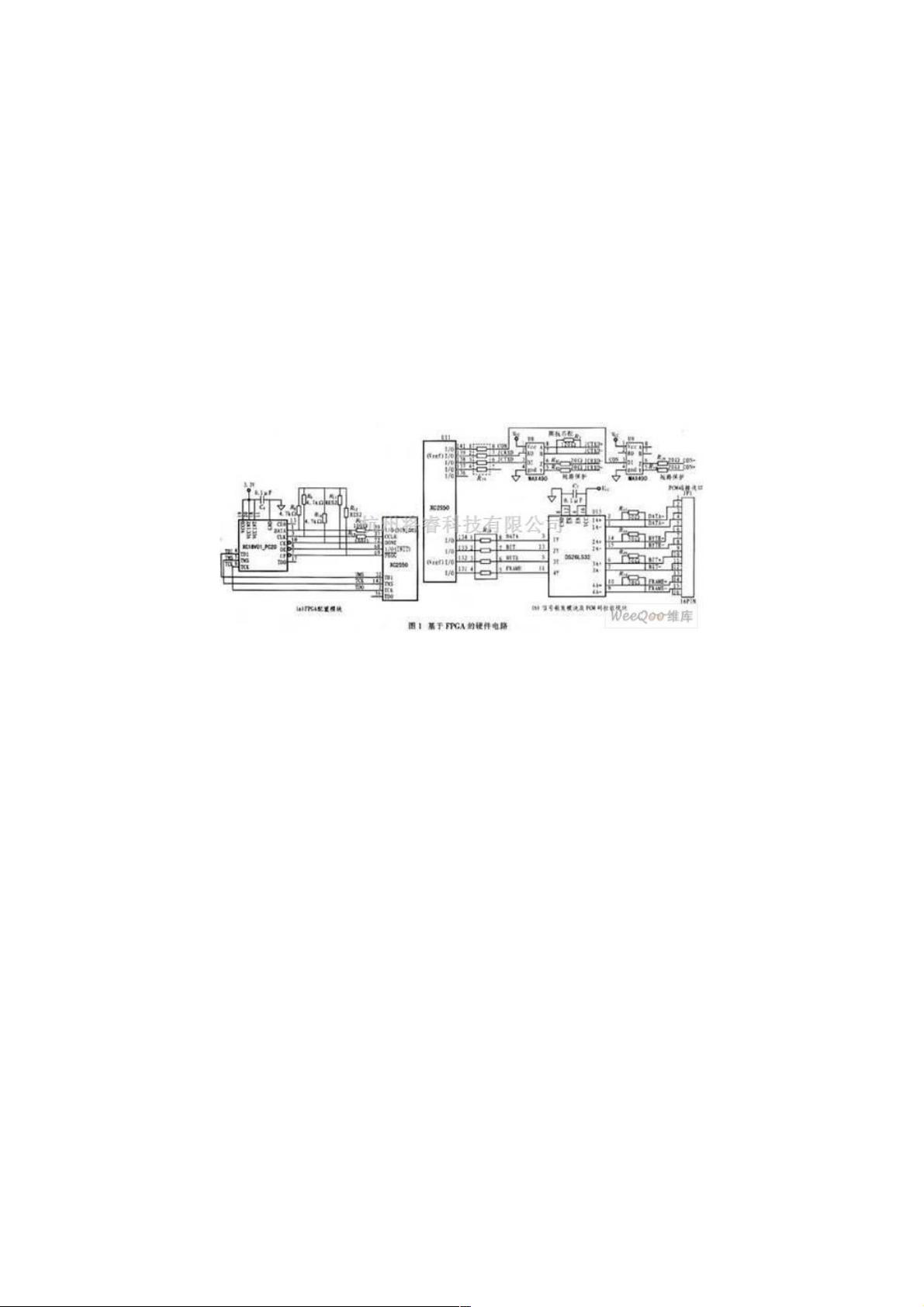

在硬件电路设计部分,文章提到了一个基于FPGA的系统架构。该架构包括两个主要模块:FPGA配置模块和信号收发模块及PCM码接收模块。FPGA配置模块负责设置器件的工作状态,而信号收发模块则处理数据的发送与接收。特别地,PCM码接收模块在移位脉冲的同步下接收串行数据,并将其转化为并行数据存储在FIFO(先进先出缓冲区)中,以便后续处理。

在硬件实现中,选择了Xilinx公司的Spartan系列XC2S50 FPGA器件。这种器件支持多种工作模式,如主串模式、从串模式、边界扫描和从并模式。在本设计中,通过接地M0、M1和M2引脚使其工作在主串模式。FPGA的配置数据存储在片内RAM中,可以通过上电时从EPROM加载,完成配置后进入工作状态。由于FPGA的特性,即使断电后其内部逻辑也会复位,但可以通过更换EPROM轻松重新编程,以适应不同的功能需求。

VHDL作为一种硬件描述语言,被用于编写这些模块的逻辑控制,它允许设计者以结构化的方式描述硬件行为,同时具有较强的抽象能力和可重用性。在PCM解调过程中,VHDL代码实现的关键在于正确处理数据的同步、采样和解码,确保在不同传输速率和帧结构下都能正确解调PCM码。

总结来说,本文详细阐述了使用VHDL在EDA/PLD环境下设计PCM码解调模块的过程,以及在FPGA硬件平台上的实现策略。这种方法的优势在于灵活性和可重构性,能够在不更改硬件的情况下适应不同的通信参数,对于现代数字通信系统的设计具有重要的实践价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-07 上传

2020-11-03 上传

2020-11-08 上传

2020-12-09 上传

2020-11-12 上传

2020-11-16 上传

weixin_38665822

- 粉丝: 9

- 资源: 933

最新资源

- samba服务器配置

- proteus 与 keil 整合构建单片机虚拟实验室

- 下载下载下载下载下载下载下载下载下载下载

- H.264.And.MPEG-4.Video.Compression.Video.Coding.For.Next.Generation.Multimedia

- linux -c编程

- 自动化专业英语附翻译

- c语言嵌入式系统编程修炼之道

- Oracle中常用函数

- 知名编辑器Vim使用手册(中译本)

- 计算机网络第三版习题答案

- GCC使用介绍,获得以及使用

- 数据库系统概论(第四版)答案

- C++编程思想 中文第二版

- 单片机应用技术.ppt

- PT2262/PT2272资料

- 全国计算机技术与软件专业技术资格(水平)考试2007年下半年 数据库系统工程师 下午试卷