FPGA实现的多功能抢答器系统设计

需积分: 12 197 浏览量

更新于2024-06-30

收藏 18.44MB DOC 举报

"基于FPGA的多组抢答器设计,旨在解决现有抢答器系统的稳定性、开发周期、功能单一和公平性等问题。通过FPGA技术,实现有线抢答组数切换、无线抢答以及系统在闲时的复用功能,提升了抢答器的扩展性和公平性。该设计由重庆邮电大学光电工程学院/重庆国际半导体学院的黄代放同学完成,指导教师为吴良英讲师。论文涵盖了对当前抢答器系统缺陷的分析,FPGA技术在抢答器系统中的应用及其优势,并提出了一个具有竞争力的系统设计方案。"

正文:

基于FPGA的多组抢答器设计是一项创新性的毕业设计项目,主要针对现有的数字电路和单片机实现的抢答器存在的问题进行改进。这些问题包括系统的不稳定、较长的开发周期、功能单一以及抢答公平性不足等。随着FPGA技术的发展,它在电子系统设计中的优势逐渐显现,特别是在抢答器系统搭建中,可以提供更复杂、更灵活的架构。

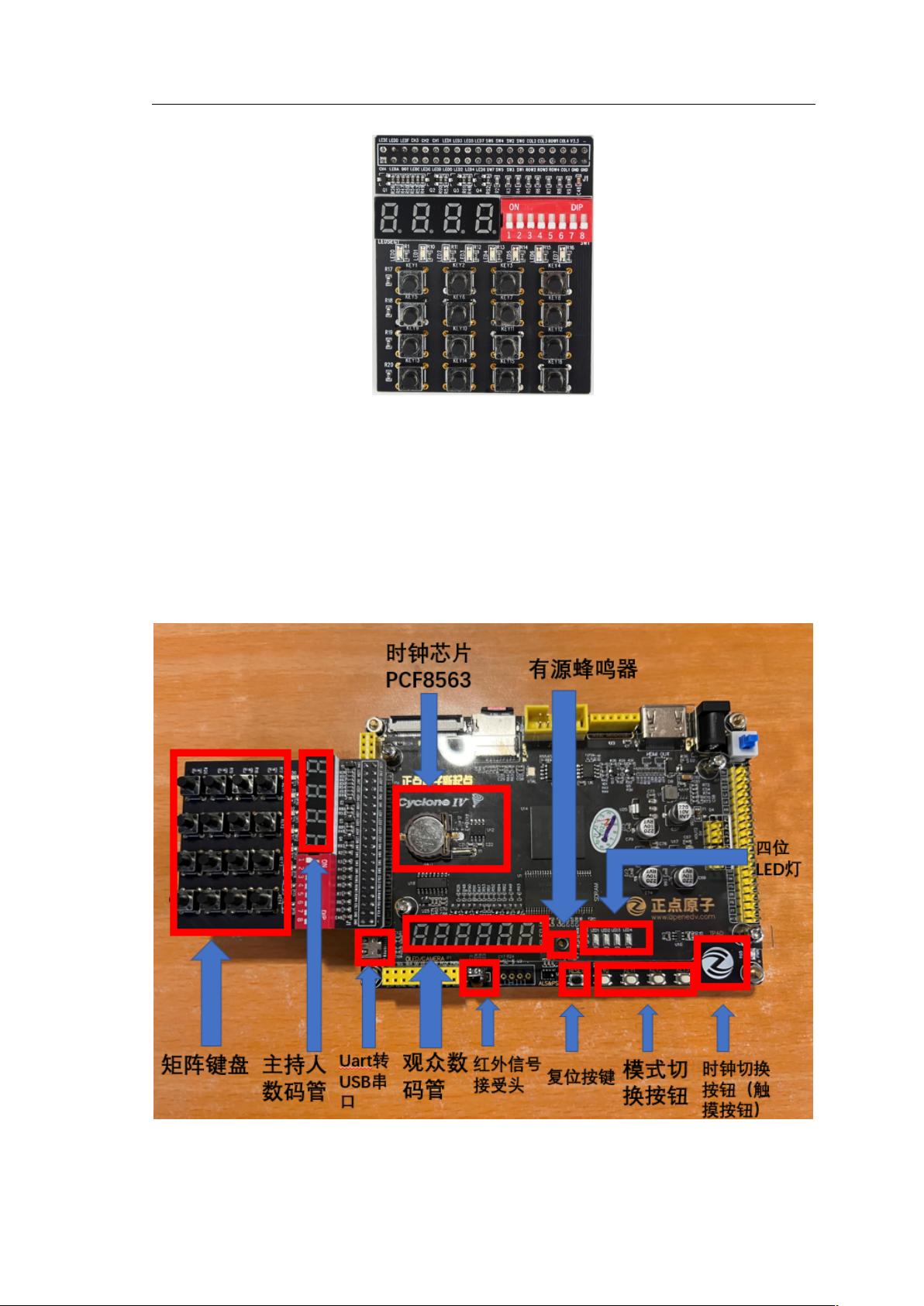

FPGA,全称为Field-Programmable Gate Array,是一种可编程逻辑器件,能够根据设计者的需要进行定制化配置,实现各种复杂的数字逻辑功能。在本设计中,FPGA被用来构建一个多组抢答器,不仅支持有线抢答组数的切换,还引入了无线抢答功能,以适应不同场合的需求。同时,系统在没有抢答活动时可以进行复用,提高了设备的利用率。

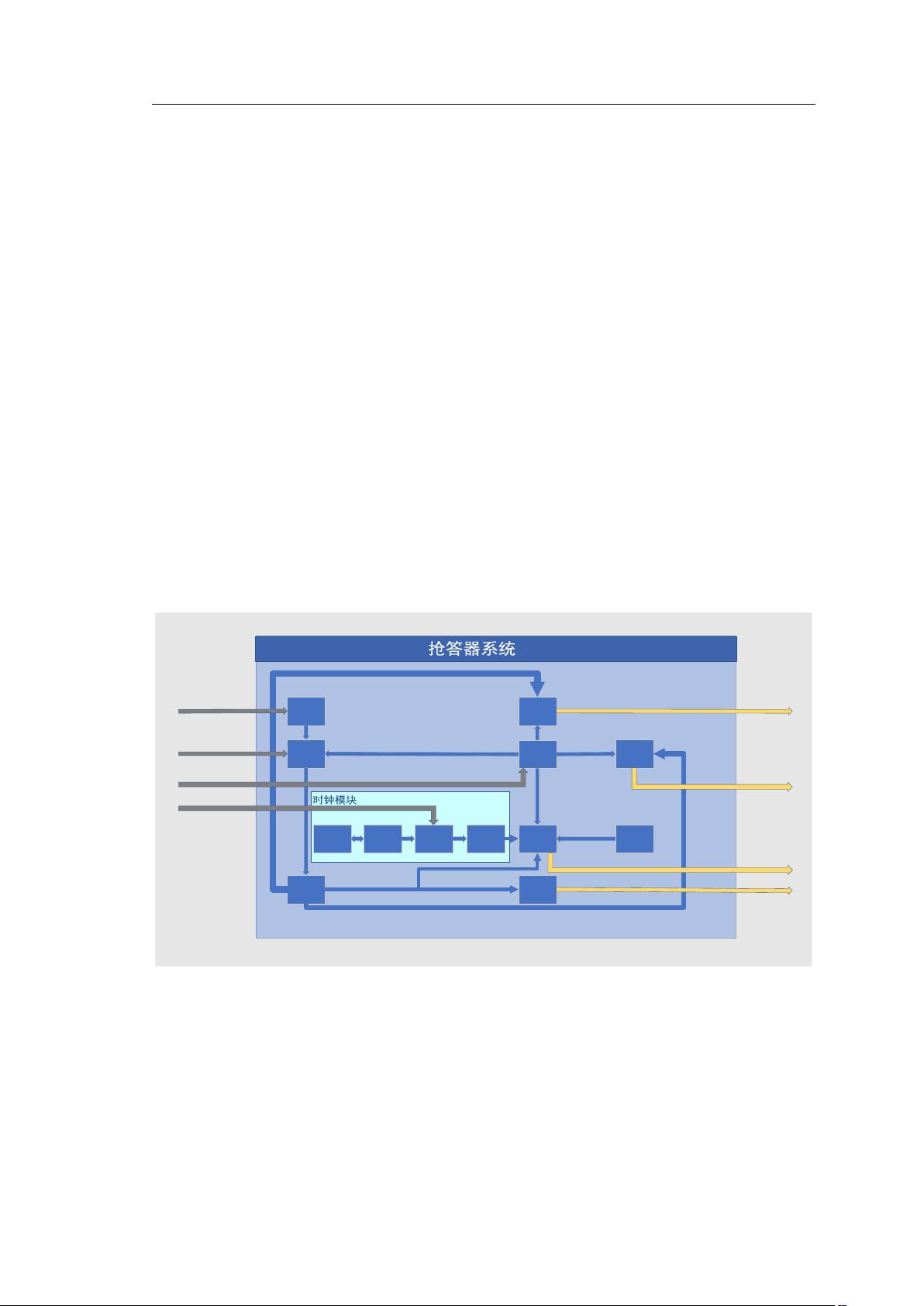

设计的关键在于构建一个稳定且高效的系统架构,确保在多个参赛组同时抢答时,能准确、快速地判断出最先按下按钮的组别,从而保证比赛的公平性。此外,系统的设计还需要考虑扩展性,以便在未来添加更多功能或增加抢答组数时,能够轻松地进行硬件和软件的升级。

论文中详细阐述了抢答器系统的运行流程,从信号的输入、处理到结果的判定,每个环节都经过精心设计和优化。同时,系统功能设计上,除了基础的抢答判断外,还可能包括了防作弊机制、计分系统、显示界面以及无线通信模块等,以提升抢答器的整体性能。

在实施过程中,作者黄代放遵循了学术诚信的原则,独立完成了研究工作,并对所有引用的内容进行了明确标注。此外,他还授权重庆邮电大学使用其学位论文,表明了对知识成果公开和分享的认同。

基于FPGA的多组抢答器设计是一次成功的尝试,它充分利用了FPGA的灵活性和并行处理能力,解决了传统抢答器的诸多问题,为知识竞赛活动提供了更加先进、公平的解决方案。这一设计不仅体现了作者扎实的专业技能,也展示了FPGA技术在电子设计领域的广阔应用前景。

1352 浏览量

112 浏览量

245 浏览量

2021-07-13 上传

1124 浏览量

124 浏览量

幻命

- 粉丝: 3

- 资源: 1

最新资源

- 免除登录繁琐步骤,QQ登录器

- responsiveapp

- Boundless-Marble

- 电子功用-多功能通用电锁

- 保险公司新干部培训班课后作业

- Curso_JavaScrip_Rocketseat-:JavaScript的模数模

- 泉中流版base64编码和解码(支持汉字等编码(utf-8))

- wget在线扒站.zip

- personal-website:我的个人网站上列出了项目等

- Reservia:Reservia是一个预订网站

- JerryQuu:使用Typescript编写的Node.js的快速,可靠的基于Redis的电子邮件队列

- d-pyro.github.io:PS4 6.72漏洞利用

- gulp-framer-skeleton:一个基于 FramerJS 的基于 gulp 的骨架项目

- 2016年“ 蓝桥 杯” 第 七 届 全国 软件和信息技术专业人才 大赛 个人赛——温湿度监控设备·代码.zip

- Story:学习git

- 保险公司新人成功销售训练培训班操作标准