Vivado Design Suite UltraFast 设计方法指南

需积分: 9 24 浏览量

更新于2024-07-17

收藏 11.27MB PDF 举报

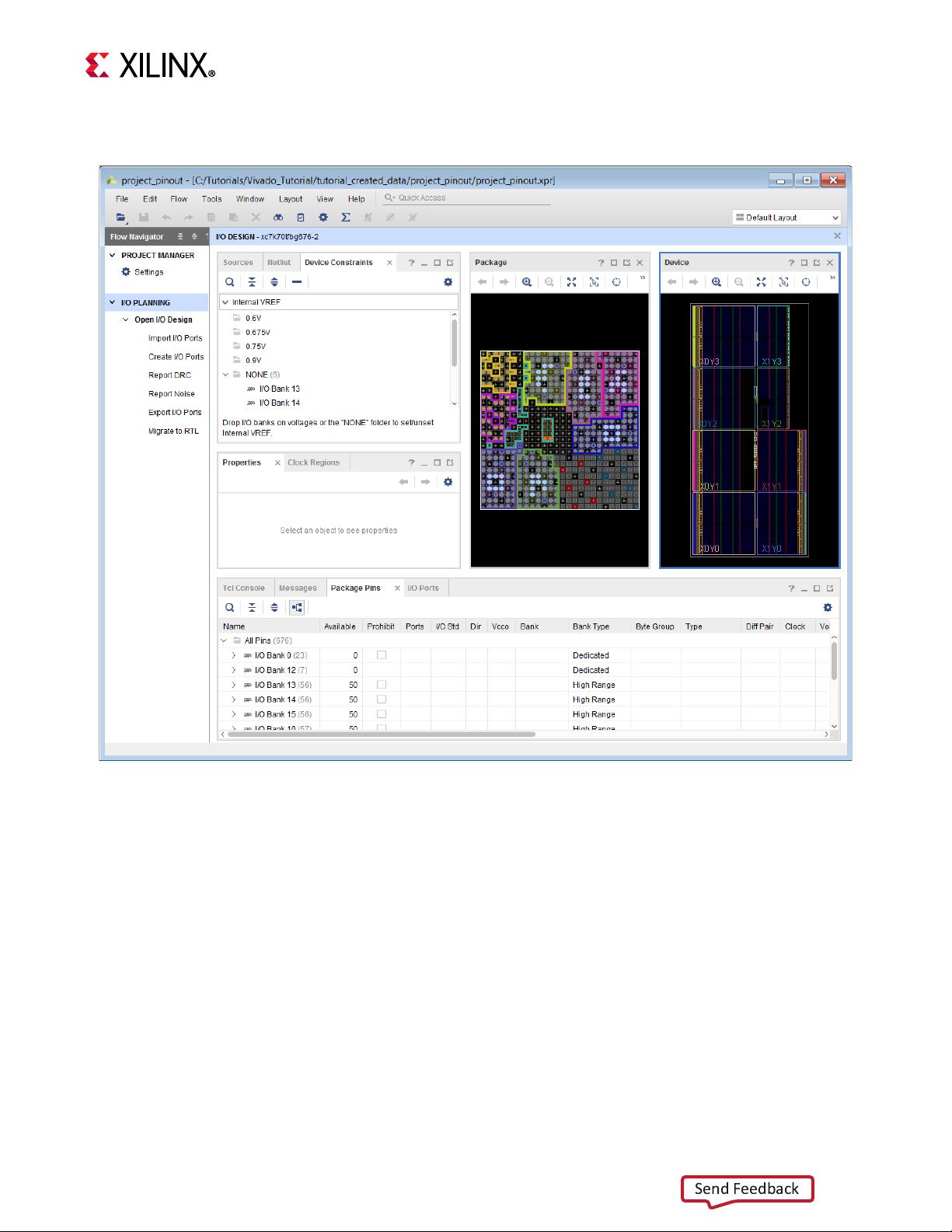

"UltraFast Design Methodology Guide for the Vivado Design Suite是Xilinx公司发布的一份关于使用Vivado Design Suite进行FPGA设计的优化指南,主要针对2018.1版本。该文档提供了FPGA设计的快速方法,旨在帮助用户提高设计效率和性能。"

这份文档的重要性和价值在于它提供了详细的FPGA设计流程和最佳实践,覆盖了从初期设计到最终实现的各个阶段。以下是一些关键知识点:

1. **修订历史**:文档在2018年5月11日更新至2018.1版本,进行了菜单命令的更新、新增和改进,确保了与软件最新功能的同步。

2. **时钟缓冲器(Clock Buffers)**:文档提到了“Cascaded Clock Buffers”并强调了设置DONT_TOUCH属性的重要性,这有助于避免不必要的时钟树调整,从而提高设计的时序收敛。

3. **时钟域跨越(Clock Domain Crossing, CDC)**:文档更新了关于处理CDC违规豁免的技巧,这对于在不同时钟域之间正确传递数据至关重要,防止数据丢失或错误。

4. **设计规则检查(Design Rule Checks, DRCs)审查与清理**:添加了关于DRC违规豁免的提示,帮助设计师解决设计中的合规性问题,以确保设计符合硬件要求。

5. **报告方法论运行**:强调了关于RAM Band和DSP primitive可选流水线的注意事项,以及如何处理方法论检查违规的豁免,这些都是优化设计性能的关键因素。

6. **布线运行时间(Route Runtime)**:新增了一个专门的章节,讨论如何优化布线过程,减少设计时间和提高布线效率。

7. **设计收敛概述**:加入了关于电源优化的信息,电源管理是现代FPGA设计中不可或缺的部分,可以显著影响设计的功耗和性能。

8. **优化常规布线路径**:介绍了LUT_REMAP、SRL_STAGES_TO_REG_INPUT和CONTROL_SET_REMAP等属性,这些属性可以帮助调整逻辑资源,提升布线速度和性能。

9. **应用常见时序收敛技术**:不再推荐减少MUXF映射的方法,可能是因为新的工具和优化策略已经提供了更好的解决方案。

10. **使用块级综合策略改善网表**:添加了这一部分,说明如何通过高级综合策略改进设计的层次结构,进一步提高设计的效率和性能。

"UltraFast Design Methodology Guide for the Vivado Design Suite" 是一个宝贵的资源,为FPGA开发者提供了一套详尽的指导,帮助他们利用Vivado Design Suite实现高效、高性能的设计。

498 浏览量

363 浏览量

2022-02-21 上传

2022-03-25 上传

696 浏览量

249 浏览量

344 浏览量

229 浏览量

long游天下

- 粉丝: 31

- 资源: 31

最新资源

- android_hybird:android_hibird 框架

- ABOV芯片 项目01 代码.zip

- 【深层神经网络实战代码】识别猫 吴恩达深度学习笔记

- teste-indt-master.zip

- 互联网大厂C++复习经验

- maolan:毛兰DAW的GUI

- CS-518:CS 518课程的作业

- 安全摄像头原理图及PCB

- ArduinoRequestResponse:Arduino固件与ORSSerialPort RequestResponseDemo示例应用程序一起使用

- VC操作MD5.rar

- buildz-api

- portal-web-ecoleta:下一级别的活动周日,Rocketseat实用工具TypeScript,NodeJS,ReactJS和React Native。 紧急情况下的集体诉讼,请在以下情况下填写您的姓名:(必要的)取消必要的附加条件

- wiki:一个简洁的个人 wiki,使用 vue.js 和 markdown-js

- aura:气候仪表板

- 最简单的SysTick延时程序

- 安全摄像头程序源码(好用)