AMBA AXI4协议详解:高性能系统设计的关键

需积分: 1 186 浏览量

更新于2024-06-26

收藏 908KB PDF 举报

"本文是对AMBA AXI4协议的总结,涵盖了AXI协议的优势、特点以及各个通道的功能和信号交互机制。"

AXI4协议是Advanced Microcontroller Bus Architecture (AMBA)体系结构中的高级扩展接口,设计用于构建高性能、高频率的系统。它的主要优点在于支持高带宽、低延迟的操作,无需复杂的桥接设备即可实现高频工作。AXI协议能够适应各种组件接口的需求,特别适合高初始访问延迟的内存控制器,并且提供了灵活的互连架构实现方式。此外,AXI协议还向下兼容AHB(Advanced High-performance Bus)和APB(Advanced Peripheral Bus)接口,使得不同层次的组件能无缝连接。

AXI协议的特点包括分离的地址/控制和数据阶段,这使得传输过程更为高效;通过字节选通信号支持非对齐数据传输,增加了设计的灵活性;使用突发传输,只需传输起始地址,减少了传输开销;允许地址信息先于数据传输,优化了数据流;分离的读写数据通道降低了DMA(Direct Memory Access)操作的损耗;支持多未完成地址,允许乱序传输完成,提高了系统的并行处理能力;并可通过添加简单的寄存器阶段来帮助时序收敛。

AXI协议包含低功耗操作的信号扩展,同时提供了一个子集——AXI4-Lite协议,该协议简化了控制寄存器接口,适用于那些不需要全功能AXI接口的简单组件。

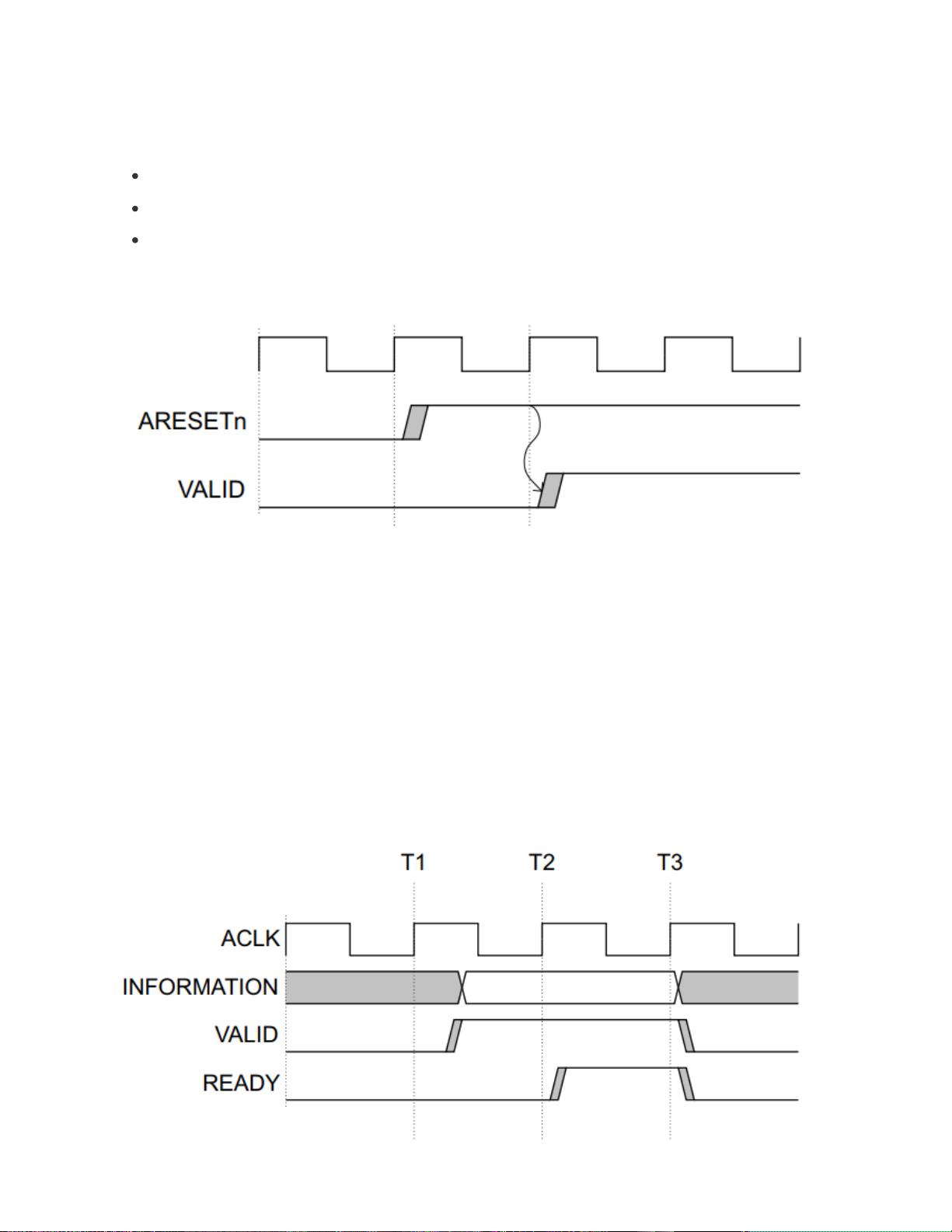

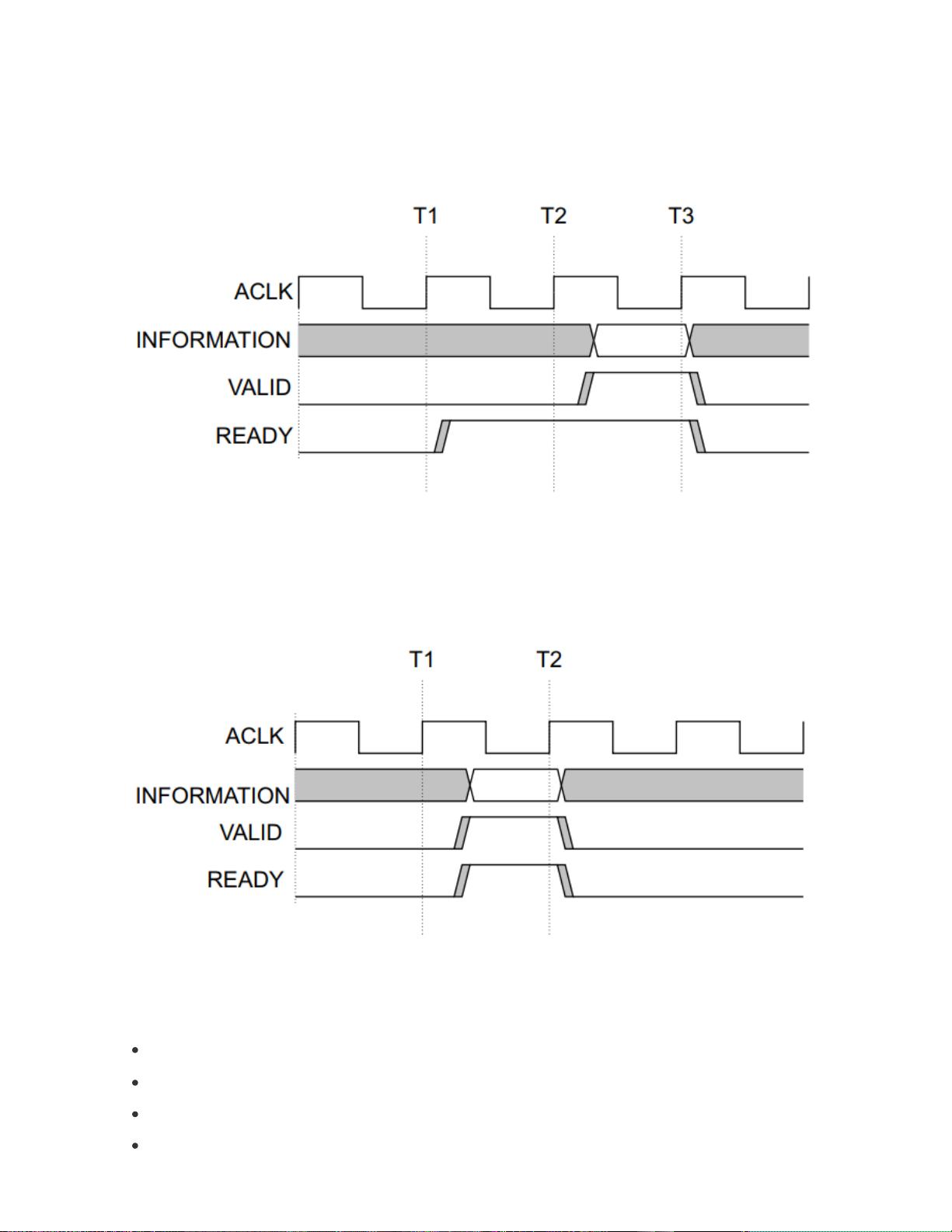

AXI协议基于突发传输,定义了四个独立的事务通道:读地址、读数据、写地址和写数据,以及一个写响应通道。这些通道各自具有VALID和READY信号,用于主设备和从设备之间的数据传输握手。VALID表明数据或控制信息已准备就绪,而READY表示接收方可以接受信息。对于读数据和写数据通道,还有LAST信号,它标记当前传输是否为事务中的最后一个。

读地址和写地址通道负责传输事务相关的地址和控制信息。读数据通道则包括数据总线和读响应信号,用于从设备向主设备传输数据和确认读事务的状态。写数据通道则由数据总线和无返回信息组成,主设备通过这个通道将数据传递给从设备。数据总线的宽度可以根据需求进行配置,范围从8到1024位不等。

总结来说,AXI4协议通过其精心设计的通道和信号机制,为构建高效、灵活和高性能的嵌入式系统提供了强大的基础,确保了不同组件之间的高效通信。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-12-18 上传

2020-07-25 上传

2021-09-30 上传

2022-01-03 上传

113 浏览量

2019-07-31 上传

阿东的芯片之路

- 粉丝: 0

- 资源: 3

最新资源

- Java毕业设计项目:校园二手交易网站开发指南

- Blaseball Plus插件开发与构建教程

- Deno Express:模仿Node.js Express的Deno Web服务器解决方案

- coc-snippets: 强化coc.nvim代码片段体验

- Java面向对象编程语言特性解析与学生信息管理系统开发

- 掌握Java实现硬盘链接技术:LinkDisks深度解析

- 基于Springboot和Vue的Java网盘系统开发

- jMonkeyEngine3 SDK:Netbeans集成的3D应用开发利器

- Python家庭作业指南与实践技巧

- Java企业级Web项目实践指南

- Eureka注册中心与Go客户端使用指南

- TsinghuaNet客户端:跨平台校园网联网解决方案

- 掌握lazycsv:C++中高效解析CSV文件的单头库

- FSDAF遥感影像时空融合python实现教程

- Envato Markets分析工具扩展:监控销售与评论

- Kotlin实现NumPy绑定:提升数组数据处理性能