Verilog实现的简易RISC_CPU设计

需积分: 9 13 浏览量

更新于2024-07-30

收藏 315KB PDF 举报

"该资源是一个关于简单CPU设计的项目,主要使用Verilog硬件描述语言实现。设计目标是一个基于RISC架构的八位微处理器,能够执行基本的算术和逻辑运算,如两个无符号八位二进制数的原码相乘。设计包括微处理器的硬件系统和指令系统,关注点在于技术指标的实现,而非实际应用的合理性或效率。"

在设计一个简单的CPU时,关键组成部分包括:

1. 运算器(ALU):负责执行基本的算术(加、减、乘、除)和逻辑运算(与、或、非、异或等),通常在时钟上升沿触发操作。

2. 控制器(CON):根据指令寄存器中的操作码生成控制信号,协调整个系统的操作。

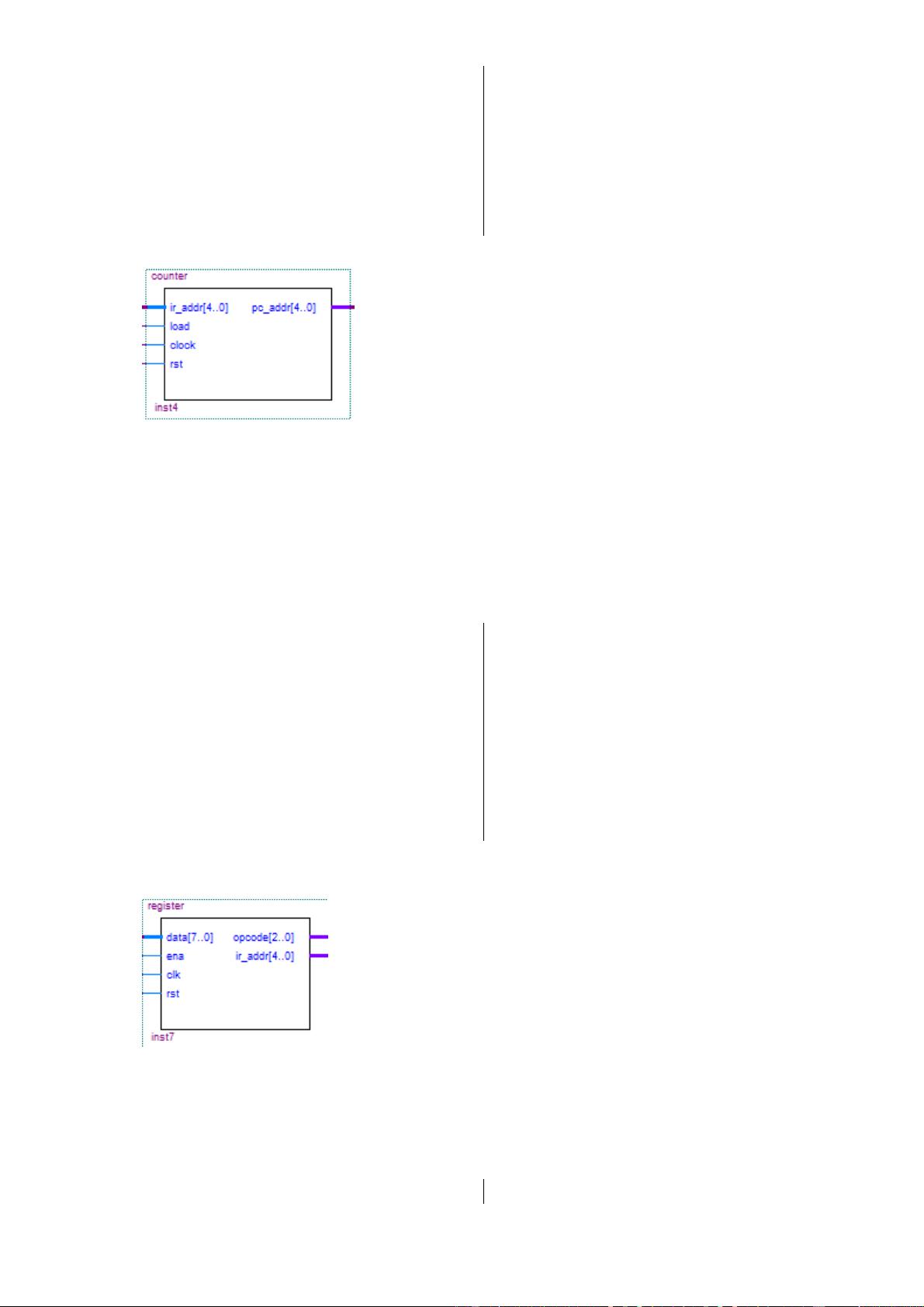

3. 指令寄存器(IR):存储当前正在执行的指令的完整信息,包括操作码和操作数地址。

4. 程序计数器(PC):存储下一条要执行指令的地址,通常在每个时钟周期增加以按顺序执行指令。

5. 累加器(ACC):临时存储运算结果。

6. 地址选择器和数据选择器:用于选择和传输数据到正确的目的地,如内存或I/O设备。

7. 时钟发生器(CLK_GEN):产生系统所需的多个时钟信号。

8. 内存(ROM和RAM):ROM存储固定程序,RAM用于存储临时数据和运算中间结果。

9. 输入/输出特殊寄存器:用于数据的输入和输出,与外部设备通过总线进行通信。

处理器的指令系统通常包括各种指令类型,如数据传送指令、算术运算指令、逻辑运算指令、控制转移指令等。在这个简单的CPU设计中,所有指令字长被设定为固定长度,简化了设计复杂性。这种RISC(精简指令集计算机)架构的CPU设计,强调指令集的精简,以提高执行效率。

在Verilog中实现CPU涉及模块化设计,每个部件作为一个独立的Verilog模块编写,然后在顶层模块中将它们集成在一起,形成完整的CPU结构。这种方式允许对每个模块进行独立的测试和验证,提高了设计的可读性和可维护性。

设计完成后,需要通过仿真工具对设计进行验证,确保其在不同情况下的正确性。这通常包括编写测试平台(Testbench),模拟各种输入序列并检查CPU的输出是否符合预期。如果验证成功,设计可以进一步被综合成门级网表,用于FPGA或ASIC的实现。

这个CPU设计虽然在功能上相对基础,但它是理解计算机体系结构和硬件设计过程的一个重要起点。通过这样的实践,可以深入学习数字逻辑、计算机组织和Verilog语言,为更复杂系统的设计打下基础。

102 浏览量

576 浏览量

2053 浏览量

586 浏览量

150 浏览量

2024-06-28 上传

563 浏览量

2022-09-24 上传

102 浏览量

xy867497088

- 粉丝: 5

最新资源

- 久度免费文件代存系统 v1.0:全技术领域源码分享

- 深入解析caseyjpaul.github.io的HTML结构

- HTML5视频播放器的实现与应用

- SSD7练习9完整答案解析

- 迅捷PDF完美转PPT技术:深度识别PDF内容

- 批量截取子网页工具:Python源码分享与使用指南

- Kotlin4You: 探索设计模式与架构概念

- 古典风格茶园茶叶酿制企业网站模板

- 多功能轻量级jquery tab选项卡插件使用教程

- 实现快速增量更新的jar包解决方案

- RabbitMQ消息队列安装及应用实战教程

- 简化操作:一键脚本调用截图工具使用指南

- XSJ流量积算仪控制与数显功能介绍

- Android平台下的AES加密与解密技术应用研究

- Место-响应式单页网站的项目实践

- Android完整聊天客户端演示与实践