国内首个RISC-V处理器:蜂鸟E200开源与SoC原型详解

需积分: 50 49 浏览量

更新于2024-07-18

收藏 5.33MB PDF 举报

蜂鸟E200是一款基于RISC-V指令集架构的处理器芯片内核和SoC原型,它在国内首次实现了RISC-V技术的应用,具有开源和灵活性的优势。本文档详细介绍了蜂鸟E200系列的开发过程、设计特点和使用方法。

1. **RISC-V指令集架构**:RISC-V是一种开放源码的指令集架构,强调可扩展性和可定制性,适用于多种应用场景,如嵌入式系统和高性能计算。蜂鸟E200的采用表明了中国在这个领域的发展和对开源技术的支持。

2. **代码层次结构与测试**:

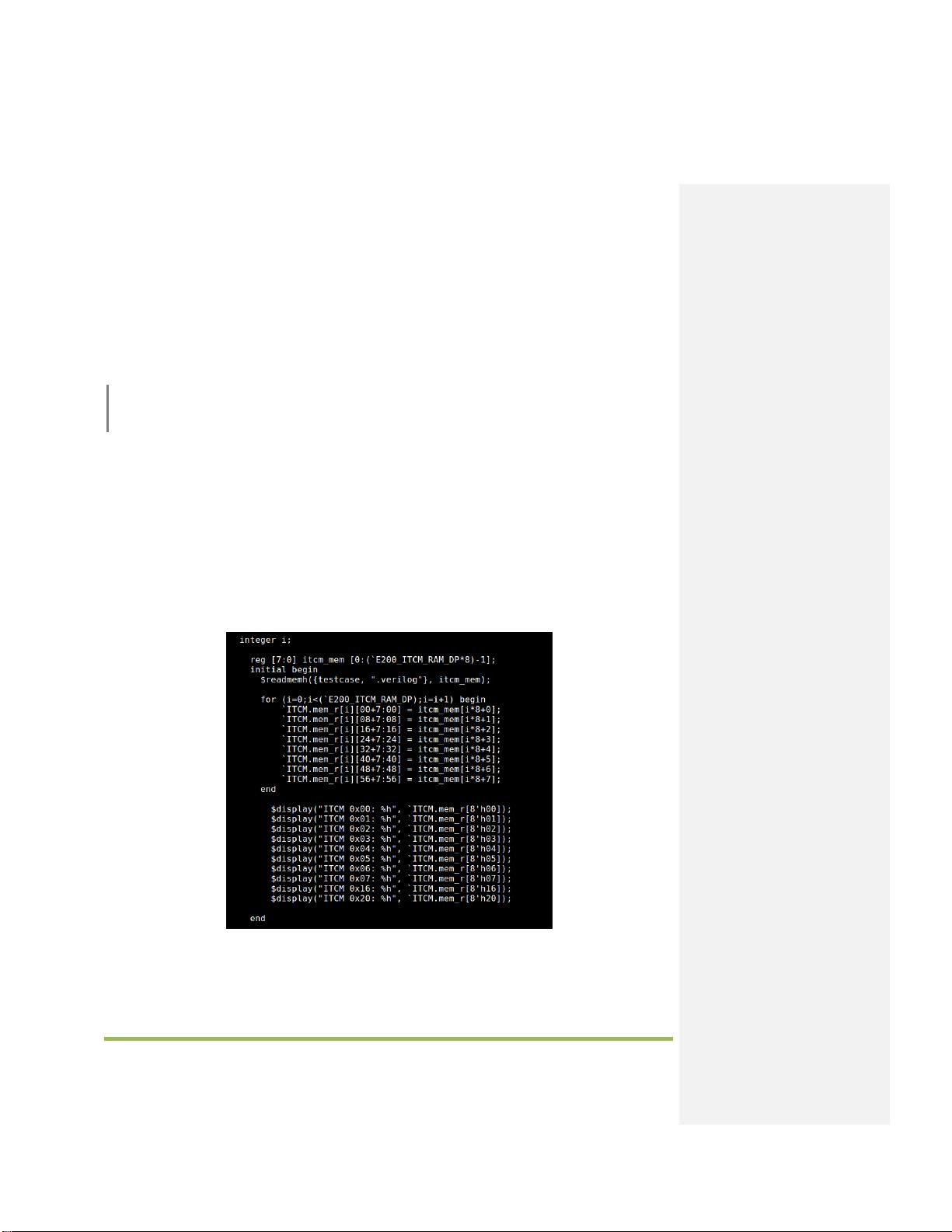

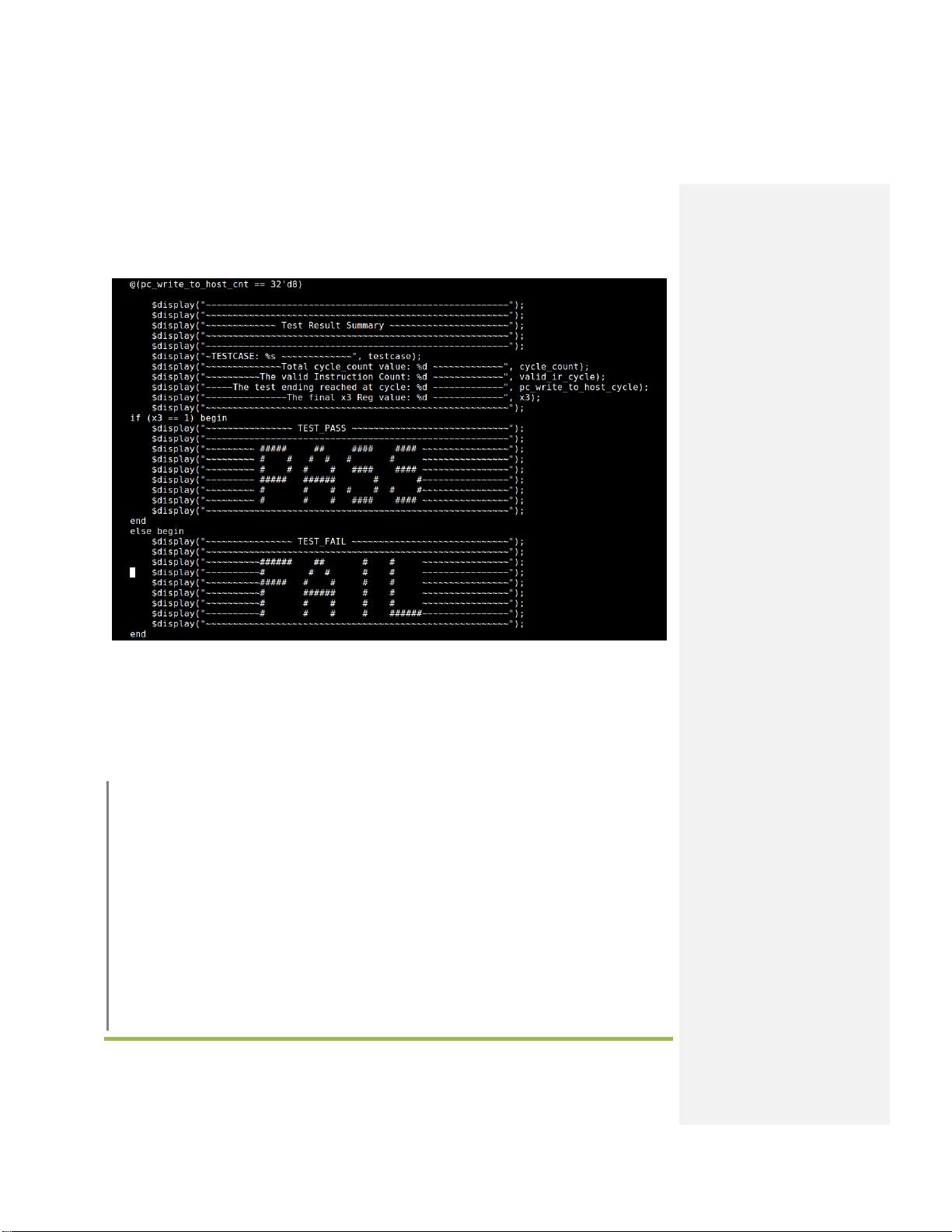

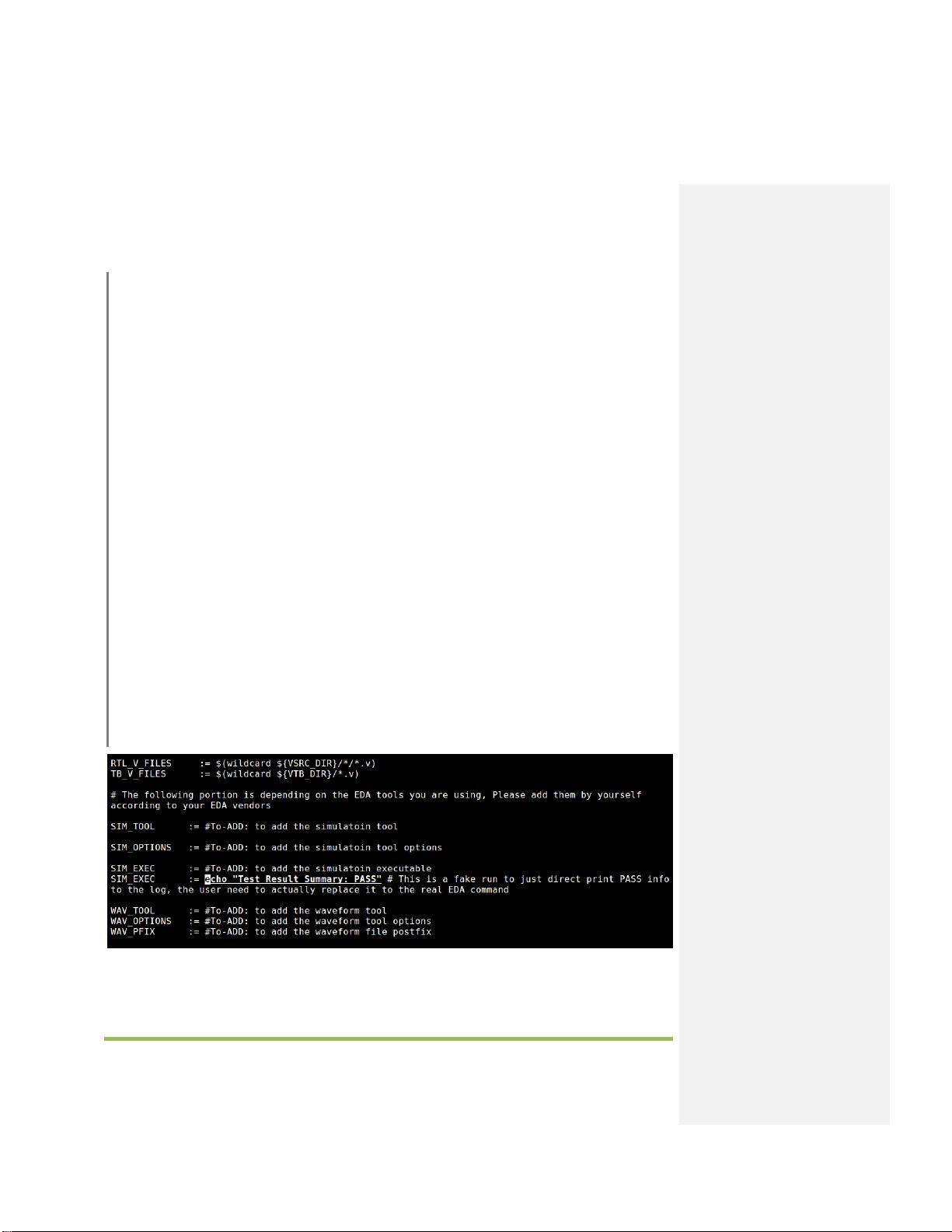

- E200项目的代码层次结构清晰,包括Verilog仿真测试,涉及自测试用例(如riscv-tests和ISA自测试),以及详细的测试平台设置,如TESTBENCH。

- 自我检查测试用例确保了核心功能的正确性,而Verilog测试bench则提供了实际硬件环境下的验证。

3. **SoC平台实现**:

- SIRV-E200-SOC是蜂鸟E200的SoC版本,由FREEDOME310 SOC介绍起,包括其组成结构(如CPU、内存、外设接口等)、代码组织结构以及自定义总线的设计。

- FPGA原型平台构建了FPGA开发板,指导用户如何烧录FPGA,利用JTAG调试器进行调试,并提供DIY总结。

4. **软件开发和调试**:

- 用户可以利用FREEDOM-E-SDK和SIRV-E-SDK进行软件开发,文档提供了这些SDK的简介、代码结构以及如何使用它们运行和调试示例程序,包括GDB和OPENOCD等调试工具的使用。

5. **性能评估**:

- 文档还介绍了如何在蜂鸟E200上运行BENCHMARKS,如DHRYSTONE Benchmark和CoreMark Benchmark,以评估处理器的性能和效率。

6. **持续改进和更新**:

- Revision History记录了项目自2017年以来的迭代过程,展示了开发团队的持续优化和改进。

蜂鸟E200的开发文档是一份详尽的技术指南,涵盖了从RISC-V指令集架构理解、硬件设计、代码组织到软件开发和性能评估的全过程,为开发者和研究者提供了丰富的参考资源。

2009-04-27 上传

2012-05-27 上传

2022-09-24 上传

2019-09-12 上传

2022-06-14 上传

2007-06-27 上传

2021-11-17 上传

2013-03-21 上传

fuli_fox

- 粉丝: 17

- 资源: 24

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查