"TI FPD-Link解串器DS90C124-Q1产品手册详解"

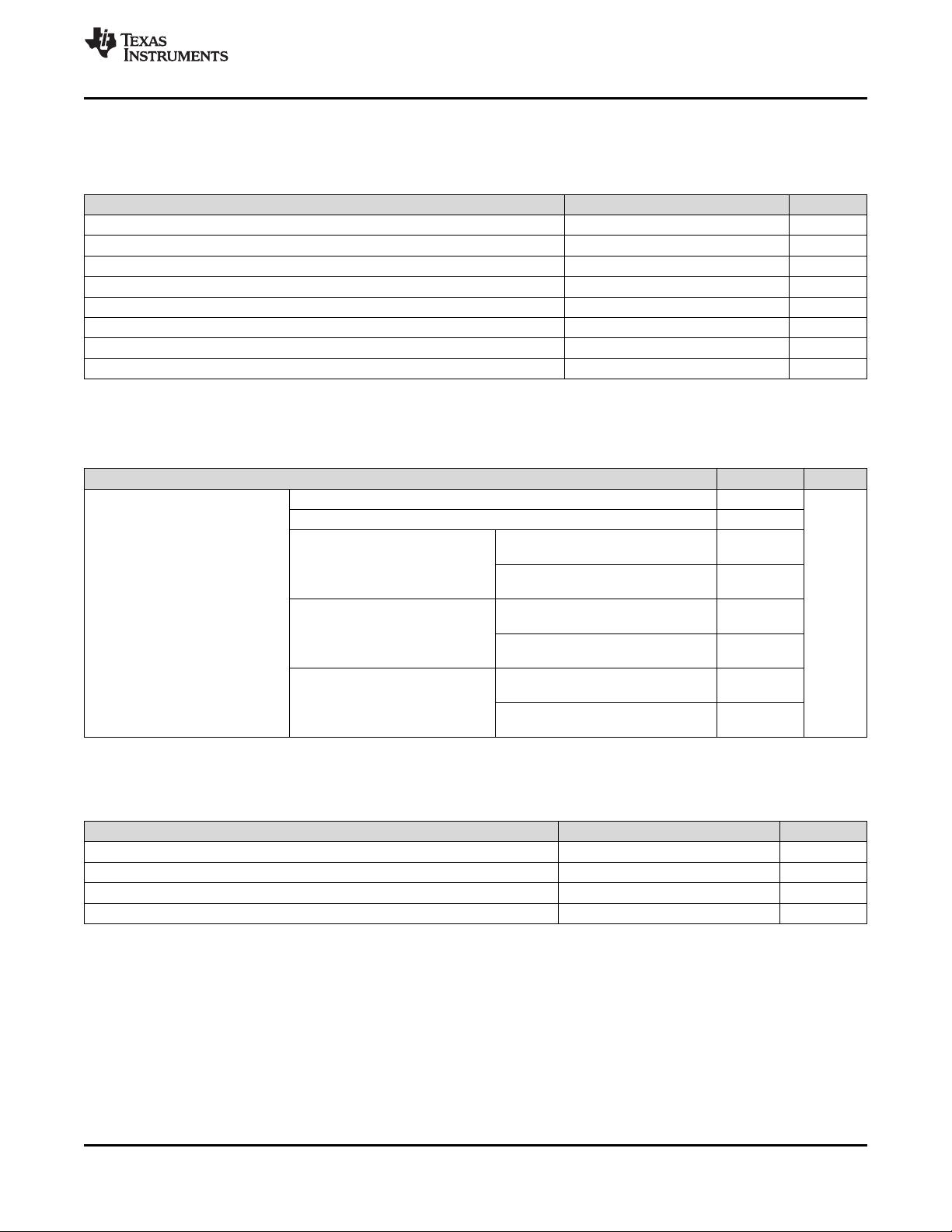

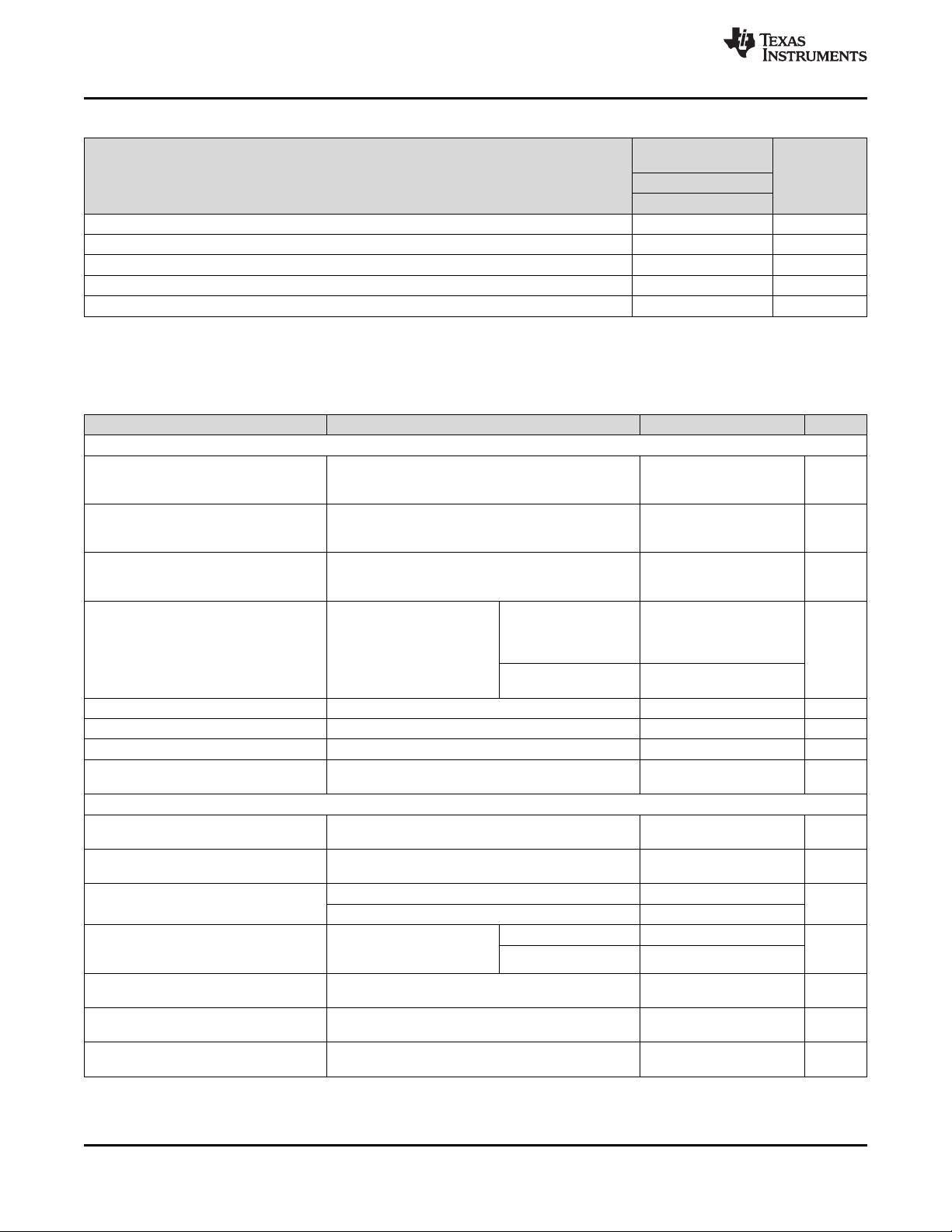

The TI-DS90C124-Q1.pdf is a document that provides detailed information about the FPD-Link serializer and deserializer, specifically the DS90C124 deserializer and DS90C241 serializer. The DS90C241 serializer is responsible for converting parallel data into a serial stream, while the DS90C124 deserializer performs the reverse operation.

The serializer is equipped with PLL timing and control circuitry, which ensures that the serial data is synchronized with the clock signal. The deserializer also has PLL timing and control capabilities, ensuring that the incoming serial data is properly synchronized with the clock signal. Both the serializer and deserializer have a DC balance encoder/decoder, which helps maintain the DC balance of the data stream.

The communication between the serializer and deserializer is facilitated by a 24-bit data link, with clock recovery and output latch circuitry ensuring that the data is transmitted and received accurately. The input latch in the deserializer converts the serial data stream into parallel data, while the output latch in the serializer converts parallel data into a serial stream.

The data link operates at a clock rate of 100 MHz, with both devices featuring a power-down mode for energy efficiency. The devices also include various control inputs and outputs for configuration and monitoring purposes.

Overall, the DS90C124 and DS90C241 provide a reliable and efficient solution for converting data between parallel and serial formats in high-speed communication applications. With their advanced timing and control features, as well as DC balance encoding/decoding capabilities, these devices are essential components for ensuring accurate data transmission in modern electronic systems.

2023-02-08 上传

2023-02-07 上传

2023-02-07 上传

2023-02-08 上传

2023-02-07 上传

2023-02-07 上传

2023-02-05 上传

2023-02-08 上传

2023-02-08 上传

不觉明了

- 粉丝: 3859

- 资源: 5759

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫