基于测频原理的4位数字频率计设计

需积分: 25 171 浏览量

更新于2024-07-25

收藏 138KB PPT 举报

"该资源是一份关于数字频率计的PPT文档,主要讲解了采用测频原理设计一个4位十进制数字显示的数字频率计,测量范围为1~9999KHz。文档详细介绍了测频法的测量原理、系统组成以及FPGA在其中的应用,并提供了VHDL程序的代码示例。"

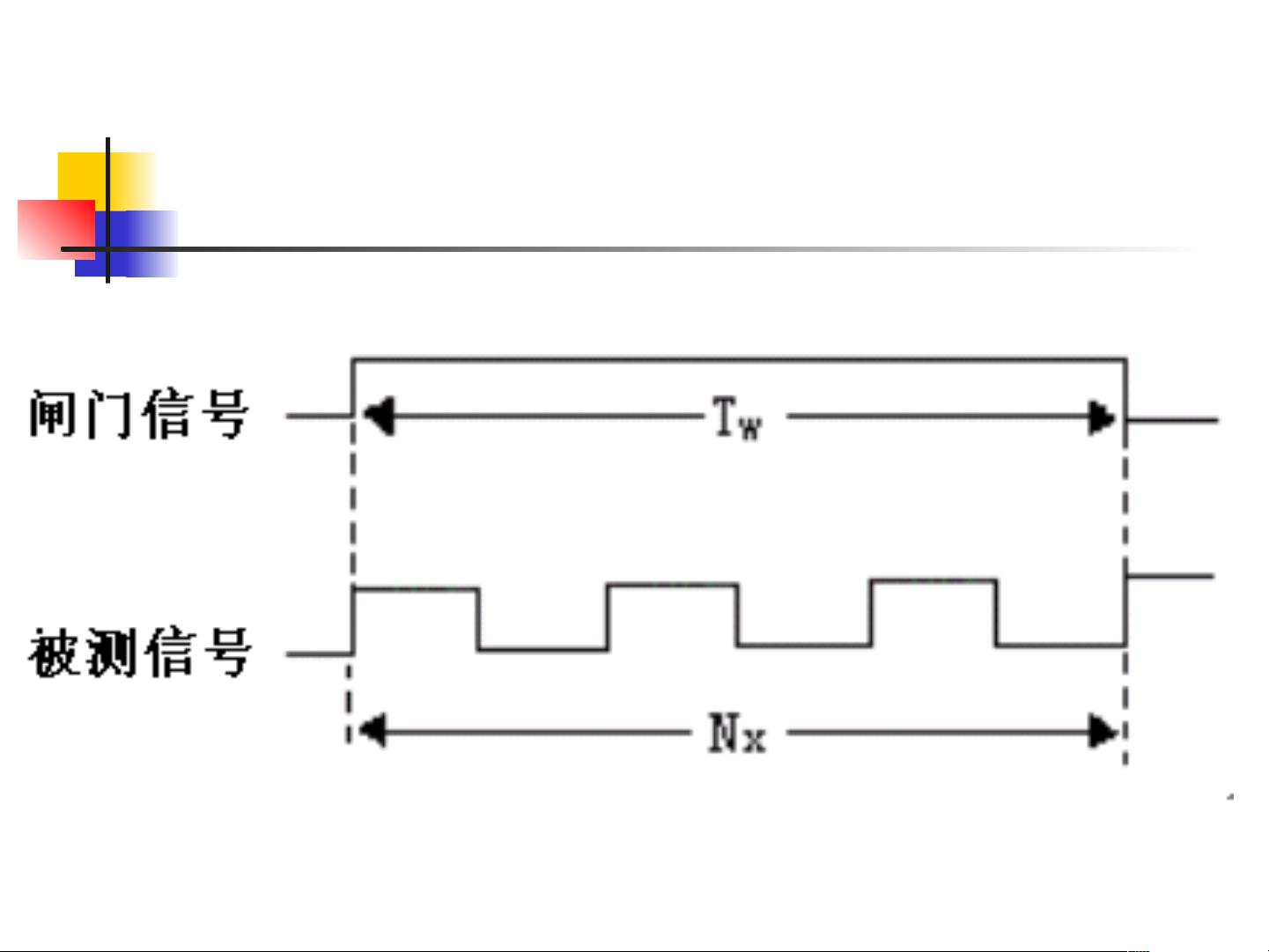

数字频率计是一种用于测量信号频率的电子设备,它基于测频法来工作。测频法的测量原理是,在固定的闸门时间Tw内,通过计数器记录被测信号的周期数(或脉冲个数)Nx,然后将这个数量除以闸门时间,即可得到被测信号的频率fx= Nx/Tw。由于这种计数方式可能会有±1个字的误差,因此,测试精度受到计数器记录的数值Nx的影响。

数字频率计的系统通常由三个主要部分构成:输入模块、FPGA模块和显示模块。输入模块包括基准时钟、复位信号和被测信号。基准时钟提供稳定的时钟源,复位信号用于初始化系统,而被测信号是需要测量频率的输入信号。FPGA模块是核心,它包含了分频器、7位十进制计数器、数据处理单元和动态译码器。分频器将基准时钟分频,生成闸门信号,该信号控制7位十进制计数器的工作。计数器在闸门时间内累计被测信号的脉冲,数据处理单元取出高4位有效数据,这些数据经过动态译码后在数码管上显示,以形成4位十进制的频率读数。显示模块则使用数码管将结果显示出来,小数点位置指示的是千位,即表示频率单位为KHz。

在VHDL程序中,定义了一个实体名为"plj"的模块,它接收复位信号、系统时钟和被测信号作为输入,输出八段码和数码管位选信号。程序使用了标准逻辑库和逻辑运算符,并实现了一个能够根据7位十进制计数结果自动选择高4位有效数据并进行动态显示的功能。通过这种方式,频率计可以有效地显示测量到的频率值。

数字频率计通过精确的计数和时间测量,实现了对各种信号频率的准确测定,其设计和实现涉及到了数字逻辑、FPGA编程以及显示技术等多个领域。VHDL程序则提供了实现这一功能的具体代码框架,使得硬件描述语言在系统设计中的应用得以体现。

点击了解资源详情

1938 浏览量

点击了解资源详情

111 浏览量

167 浏览量

2025-04-03 上传

2025-04-03 上传

2025-04-03 上传

阿甲哥哥

- 粉丝: 0

最新资源

- AntraxCore:下一代HTML技术核心

- 批量提取CAD块属性至Excel的免费软件

- .net/C#/VB动态连接库反编译工具的使用介绍

- 官方Gson 2.7版本jar包下载指南

- 单片机实现马达PWM控制技术研究

- Windows系统安全防护:木马清道夫工具介绍

- 专业修图软件Affinity Photo中文版发布

- 蒸汽服务器主程序:管理与优化技巧

- Linux内核2.6.22版本sbull块设备源码分析

- 远程访问USB设备技术:FabulaTech USB over Network v4.5.3新特性解析

- 高效数据导出利器:SQLULDR快速导出工具

- Linux驱动开发入门指南与源码实践

- DFB转XLS转换工具:批量文件处理新方案

- 探索P2P视频即时通讯控件:源码与测试程序

- Python实践教程:212Factory特斯拉模拟项目

- 实现优先级CPU调度算法的设计与实验