HD74LS138P:3线至8线解码器/_demux器详解

需积分: 9 72 浏览量

更新于2024-09-29

收藏 100KB PDF 举报

HD74LS138是一款集成逻辑门电路,具体来说是三线到八线的译码器/解码器。这款器件的主要功能是根据输入的三位二进制选择线(binary select inputs)和三位使能输入(enable inputs)的状态,将单一线路的数据信号解码成八个输出线中的一个。它的设计巧妙之处在于两个低电平有效的和一个高电平有效的使能输入,这在扩展系统时可以减少对外部门电路或反相器的需求。

对于24线的译码器,它可以直接实现而无需额外的外部反相器,这对于节省电路板空间和简化设计非常有利。然而,对于32线的译码器,仅需一个外部反相器就能满足需求。此外,一个使能输入可以作为数据输入,使得HD74LS138在多路复用(demultiplexing)应用中也非常适用。

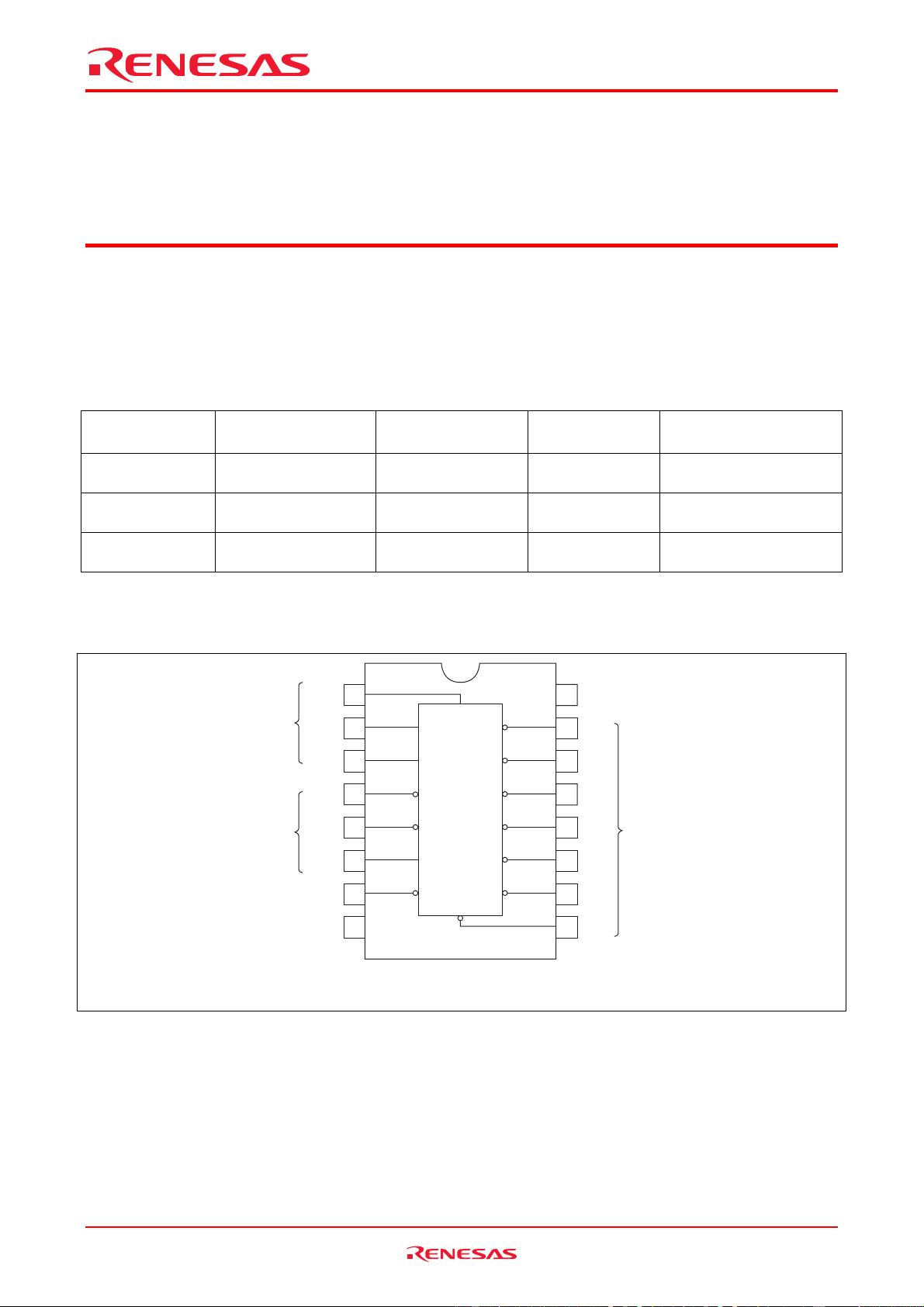

关于封装,该器件提供多种选项,包括DIP-16针双列直插式(DILP-16pin)和SOIC-16针小外形塑料封装(SOP-16pin),如JEITA标准的HD74LS138FPEL和JEDEC标准的HD74LS138RPEL,每种封装都有其特定的包装代码和数量限制,例如PRDP0016AE-B、PRSP0016DH-B和PRSP0016DG-A。购买时应咨询销售办公室确认这些封装的可用性。

在电路布局方面,HD74LS138P的引脚排列图示了电源(VCC)、地(GND)以及各个功能引脚的位置,包括输出信号线Y0至Y7,以及控制信号线如A、B、C等。G1和G2A是两个使能输入,而A、B则是二选一的输入线。整个器件的尺寸紧凑,适合在小型电路板上进行集成,提高了设计的灵活性和效率。

HD74LS138P是一个经济高效且功能强大的译码器,适用于各种需要将单个输入数据扩展到多个输出的电子系统中,尤其适用于对空间和成本敏感的应用场景。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-03-20 上传

2010-11-06 上传

2024-06-19 上传

2010-06-11 上传

2021-10-01 上传

2022-07-04 上传